Триггер с установочными входами (RS-триггер).

Триггер задержки (D-триггер). Т- триггер. JK-триггер

В импульсной и цифровой технике широко используются функциональные узлы, способные сохранять двоичную информацию (состояния «0», «1») после окончания действия входных импульсов. Такие функциональные узлы называют триггерами.

Указанное свойство триггера обусловлено тем, что факторами, воздействующими на его состояния, являются не только внешние управляющие сигналы, но и сигналы самого триггера (сигналы обратной связи).

В триггере два выхода один – прямой, а другой – инверсный. потенциалы на них взаимно инвертированы: лог1 на одном выходе соответствует лог.0 на другом. С приходом переключающих (запускающих) сигналов переход триггера из одного состояния в другое происходит лавинообразно, и потенциалы на выходах меняются на противоположные. В интервале между переключающими сигналами состояние триггера не меняется, т.е. он «запоминает» поступление сигналов, отражая это величиной потенциала на выходе, это дает возможность использовать его как элемент памяти.

При лавинообразных переключениях на выходе триггера формируются прямоугольные импульсы с крутыми фронтами. Это позволяет использовать триггер для формирования прямоугольных импульсов из напряжения другой формы (например, из синусоидального). При двух последовательных переключениях триггера на выходе формируется один импульс, т.е. триггер можно использовать в качестве делителя частоты переключающих сигналов с коэффициентом, равным двум.

В интегральной микросхемотехнике триггеры выполняют либо на основе логических интегральных элементов, либо как завершенный функциональный элемент в виде микросхемы.

Интегральные триггеры характеризуются большим разнообразием. Их отличают функциональный признак, определяющий поведение триггера при воздействии сигнала управления, а также используемый способ управления. По функциональному признаку различают триггеры типов RS, D, Т, JK и др. По способу управления триггеры подразделяют на асинхронные (нетактируемые) и тактируемые (синхронные).

В асинхронных триггерах переключение из одного состояния в другое осуществляется непосредственно с поступлением сигнала на информационный вход. В тактируемых триггерах помимо информационных входов имеется вход тактовых импульсов. Их переключение производится только при наличии разрешающего, тактирующего импульса.

Триггеры применяют при построении более сложных функциональных устройств счетчиков импульсов, регистров и т. д.

RS-триггеры.

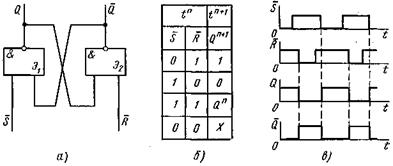

В зависимости от способа управления различают асинхронные и тактируемые RS-триггеры. Асинхронные RS-триггеры являются простейшими, однако они получили широкое распространение в импульсной и цифровой технике. В частности, они служат основой триггеров других типов и требуют для своего построения два двухвходовых логических элемента типа И-НЕ или ИЛИ-НЕ. На рис.3.6,а приведена структурная схема асинхронного триггера на логических элементах И-НЕ. Схема имеет два выхода: Q – прямой выход состояния триггера,  - инверсный выход.

- инверсный выход.

Асинхронный RS-триггер, как и триггер любого другого типа, характеризуется двумя состояниями: логической «1» и логического «0». Состоянию логической «1» соответствует Q=1,  =0; состоянию логического «0» - Q=0,

=0; состоянию логического «0» - Q=0,  =1.

=1.

По информационному входу S производится установка триггера в состояние логической «1», а по информационному входу R — установка (перевод) триггера в исходное состояние логического «0». Этому соответствуют сокращенные обозначения входов и название триггера: S - set (установка), R - reset (возвращение в исходное состояние).

| ||||||||||||||||||

| ||||||||||||||||||

Рис.3.6. Структурная схема асинхронного RS-триггера на логических

элементах И-НЕ (а), его таблица переходов (б) и временные диаграммы (в),

таблица истинности элемента И-НЕ (д)

Особенностью схемы являются инверсные входы  и

и  . Это означает, что для перевода триггера, например, в единичное состояние нужно на вход S подать не единичный, а нулевой сигнал, а в состоянии покоя на входы

. Это означает, что для перевода триггера, например, в единичное состояние нужно на вход S подать не единичный, а нулевой сигнал, а в состоянии покоя на входы  и

и  лог.1. Рассмотрим принцип действия триггера.

лог.1. Рассмотрим принцип действия триггера.

Принцип действия триггера определяется поведением в нем элементов И-НЕ. Он иллюстрируется таблицей переходов триггера (рис.3.6,б), где указаны значения входных сигналов  и

и  в некоторый момент времени tn и состояние триггера (по значению его прямого выхода) в следующий момент времени tn+1 после прихода очередных импульсов.

в некоторый момент времени tn и состояние триггера (по значению его прямого выхода) в следующий момент времени tn+1 после прихода очередных импульсов.

При  =0 и

=0 и  =1 подтверждается предшествующее состояние, если триггер находился в состоянии логической «1», и переход его в состояние «1», если триггер до этого находился в состоянии «0» (первая строка сверху в таблице на рис.3.6,б).

=1 подтверждается предшествующее состояние, если триггер находился в состоянии логической «1», и переход его в состояние «1», если триггер до этого находился в состоянии «0» (первая строка сверху в таблице на рис.3.6,б).

Пусть триггер находился в состоянии логической «1», т.е. Q=1,  =0. Тогда при

=0. Тогда при  =0 и

=0 и  =1 на выходе элемента Э1 будет лог.1 (т.к. вход S – инверсный) и независимо от значения сигнала на втором входе элемента Э1 Q=1. На обоих входах элемента Э2 присутствуют логические «1». Это обеспечивает

=1 на выходе элемента Э1 будет лог.1 (т.к. вход S – инверсный) и независимо от значения сигнала на втором входе элемента Э1 Q=1. На обоих входах элемента Э2 присутствуют логические «1». Это обеспечивает  =0. Таким образом, триггер будет находится в состоянии лог.1

=0. Таким образом, триггер будет находится в состоянии лог.1

Пусть триггер находится в состоянии лог.0, т.е. Q=0,  =1. Тогда при

=1. Тогда при  =0 и

=0 и  =1 на выходе элемента Э1 появится лог.1, т.е. произойдет переключение элемента Э1 в состояние лог.1. Следовательно на левом входе элемента Э2 появится лог.1 и тогда на выходе элемента Э2 появится лог.0 (

=1 на выходе элемента Э1 появится лог.1, т.е. произойдет переключение элемента Э1 в состояние лог.1. Следовательно на левом входе элемента Э2 появится лог.1 и тогда на выходе элемента Э2 появится лог.0 (  =0), т.е. элемент Э2 переключится в состояние лог.0. таким образом произойдет переход триггера из состояния лог.0 в состояние лог.1 (первая строка сверху в таблице на рис.3.6,б).

=0), т.е. элемент Э2 переключится в состояние лог.0. таким образом произойдет переход триггера из состояния лог.0 в состояние лог.1 (первая строка сверху в таблице на рис.3.6,б).

Для его переключения из этого состояния (из состояния «1» (Q=1,  =0,) в состояние «0», Q=0,

=0,) в состояние «0», Q=0,  =1) на входы должна поступить комбинация сигналов

=1) на входы должна поступить комбинация сигналов  =l,

=l,  =0. После чего на выходе Q=0, на входах Э2 будут лог.0, следовательно на выходе

=0. После чего на выходе Q=0, на входах Э2 будут лог.0, следовательно на выходе  =1 (вторая строка сверху в таблице переходов). Положение доказывается аналогичным образом.

=1 (вторая строка сверху в таблице переходов). Положение доказывается аналогичным образом.

Значениям сигналов на входе S=R=1 соответствует сохранение триггером предыдущего состояния (третья строка сверху в таблице переходов). Пусть до появления такой комбинации сигналов на входах в триггере была записана логическая «1» (Q=1,  =0). При наличии S=R=1 имеем на обоих входах элемента Э2 по логической «1». Это обусловливает

=0). При наличии S=R=1 имеем на обоих входах элемента Э2 по логической «1». Это обусловливает  =0. На правом входе элемента Э1 будет логический «0», что дает Q=1.

=0. На правом входе элемента Э1 будет логический «0», что дает Q=1.

При комбинации S=R=0 (последняя строка снизу в таблице переходов) один из входов обоих элементов И-НЕ имеет логический «0». Согласно рис.3.6,в, Q=  =1. Такие значения выходных сигналов триггера не соответствуют ни его состоянию «1» (Q= 1,

=1. Такие значения выходных сигналов триггера не соответствуют ни его состоянию «1» (Q= 1,  =0), ни его состоянию «0» (Q=0,

=0), ни его состоянию «0» (Q=0,  =1). Триггер принимает неопределенное состояние. По указанной причине комбинация сигналов на входе S=R=0 для асинхронного RS-триггера на элементах И-НЕ является запрещенной. Рассмотренной схеме триггера соответствуют временные диаграммы, приведенные на рис.3.6,в. Они построены с учетом таблицы переходов, приведенной на рис.3.6,б.

=1). Триггер принимает неопределенное состояние. По указанной причине комбинация сигналов на входе S=R=0 для асинхронного RS-триггера на элементах И-НЕ является запрещенной. Рассмотренной схеме триггера соответствуют временные диаграммы, приведенные на рис.3.6,в. Они построены с учетом таблицы переходов, приведенной на рис.3.6,б.

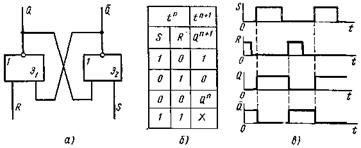

На рис.3.7,а показана структурная схема асинхронного RS-триггера на двухвходовых логических элементах ИЛИ-НЕ. В отличие от предыдущей схемы триггер управляется не инверсными, а прямыми значениями входных сигналов. Работу схемы иллюстрирует таблица переходов, приведенная на рис.3.7,б.

| ||||||||||||||||||

| ||||||||||||||||||

Рис.3.7. Структурная схема асинхронного RS-триггера на логических

элементах ИЛИ-НЕ (а), его таблица переходов (б) и временные

диаграммы (в), таблица истинности элемента ИЛИ-НЕ (д)

Пусть триггер находится в состоянии лог.0 (Q=0,  =1), а на входах действуют сигналы S=0, R=0. Для его переключения в состояние лог.1 Q= 1,

=1), а на входах действуют сигналы S=0, R=0. Для его переключения в состояние лог.1 Q= 1,  =0 подадим на входы комбинацию S=1, R=0. Тогда на выходе элемента Э2 установится лог.0 (

=0 подадим на входы комбинацию S=1, R=0. Тогда на выходе элемента Э2 установится лог.0 (  =0), на обоих входах элемента Э1 будут одновременно присутствовать лог. 0, и на выходе Q установится лог. 1 — триггер переключится в новое состояние (лог.1 Q= 1,

=0), на обоих входах элемента Э1 будут одновременно присутствовать лог. 0, и на выходе Q установится лог. 1 — триггер переключится в новое состояние (лог.1 Q= 1,  =0) (первая строка на рис.3.7,б). Для его переключения из этого состояния на входы должна поступить комбинация S=0, R=1. После чего на выходе Q будет лог. 0, на входах элемента Э2 одновременно окажутся лог. 0 и его выход примет потенциал, соответствующий

=0) (первая строка на рис.3.7,б). Для его переключения из этого состояния на входы должна поступить комбинация S=0, R=1. После чего на выходе Q будет лог. 0, на входах элемента Э2 одновременно окажутся лог. 0 и его выход примет потенциал, соответствующий  =1, т. е. триггер переключится в состояние лог.0 (Q=0,

=1, т. е. триггер переключится в состояние лог.0 (Q=0,  =1) (вторая строка на рис.3.7,б).

=1) (вторая строка на рис.3.7,б).

При S=R=0 в триггере сохраняется предшествующее состояние («0» или «1»). Например, при Q=0 на обоих входах элемента Э2 присутствуют логические «0», что дает Q=1. Сигнал на правом входе элемента Э1 равен единице, вследствие чего (см. рис.3.7,в) в триггере поддерживается состояние Q=0.

Комбинация S=R=1 для схемы триггера на элементах ИЛИ-НЕ является запрещенной ввиду неопределенности его состояния. Для этой комбинации Q=  =0. Схеме триггера соответствуют временные диаграммы, приведенные на рис.3.7,в.

=0. Схеме триггера соответствуют временные диаграммы, приведенные на рис.3.7,в.

Из двух рассмотренных схем асинхронных RS-триггеров триггер на логических элементах И-НЕ нашел большее применение ввиду большей распространенности этих элементов в сериях интегральных микросхем.

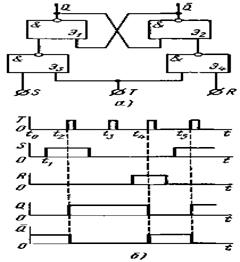

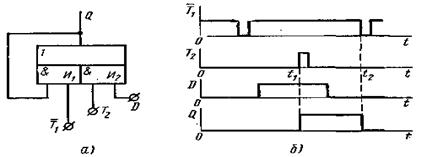

На рис.3.8,а приведена структурная схема тактируемого RS-триггера на элементах И-НЕ. Переключения в тактируемом триггере возможны, как отмечалось, лишь при наличии разрешающего сигнала (импульса тактов), подаваемого на вход Т. Эта особенность схемы связана с применением на входах асинхронного RS-триггера двух управляющих элементов И-НЕ (Э3, Э4). Принцип действия схемы иллюстрируют временные диаграммы, приведенные на рис.3.8,б.

|

Рис.3.8. Структурная схема тактируемого RS-триггера (а)

и его временные диаграммы (б)

При нулевых значениях сигналов на всех трех входах (S=R=Т=0) на выходах элементов Э3, Э4 действует логическая «1». Состояние RS-триггера на элементах Э1, Э2 остается без изменения (интервал времени t0-t1); на рис.3.8,б принято за нулевое. Состояние триггера сохраняется и при S=l, R=Т=0 (интервал времени t1-t2). В момент времени t2 сигналы логической «1» совпадают по входам S и T(S=Т=1, R=0). На выходе элемента Э3 действует логический «0», а на выходе элемента Э4 — логическая «1», что приводит к переключению триггера на элементах Э1, Э2 в состояние «1».

Очередное переключение триггера возможно лишь в момент времени t4, когда R=Т=1,S=0, а также в момент времени t5, когда S=Т=1,R=0. Комбинация S=R=Т=1 в триггере должна быть исключена, так как на выходах элементов Э3, Э4 при этом присутствовал бы одновременно сигнал «0», что, как известно, запрещено для асинхронного RS-триггера на логических элементах И-НЕ. Тактируемые RS-триггеры нашли широкое применение в устройствах цифрового действия для хранения двоичной информации в течение времени, большего ее существования в исходном источнике, например для хранения промежуточной информации, передаваемой от счетчиков импульсов и регистров.

D-триггеры.

D-триггеры имеют один информационный вход. Состоянию логической «1» соответствует единица на входе триггера, а состоянию логического «0» — нулевой уровень входного сигнала. На практике наибольшее применение получили тактируемые (однотактные и двухтактные) D-триггеры. Их обозначение обусловлено свойством сохранять состояние логической «1» после снятия входного сигнала до прихода очередного тактового импульса (delay — задержка). D-триггеры широко используют при построении регистров.

На рис.3.9,а приведена структурная схема однотактного D-триггера, выполненная на основе асинхронного RS-триггера. Временные диаграммы, поясняющие его принцип действия, изображены на рис.3.9,б.

|

Рис.3.9. Структурная схема тактируемого D-триггера (а) и

его временные диаграммы (б)

Предположим, что к моменту прихода входного сигнала D-триггер находился в состоянии логического «0» (Q=О,  =1). В интервале времени t1-t2, когда действует входной сигнал D, состояние триггера не изменяется, так как при этом Т=0 и сигналы на входах элементов Э1,Э2 S=R=1. Действие сигнала Т=1 в момент времени t2 обусловливает на выходе элемента Э3 S=0, а на выходе элемента Э4 R=1. Это приводит к переключению триггера в состояние логической «1» (Q=1,

=1). В интервале времени t1-t2, когда действует входной сигнал D, состояние триггера не изменяется, так как при этом Т=0 и сигналы на входах элементов Э1,Э2 S=R=1. Действие сигнала Т=1 в момент времени t2 обусловливает на выходе элемента Э3 S=0, а на выходе элемента Э4 R=1. Это приводит к переключению триггера в состояние логической «1» (Q=1,  =0). Состояние «1» триггера не изменится до момента времени t4, так как при Т=0 сигналы на входах асинхронного триггера S=R=1. Появление в момент времени t4 сигнала Т=1 дает R=0,S=1 и вызывает переключение триггера в состояние логического «0». Принцип действия двухтактных D-триггеров подобен однотактным. Отличие заключается в том, что запись информации в них производится с участием одной последовательности тактовых импульсов, а считывание — с участием другой последовательности тактовых импульсов. Обе последовательности тактовых импульсов имеют фазовый сдвиг в 180°.

=0). Состояние «1» триггера не изменится до момента времени t4, так как при Т=0 сигналы на входах асинхронного триггера S=R=1. Появление в момент времени t4 сигнала Т=1 дает R=0,S=1 и вызывает переключение триггера в состояние логического «0». Принцип действия двухтактных D-триггеров подобен однотактным. Отличие заключается в том, что запись информации в них производится с участием одной последовательности тактовых импульсов, а считывание — с участием другой последовательности тактовых импульсов. Обе последовательности тактовых импульсов имеют фазовый сдвиг в 180°.

Двухтактные D-триггеры просто реализуются на комбинированных логических элементах.

На рис.3.10,а приведена структурная схема однофазного (имеющего один выход) двухтактного D-триггера на элементе 2И-ИЛИ. Запись единицы в триггере осуществляется при одновременном действии сигналов T2,D на входах элемента И2, а считывание производится по входу Т1 элемента И1. Процессы в схеме иллюстрируют временные диаграммы рис.3.10,б.

До момента времени t1 триггер находится в состоянии «0». При наличии в момент времени t1 сигналов на обоих входах элемента И2 происходит изменение состояния триггера (Q=1). Это состояние поддерживается в триггере до момента времени t2 логической «1» на обоих входах элемента И1.

В момент времени t2 Т1 = 0, на выходе элемента И1, действует логический «0», что вызывает переход триггера в исходное нулевое состояние.

|

Рис.3.10. Структурная схема однофазного двухтактного D-триггера (а)

и его временные диаграммы (б)

Т-триггер.

Характерным свойством Т-триггера является его переключение в противоположное состояние с приходом каждого очередного входного импульса. Ввиду широкого применения в счетчиках импульсов его часто называют триггером со счетным запуском.

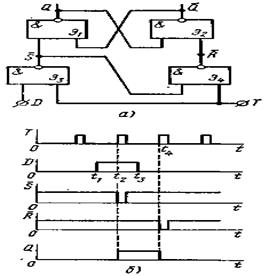

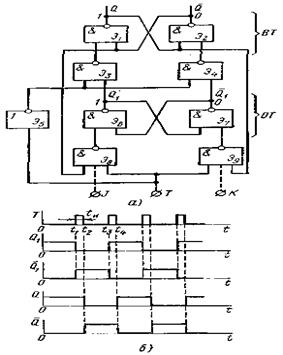

Триггеры Т-типа выполняются на базе двух асинхронных RS-триггеров (MS-схема), один из которых называют основным (master — основной), а другой — вспомогательным (slave — вспомогательный) (триггеры ОТ и ВТ на рис.3.11,а).

|

Рис.3.11. Структурная схема Т-триггера (а) и его временные диаграммы (б)

По MS-схеме реализуются несколько вариантов Т-триггера. Особенностью рассматриваемой структурной схемы является наличие в ней дополнительного инвертора (элемент Э5), управляющего ВТ. В связи с этим ее называют часто схемой с инвертором.

Последовательность переключения асинхронных RS-триггеров, входящих в T-триггер, такая. На этапе фронта входного импульса переключается основной триггер, а по окончании длительности tи входного импульса (на этапе среза) — вспомогательный триггер (рис.3.11,6). Указанная особенность отражается в другом названии схемы — триггер с внутренней задержкой(Тt).

Режим счетного запуска T-триггера определяет указанные ниже особенности, учитываемые при его построении. В схеме должны быть созданы условия для сохранения нового состояния после переключения триггера входным импульсом. При этом должна обеспечиваться необходимая направленность переключения: если триггер находится в состоянии «1», то входной импульс переводит его в состояние «0», и наоборот. Предположим, что после переключения оба триггера установлены в состояние «1». Состояние «1» основного триггера поддерживается единичными сигналами с выходов элементов Э8, Э9. Значения «1»на выходах этих элементов создаются ввиду того, что сигнал на одном из их входов Т=0. Состояние «1» вспомогательного триггера обусловливается тем, что при Т=0 на обоих входах элемента Э3 действует логическая «1», а на выходе элемента Э3 — логический «0». Избирательность переключения Т-триггера достигается наличием связей элементов Э8, Э9 с выходами вспомогательного триггера. Если до прихода очередного входного импульса Т в триггере записана «1», то по цепям обратных связей на входе элемента Э9 будет логическая «1», а на выходе элемента Э8 — логический «0». При поступлении входного импульса Т элемент Э9 переходит в состояние «0», вызывая переключение в нулевое состояние основного триггера, а после окончания входного импульса в состояние «0» переключается и вспомогательный триггер. Принцип действия схемы поясняют временные диаграммы, приведенные на рис.3.11,б. К моменту времени t1, триггеры ОТ и ВТ находятся в состоянии «1». В момент времени t1 T=1 и триггер ОТ переходит в состояние «0», однако при этом на выходе элемента Э5 действует логический «0», а на выходах элементов Э3 и Э4 — по логической «1». Таким образом, на этапе действия входного импульса состояние ВТ не изменяется. В момент времени t2 Т=0 и на выходе элемента Э5 действует логическая «1». На обоих входах элемента Э4 присутствует «1», сигнал на выходе элемента Э4 становится равным нулю, что вызывает переключение в состояние «0» и вспомогательного триггера.

С момента времени t3 действие входного импульса направлено на переключение триггера в состояние «1». Вначале (в момент времени t3) в состояние «1» переключается триггер ОТ, а затем (в момент времени t4) и триггер ВТ. В последующем процессы в схеме повторяются.

JK-триггер.

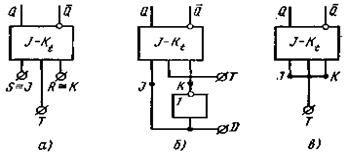

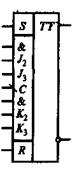

JK-триггер получают на основе T-триггера (рис.3.11,а) путем использования в его входных цепях трехвходовых элементов И-НЕ, позволяющих иметь два дополнительных входа J и К (пунктирные линии на рис.3.11,а). Наличие двух дополнительных входов расширяет функциональные возможности триггера, в связи с чем JK-триггер называют универсальным. При соответствующем подключении входов JК-триггер, в частности, может выполнять функции RS, D- и T-триггеров (рис.3.12,а-в) JK.

JK-триггер, так же как и все типы триггеров, получаемые на его основе, является триггером с внутренней задержкой: в момент действия импульса Т информация записывается в основной триггер, а после его окончания состояние основного триггера передается во вспомогательный. Наличие в работе схемы внутренней временной задержки, определяемой длительностью тактовых импульсов, часто отражается символом «t» в обозначении JK триггера и триггеров, выполненных на его основе: JKt, R-St, Dt, Tt.

Рис.3.12. Схемы триггеров RS (a), D (б), T (в),

реализуемых на основе JK-триггера

RSt и Dt триггеры являются тактируемыми (рис.3.12,а,б); RSt-триггер (рис.3.12,а) получают подачей на вход J сигнала S; а на вход К — сигнала R; Dt-триггер создается введением инвертора в цепь входа К (рис.3.12,б). Триггер со счетным запуском (Тt триггер) реализуется подключением входов J и К к входу Т. Условные изображения триггеров представлено на рис.3.13.

а б в г д

е ж з

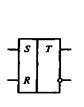

Рис. 3.13. Условные обозначения триггеров: а) RS; б) RS-триггер с инверсными входами; в) тактируемый RS-триггер (RSC-триггер); г) двухступенчатый тактируемый RS-триггер с перепадом 1/0; д) двухступенчатый тактируемый RS-триггер с перепадом 0/1; е) двухступенчатый RS-триггер с асинхронными входами; ж) двухтактный D-триггер с перепадом 1/0; з) JK-триггер с 3 объединенными конъюнкцией J-входами, с 3 объединенными конъюнкцией K-входами и с входами S,R асинхронной установки.

Счетчики импульсов

3.3.1. Суммирующий счётчик.

Подсчет числа импульсов является наиболее распространенной операцией в устройствах цифровой обработки информации. Повышенный интерес к таким устройствам объясняется их высокой точностью, возможностью применения регистрирующих приборов с непосредственным цифровым представлением результата, а также возможностью осуществления связи с ЭВМ. В устройствах цифровой обработки информации измеряемый параметр (угол поворота, перемещение, скорость, частота, время, температура и т. д.) преобразуется в импульсы напряжения, число которых в соответствующем масштабе характеризует значение данного параметра. Эти импульсы подсчитываются счетчиками импульсов и выражаются в виде цифр.

По целевому назначению счетчики подразделяют на: простые и реверсивные. Простые счетчики, в свою очередь, подразделяют на: суммирующие и вычитающие.

Суммирующий счетчик предназначен для выполнения счета в прямом направлении, т.е. для сложения. С приходом очередного счетного импульса на вход счетчика его показание увеличивается на единицу.

Вычитающий счетчик служит для осуществления счета в обратном направлении, т.е. для вычитания. Каждый счетный импульс, поступающий на вход вычитающего счетчика, уменьшает его показание на единицу.

Реверсивные счетчики предназначены для выполнения операции счета как в прямом, так и в обратном направлении, т.е. они могут работать в режиме сложения и вычитания.

Основными показателями счетчиков являются модуль счета (коэффициент счета К) и быстродействие.

Коэффициент счета определяет число импульсов, которое может быть сосчитано счетчиком.

Быстродействие счетчика характеризуется максимальной частотой fcч следования счетных импульсов и связанным с ней временем tУст установки счетчика. Величина tуст определяет максимальное время протекания переходных процессов во всех разрядах счетчика с поступлением на вход очередного счетного импульса.

Счетчики импульсов выполняются на основе триггеров. Счет числа поступающих импульсов производится с использованием двоичной системы счисления

Двоичные суммирующие счетчики с непосредственной связью. Двоичные счетчики производят счет поступающих импульсов в двоичной системе счисления. Основным узлом двоичного счетчика (служащим также его разрядом) является триггер со счетным запуском, осуществляющий подсчет импульсов по модулю 2.

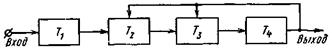

Многоразрядные двоичные суммирующие счетчики с непосредственной связью выполняются путем последовательного соединения счетных триггеров. Счетные импульсы подаются на счетный вход первого триггера. Счетные входы последующих триггеров связаны непосредственно с прямыми выходами предыдущих триггеров: вход второго триггера соединен с выходом первого триггера, вход третьего — с выходом второго и т. д.

Принцип действия двоичного счетчика с непосредственной связью рассмотрим на примере четырехразрядного счетчика, показанного на рис.3.14,а. Схема выполнена на счетных Tt триггерах с внутренней задержкой. Работу схемы иллюстрируют временные диаграммы, приведенные на рис. 3.14.

Рис.3.14. Схема двоичного счетчика (а) и его временные диаграммы (б)

Перед поступлением счетных импульсов все разряды счетчика устанавливаются в состояние «0» (Q1=Q2=Q3=Q4=0) подачей импульса на вход «Установка нуля». При поступлении первого счетного импульса (рис.3.14,б) первый разряд подготавливается к переключению в противоположное состояние и после окончания действия входного импульса переходит в состояние Q=1. В счетчик записывается число 1. Уровень 1 с выхода Q1 воздействует на счетный вход второго разряда, подготавливая его к переключению. По окончании второго счетного импульса первый разряд счетчика переходит в состояние «0», а второй разряд переключается в состояние «1». В счетчике записывается число 2 с кодом 0010.

Подобным образом осуществляется работа схемы с приходом последующих импульсов. Первый разряд счетчика, как видно из рис.3.14,б, переключается с приходом каждого входного импульса, второй разряд — каждого второго, третий — каждого четвертого, а четвертый разряд срабатывает на каждый восьмой счетный импульс.

По окончании 15-го импульса все разряды счетчика устанавливаются в состояние «1» (рис.3.14,б), а 16-й импульс переключает первый разряд счетчика в состояние «0». Уровень Q1=0 переводит второй разряд счетчика в состояние Q2=0, что, в свою очередь, вызывает Q3=0, а затем и Q4=0, т.е. счетчик переходит в исходное состояние.

В соответствии с рис.3.14,б установка в исходное состояние «0» двух последовательно включенных триггеров (T1 и T2) осуществляется четвертым счетным импульсом, трех триггеров (Т1-Т3) — восьмым и четырех триггеров (T1-Т4) — 16-м счетным импульсом. Из этого следует, что модуль счета двухразрядного, трехразрядного и четырехразрядного двоичных счетчиков равен соответственно 4, 8 и 16. Модуль счета двоичного счетчика находят из соотношения Kcч =2N , где N — число разрядов счетчика.

В процессе работы двоичного счетчика частота следования импульсов на выходе каждого последующего триггера уменьшается вдвое по сравнению с частотой его входных импульсов (рис.3.14, б). Это свойство схемы используют для построения делителей частоты. При использовании схемы в качестве делителя частоты входной сигнал подают на счетный вход первого триггера, а выходной снимают с последнего триггера. Выходная и входная частоты связаны соотношением

fвыx = Iвх/Kсч

Максимальное время установки tустmax в двоичных счетчиках с непосредственной связью характеризуется суммарной задержкой в последовательной передаче информации от младшего к старшему разряду счетчика. Другими словами, параметр tустmax определяется временем перехода счетчика из кода 2N-1 в код 00...0. Его находят из соотношения

tустmax=Ntз т.,

где tз.т - задержка переключения Тt триггера после окончания счетного импульса.

Время установки возрастает с увеличением числа разрядов, что сказывается на быстродействии счетчика. Максимальная частота следования счетных импульсов ограничивается величиной

fвх=1/(tи + tуст max).

Счетчики с коэффициентом счета Ксч  2N. B рассмотренных двоичных счетчиках коэффициент счета связан определенной зависимостью с числом разрядов (триггеров) счетчика Ксч = 2N и может быть равен. 2, 4, 8, 16, 32 и т.д. Однако на практике часто возникает необходимость в счетчиках, коэффициент счета которых не соответствует указанным значениям. В частности, требуются счетчики с коэффициентом счета Ксч=3, 10 и т. д., т. е. счетчики, принимающие в процессе работы соответственно 3, 10 состояний и т. д.

2N. B рассмотренных двоичных счетчиках коэффициент счета связан определенной зависимостью с числом разрядов (триггеров) счетчика Ксч = 2N и может быть равен. 2, 4, 8, 16, 32 и т.д. Однако на практике часто возникает необходимость в счетчиках, коэффициент счета которых не соответствует указанным значениям. В частности, требуются счетчики с коэффициентом счета Ксч=3, 10 и т. д., т. е. счетчики, принимающие в процессе работы соответственно 3, 10 состояний и т. д.

Такие счетчики выполняются на основе двоичных счетчиков. Общий принцип их построения основывается на исключении у счетчика с Ксч=2N соответствующего числа «избыточных» состояний. Число избыточных (запрещенных) состояний s определяется разностью:

s =2N-KCЧ,

где 2N - количество состояний двоичного счетчика; Ксч - требуемый коэффициент счета.

Число триггеров синтезированного счетчика выбирают по минимуму величины s. Например, при построении счетчика с Kсч=3 на двух триггерах и счетчика с Ксч=10 на четырех триггерах следует исключить соответственно 1 и 6 состояний.

Способы построения счетчиков с коэффициентом счета Kсч  2N достаточно разнообразны. Наибольшее распространение получили способ принудительной установки в состояние «0» всех разрядов двоичного счетчика и способ принудительного насчета. По первому способу реализуются счетчики с естественным порядком счета, по второму — счетчики с принудительным насчетом.

2N достаточно разнообразны. Наибольшее распространение получили способ принудительной установки в состояние «0» всех разрядов двоичного счетчика и способ принудительного насчета. По первому способу реализуются счетчики с естественным порядком счета, по второму — счетчики с принудительным насчетом.

В счетчиках с естественным порядком счета порядок счета такой же, как в двоичных счетчиках. Отличие заключается в том, что путем введения дополнительных связей счет заканчивается раньше значения 2N. Так, у счетчика с Ксч=10 переход разрядов в состояние «0» будет происходить с приходом не 16-го, а 10-го счетного импульса («система 16—6»).

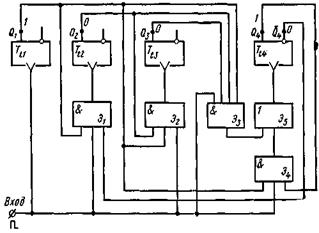

Пример построения счетчика с естественным порядком счета при Ксч=10 приведен на рис.3.15. Счетчик содержит четыре Тt-триггера и пять элементов Э1 — Э5, управляющих переключением триггеров Тt2 — Tt4.

|

Рис.3.15. Схема декадного счетчика с естественным порядком счета

Запуск триггера Тt1 осуществляется непосредственно счетными импульсами, а запуск триггеров Tt2 - Тt4 — счетными импульсами, проходящими через элементы Э1 -Э4.

До наступления 10-го счетного импульса последовательность переключения триггеров та же, что и у двоичного счетчика (табл.3.3).

Действительно, к приходу счетного импульса на один из входов элементов Э1 -Э4 подается логический «0» с выхода Q1=0 и все они закрыты для пропускания первого счетного импульса на входы Тt2 - Тt4. Первый счетный импульс переключает только триггер Тt1 первого разряда (см. табл.3.3). К приходу второго счетного импульса подготовлен к пропусканию счетного импульса элемент Э1 (на левом его входе присутствует «1» с выхода Q1=1, а на правом - «1» с выхода Q4=1). Элемент Э2 закрыт по входу Q2=0, элемент Э3 - по входам Q2=Q3=0, а элемент Э4 - по входу Q4=0. Второй счетный импульс переключает в состояние «0» триггер Tt1 и в состояние «1» триггер Тt2. К приходу третьего счетного импульса элементы Э1-Э4 закрыты по одному из их входов (Q1=0) Третий счетный импульс переключает только триггер Тt1. В соответствии с табл.3.3 происходит переключение триггеров разрядов с приходом и последующих четвертого — девятого счетных импульсов.

Таблица 3.3

Последовательность переключения триггеров

| Число входных импульсов | Состояние триггеров счётчиков | |||

| Т4 | Т3 | Т2 | Т1 | |

После девятого счетного импульса триггеры счетчика принимают следующие состояния: Q1=Q4=1, Q2=Q3=0. Сигналы Q2=Q3=Q4=0 закрывают элементы Э1, Э2, Э3, а сигнал Q4=1 подготавливает элемент Э4 к отпиранию при поступлении 10-го счетного импульса. Поступающий 10-й счетный импульс переводит триггеры Тt1 и Tt4 в состояние «0», обеспечивая нулевое исходное состояние всех разрядов счетчика.

В счетчиках с принудительным насчетом исключение избыточных состояний двоичного счетчика достигается путем принудительной установки отдельных его разрядов в состояние «1» в процессе счета.

Принудительный насчет осуществляется введением обратных связей со старших разрядов двоичного счетчика в младшие, благодаря чему соответствующие младшие разряды вне очереди переключаются в состояние «1».

Вследствие принудительного насчета показания рассматриваемых счетчиков не соответствуют двоичной системе счисления. По этой причине их относят к классу счетчиков с «произвольным» порядком счета.

Способ реализации счетчиков с принудительным насчетом в процессе счета покажем на примере структурной схемы счетчика с Kсч=10 (рис.3.16). Схема состоит из четырех триггеров и цепей обратных связей с выхода четвертого разряда на запись «1» во второй и третий разряды.

|

Рис.3.16. Структурная схема декадного счетчика с

принудительным насчетом

До записи «1» в четвертый разряд, т.е. до прихода восьмого счетного импульса, счетчик работает как двоичный. С приходом восьмого счетного импульса «1» записывается в триггер T4 с осуществлением обратной связи на запись «1» во вторую и третью ячейки. Таким образом, после восьмого счетного импульса вследствие принудительного насчета в счетчик записывается число 8+6=14. Девятый счетный импульс устанавливает «1» в триггере T1, а 10-й счетный импульс возвращает счетчик в исходное нулевое состояние.

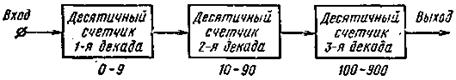

Счетчики с Kсч=10 называют десятичными или декадными. Они нашли широкое применение для регистрации числа импульсов с последующим визуальным отображением результата. Десятичные счетчики часто включают последовательно (рис.3.17).

Последовательное соединение двух схем десятичного счета дает пересчет на 100, трех — на 1000 и т. д. Первая декада производит счет единиц входных импульсов от 0 до 9. Десятый импульс устанавливает разряды первой декады состояние «0», а формируемый ею на выходе импульс записывает «1» во вторую декаду, что соответствует числу 10. Вторая декада считает десятки (от 10 до 90), третья — сотни (от 100 до 900) и т, д.

|

Рис. 3.17. Последовательное соединение декадных счетчиков