Общий принцип работы однонаправленного буфера типа FIFO

МГТУ МИРЭА

==============================================================

Факультет: филиал МГТУ МИРЭА в г. Фрязино

Кафедра общенаучных дисциплин

КУРСОВОЙ ПРОЕКТ

По дисциплине

« Схемотехника ЭВМ »

Тема курсовой работы «Проектирование FIFO»

Студент группы ИФБ-1-10

Руководитель курсовой работы

доцент кафедры ОНД, к.п.н. Исмагилова Е.И.

Рецензент

старший преподаватель кафедры ОНД Николаева Е.Л.

| Работа представлена к защите | «___»__________201__г. | ____________________ |

| «Допущен к защите» | «___»__________201__г. | _____________________ |

Фрязино 2012г.

| Содержание | стр | |||

| Постановка задачи …………………………….………..………………. | ||||

| Введение………………………………………….……………….……... | ||||

| Общий принцип работы однонаправленного буфера типа FIFO.……. | ||||

| Проектирование буфера FIFO ……..…………………………….....…... | ||||

| 4.1 | Схема электрическая структурная...……...………..…………… | |||

| 4.2 | Построение блока регистровой памяти………………………… | |||

| 4.2.1 | Увеличение числа разрядов……………...……….………..…… | |||

| 4.2.2 | Увеличение числа слов …………………………………...……. | |||

| 4.2.3 | Функциональная схема блока регистровой памяти…..……….. | |||

| 4.3 | Построение дешифратора ……………………………………… | |||

| 4.4 | Построение компаратора……………………………………..…. | |||

| Параметры используемых микросхем………….……………………… | ||||

| 5.1 | Регистр ……….…………………………………………………… | |||

| 5.2 | Счётчик …….……………………………………………………... | |||

| 5.3 | Триггер ……………………………………………………………. | |||

| 5.4 | Логические элементы И………………..………………………… | |||

| 5.6 | Логический элемент НЕ ……..…………………………………… | |||

| 5.7 | Логический элемент исключающее ИЛИ ……...………………... | |||

| Принципиальная схема устройства | ||||

| 6.1 | Перечень элементов | |||

| Расчёт параметров устройства | ||||

| 7.1 | Токи и потенциалы | |||

| 7.2 | Нагрузка. | |||

| 7.3 | Потребляемая мощность | |||

| Литература………………………..…..……………………………… | ||||

Постановка задачи

Разработать принципиальную схему буфера FIFO 8сл.×8р. на элементах серии К1533. Регистровую память разработать на основе микросхемы КР1533ИР32.

Введение

Важнейшим применением микросхем оперативной памяти является организация разнообразных информационных буферов, то есть буферной памяти для промежуточного хранения данных, передаваемых между двумя устройствами или системами. Суть информационного буфера состоит в следующем: передающее устройство записывает передаваемые данные в буфер, а принимающее устройство читает принимаемые данные из буфера (рис. 1).

Рис. 1 Включение буферной памяти

Такое промежуточное хранение позволяет лучше скоординировать работу устройств, участвующих в обмене данными, повысить их независимость друг от друга, согласовать скорости передачи и приёма данных.

Главное отличие буферной памяти от памяти для временного хранения информации состоит в том, что к информационному буферу всегда имеют доступ не одно внешнее устройство, а два (или даже более).

Информационные буферы могут обеспечивать периодический или непрерывный обмен между устройствами. Примером буфера с непрерывным режимом обмена может служить контроллер видеомонитора.

Информационные буферы с периодическим режимом обмена могут быть организованы по типу FIFO или по типу LIFO. В случае FIFO массив данных читается из памяти одним устройством в том же порядке, в каком он был записан в память другим устройством. В случае информационного буфера LIFO массив данных читается из памяти в порядке, противоположном тому, в котором он был записан в память.

Общий принцип работы однонаправленного буфера типа FIFO

Для организации обычной очерёдности служит буфер типа очередь, или буфер FIFO (first in — first out — первым вошёл, первым вышел, читается «фифо»). Необходимость в таком буфере возникает, когда источник данных поставляет приёмнику слова, распределённые во времени нерегулярно, причём интервалы времени между некоторыми словами могут быть меньше, чем время, необходимое приёмнику для обработки одного слова. Если потери информации недопустимы, то между источником и приёмником включается буфер FIFO, в котором хранится очередь слов, ожидающих обработки.

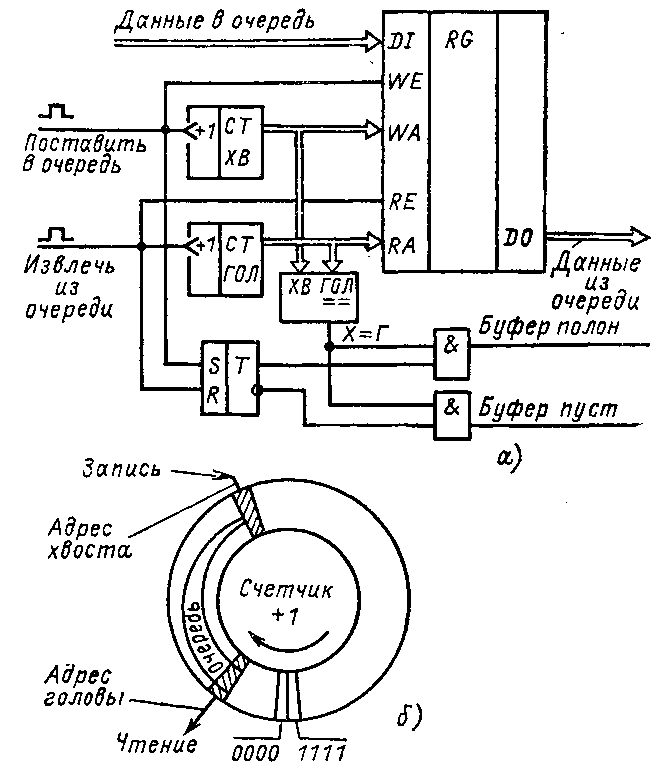

Схема буфера типа «очередь», построенного на основе регистровой памяти, показана на рис. 2,а. На рис. 2,б набор регистров памяти, т. е. адреса памяти показаны в виде кольца. Часть регистров занята очередью, остальные ‑ свободный резерв на случай её увеличения. Адрес записи при постановке в очередь задаётся счётчиком хвоста очереди СТХВ. Сигнал «Поставить в очередь», поступая на вход WE разрешения записи, записывает поступившие по входной шине DI данные в тот регистр памяти, номер которого хранится в СТХВ. По срезу сигнала «Поставить в очередь» выходной код счётчика хвоста увеличивается на 1, подготавливая адрес записи для очередного сигнала «Поставить в очередь».

При поступлении сигнала «Извлечь из очереди» на выходной шине DO появляется слово, хранящееся в том регистре памяти, номер которого задан кодом счётчика головы очереди СТГОЛ. По срезу сигнала выходной код счётчика увеличится на 1, подготовив для выдачи следующее слово, ставшее теперь первым в очереди. Переполнение счётчика хвоста очереди осложнений не вызовет, поскольку после максимально возможного кода счётчика ВСЕ ЕДИНИЦЫ в нем автоматически появится код ВСЕ НУЛИ. Очередь в своём кольце просто переползёт хвостом через нулевую отметку счётчика. Так же со временем переползёт и голова. В процессе нормальной работы очередь двигается в кольце значений адресов по часовой стрелке, хвостом вперёд, удлиняясь или укорачиваясь в соответствии с флюктуациями активности передатчика. Перед началом работы оба счётчика сбрасываются в нуль.

а — функциональная схема; б — диаграмма использования адресов

Рис. 2. Буфер типа «очередь» (буфер FIFO):

Схема буфера FIFO должна сигнализировать о двух особых ситуациях. Первая — буфер полон, тогда в него нельзя больше записывать, и нужно приостановить передатчик. Вторая — буфер пуст, тогда из него нельзя брать данные, и нужно приостановить приёмник.

Обе ситуации имеют общий признак: равенство показаний обоих счётчиков после исчезновения входного сигнала. Этот признак выявляет компаратор. Если счётчики стали равны после очередного извлечения из очереди, то это значит, что очередь иссякла, буфер пуст. Если они стали равны после очередной постановки в очередь, то буфер полон. Характер последнего обращения к буферу запоминается в RS-триггере. Сигналы, информирующие устройство управления об особых состояниях буфера, получаются как конъюнкции того или иного состояния триггера и признака равенства показаний счётчиков головы и хвоста.