Принцип действия процессора

Процессор – важнейший элемент ЭВМ, поэтому производством процессоров занимается большое число фирм. Наиболее массовое распространение в настоящее время получили процессоры, произведенные фирмой Intel (США).

По конструктивному признаку все процессоры делятся на разрядно-модульные (собираемые из несколько микросхем) и однокристальные (они изготавливаются в виде одной микросхемы, на одной подножке, на одном кристалле).Однокристальные процессоры в настоящее время получили наибольшее распространение. По способу представления команд (иногда говорят инструкций) все микропроцессоры можно разделить на две группы:

- процессоры типа CISC (Complex Instruction Set Computing) с полным набором команд;

- процессоры типа RISC (Redused Instruction Set Computing) с сокращенным набором команд. Эти процессоры нацелены на быстрое выполнение небольшого набора простых команд. При выполнении сложных команд RISC – процессоры работают медленнее, чем CISC –процессоры.

Заметим, что эти две архитектуры процессоров постоянно сближаются, отбирая лучшие свойства из каждой. Тем не менее, более перспективной считается RISC-архитектура.

В ноябре 2000г. выпущен процессор Pentium 4 тактовыми частотами 1,4 и 1,5 ГГц. Процессор Pentium 4 изготавливается по 0,18-микронной технологии. В процессоре используется 144 новых команд (инструкций), предназначенных для ускорения обработки видео, мультимедиа, трехмерной графики и криптографии.

Процессор является главным элементом ЭВМ. Он прямо или косвенно управляет всеми устройствами и процессами, происходящими в ЭВМ.

В конструкции современных процессоров четко просматриваются тенденция постоянного увеличения тактовой частоты. Это естественно, чем больше операций выполняет процессор, тем выше его производительность.

Предельная тактовая частота во многом определяется существующей технологией производства микросхем, достижимыми наименьшими размерами элементов, которые определяют минимальное время передачи сигналов.

Кроме повышения тактовой частоты, увеличение производительности процессоров достигается разработчиками менее очевидными приемами, связанными с изобретением новых архитектур и алгоритмов обработки информации. Некоторые из них рассмотрим на примере процессора Pentium.

Перечислим основные особенности процессора Pentium:

· конвейерная обработка информации,

· суперскалярная архитектура,

· наличие отдельных КЭШ-памятей для команд и данных.

· наличие блока предсказания адреса перехода,

· наличие блока вычислений с плавающей точкой,

· поддержка многопроцессорного режима работы,

· наличие средства обнаружения ошибок.

Термин «суперскалярная архитектура» означает, что процессор содержит более одного вычислительного блока. Эти вычислительные блоки чаще называют конвейерами. Заметим, что первая суперскалярная архитектура была реализована в ЭВМ «Эльбрус 1 » (1978г.)

Наличие в процессоре двух конвейеров позволяет ему одновременно выполнять (завершать) две команды (инструкции).

Каждый конвейер разделяет процесс выполнения команды на несколько этапов:

· выборка (считывание) команды из ОЗУ или КЭШ-памяти

· декодирование (дешифрование) команды, т.е. определение кода выполняемой операции;

· выполнение команды;

· обращение к памяти;

· запоминание полученных результатов в памяти.

Для реализации каждого из перечисленных этапов (каждой операции) служит отдельное устройство-ступень. Таким образом, в каждом конвейере процессора Pentium имеется пять ступеней.

Основная память.

Комплекс технических устройств, реализующих функцию памяти, называется запоминающем устройством (ЗУ). ЗУ необходимы для размещения в них команд и данных. Они обеспечивают центральному процессору доступ к программам и информации.

ЗУ делятся на основную память, сверхоперативную (РОН) и внешние запоминающие устройства.

Основная память включает два типа устройств:

а) оперативное запоминающее устройство (ОЗУ) или RAM-Random Access Memory и б) постоянное запоминающее устройство (ПЗУ) или Rom-Read Onty Memory.

ОЗУ предназначена для хранения переменной информации, работает в режимах записи, чтения и хранения.

ПЗУ содержит информацию, которая не должна изменяться в ходе выполнения процессором вычислительных операции, например, стандартные программы и константы. Основные операции ПЗУ – чтение и хранение.

Функциональные возможности ОЗУ шире, чем ПЗУ, но ПЗУ сохраняет информацию при отключении питания, т.е. является энергонезависимой, и может иметь более высокое быстродействие.

В современных ЭВМ микросхемы памяти (основной и сверхоперативной СОЗУ) изготавливают из кремния по полупроводниковой технологии с высокой степенью интеграции элементов на кристалле.

Основной составной частью микросхемы является массив элементов памяти (ЭП), объединенных в матрицу накопителя.

Каждый элемент памяти может хранить 1-бит информации и имеет свой адрес ЗУ, позволяющие обращаться по адресу к любому ЭП в произвольном порядке, называются запоминающими устройствами произвольного доступа.

На английском языке оперативная память называется Rendom Access Memory (RAM) – память с произвольным доступом.

Используется два основных типа оперативной памяти:

· статистическая (SRAM-Static RAM)

· динамическая (DRAM – Dynamic RAM)

Эти две разновидности памяти различаются быстродействием и удельной плотностью (емкостью хранимой информации).

Быстродействие характеризуется:

· временем доступа (промежуток времени между формированием запроса на чтение информации из памяти и моментом поступления из памяти запрошенного машинного слова (операнда) – access mime).

· длительностью цикла (минимально допустимое время между двумя последовательными обращениями к памяти).

Эти величины измеряются в наносекундах. Чем меньше эти величины, тем больше быстродействие.

В статистической памяти ЭП построены на триггерах-схемах с двумя устойчивыми состояниями.

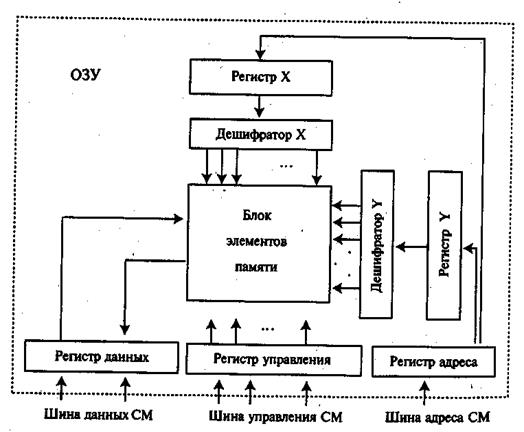

Конструктивно микросхема памяти выполняется в виде прямоугольной матрицы. При матричной организации памяти реализуется координатный принцип адресации ЭП№. В связи с чем, адрес делится на две части (две координаты) – X и Y. На пересечении этих координат находится элемент памяти, чья информация должна быть прочитана или изменена.

ОЗУ связано с остальным микропроцессорным комплектом ЭВМ через системную магистраль см. (рис.2.3.)

Рис. 2.3. Структурная схема ОЗУ

По шине управления передается сигнал, определяющий, какую операцию необходимо выполнить.

По шине данных передается информация, записывающая в память или считываемая из нее.

По шине адреса передается адрес участвующих в обмене элементов памяти (поскольку данные передаются машинными словами, а один ЭП может воспринять только один бит информации, блок элементов памяти состоит из n матриц ЭП, где n-количество разрядов в машинном слове). Максимальная емкость памяти определяется количеством линий в шине адреса системной магистрали: если количество линий обозначить через m, то емкость памяти (т.е. количество элементов памяти, имеющих уникальные адреса) определяется как 2m. Максимальный объем ОП в настоящее время увеличился до 232= 4 Гбайта.

Основными характеристиками ОЗУ является объем и быстродействие.

В современных ПЭВМ ОЗУ имеет модульную структуру. Сменные модули могут иметь конструктивное различное исполнение (SIP, ZIP, SIMM, DIMM). Увеличение объема ОЗУ обычно связано с установкой дополнительных модулей, которые выпускаются в 30-контактном (30-pin) и 72-контактном исполнениях на 1,4,8,16,32,64 Мбайта. Время доступа к модулям DRAM составляет 60-70нс. На производительность ЭВМ влияют не только время доступа, но и такие параметры, связанные с ОЗУ, как тактовая частота и разрядность шины данных системной магистрали. Если тактовая частота недостаточно высока, то ОЗУ простаивает в ожидании обращения. При тактовой частоте, превышающей возможности ОЗУ, в ожидании будет находиться системная магистраль, через которую поступил запрос в ОЗУ.

Разрядность шины данных (8,16,32 или 64 бита) определяет длину информационной единицы, которой можно обменяться с ОЗУ за одно обращение.

Интегральной характеристикой производительности ОЗУ с учетом частоты и разрядности является пропускная способность, которая измеряется в мегабайтах в секунду.

Микросхемы ПЗУ также построены по принципу матричной структуры накопителя.

Сверхоперативные ЗУ (СОЗУ) используются для хранения небольших объемов информации и имеют значительно меньшее время (в 2-10раз) считывания / записи, чем основная память. СОЗУ обычно строятся на регистрах и регистровых структурах.

Регистр представляет собой электронное устройство, способное хранить занесенное в него число неограниченно долго (при включенном питании). Наибольшее распространение получили регистры на статических триггерах.

По назначению регистры делятся на регистры хранения и регистры сдвига. Информация в регистры может заноситься и считываться либо параллельно, сразу всеми разрядами, либо последовательно, через один из крайних разрядов с последующим сдвигом занесенной информации.

В микропроцессорах ассоциативные ЗУ используются в составе КЭШ-памятидля хранения адресной части команд и операндов исполняемой программы. При этом нет необходимости обращаться в ОП за следующей командой или требуемыми операндами: достаточно поместить в маску необходимый адрес, если искомая информация имеется в СОЗУ, то она будет сразу выдана. Обращение к ОП будет необходимо лишь при отсутствии требуемой информации в СОЗУ. За счет такого использования СОЗУ сокращается число обращений к ОП, а это позволяет экономить время, так как обращение к СОЗУ требует в 2-10 раз меньше времени, чем обращение к ОП.

КЭШ-память может быть размещена в кристалле процессора (так называемая «КЭШ-память I уровня») или выполнена в виде отдельной микросхемы (внешняя КЭШ-память, или КЭШ-память II уровня).

Объем КЭШ-памяти – 16 Кбайт (I уровень)

– 256 Кб – 1 Мб (II уровень)