Архитектурные способы повышения производительности.

Повышение производительности процессоров в большинстве случаев достигается за счет применения технологических и архитектурных решений. Технологические решения: технология производства ИС, повышение тактовой частоты, уменьшение проектной нормы. Архитектурные способы связаны с рядом направлений: оптимизация системы команд с учетом развития технологий программирования, использование методов и средств параллельной обработки данных.

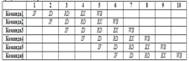

1. конвейеризация – это естественное средство реализации параллелизма линейной последовательности команд. В процессоре команда разбивается на 5–6 ступеней, которые исполняются в различных блоках процессора. Каждый блок в цепочке осуществляет только один этап исполнения команды. Полная обработка команды занимает несколько тактов. Выборка (IF) – промежуточный буфер – дешифрация команды (ID)– промежуточный буфер – чтение операции (RD)– промежуточный буфер – исполнение операции (EX)– промежуточный буфер – запись результата (WB).

В ходе выполнения команда продвигается по конвейеру, освобождая ступень для следующей команды. Для хранения информации, передаваемой между ступенями, используются внутренние промежуточные буферы, которые обновляются после каждого такта. Благодаря конвейерной обработке обрабатывается несколько следующих друг за другом команд. Из принципа конвейера следует, что повышение производительности прямо пропорционально количеству ступеней. Однако существуют ситуации, при которых в процессе выполнения происходит временная остановка конвейера, которые называются конфликтами. Конфликты снижают производительность процессора и для уменьшения их отрицательного влияния разрабатывают специальные архитектурные решения. Существует 3 типа конфликтов:

конфликты по ресурсам возникают, когда нескольким командам, находящимся на разных ступенях конвейера требуется использование одного и того же ресурса, например, памяти; конфликт по данным – ситуация, когда или исходный операнд или результат недоступны в положенное время; конфликт по управлению возникает при конвейеризации команд условного перехода и других ситуациях, приводящих к изменению значения счетчика команд.

При возникновении конфликта приходится прерывать работу конвейера на время, необходимое для устранения причин нарушения. В связи с этим есть еще дополнительные архитектурные особенности, позволяющие держать конвейер заполненным. Такие способы называются динамическим выполнением – метод, позволяющий процессору выполнять параллельно несколько команд и включающий в себя следующие элементы: предсказание множественного перехода, анализ потока команд, упреждающее выполнение.

Суперскалярность вычислений.

Означает, что на каждом этапе обрабатывается сразу несколько потоков инструкций. Современные процессоры способны запускать на исполнение не только ту команду, которая стоит на входе, но и следующие за ней.

Внеочередное исполнение команд.

Означает, что операции не обязаны выполняться в устройствах строго в том порядке, в котором определены в коде. Более поздние могут выполняться перед ранними, если не зависят от порождаемых результатов. Процессор должен лишь гарантировать, чтобы результаты внеочередного выполнения совпадали с результатами последовательного.

Процессор, оснащенный механизмом параллельного исполнения, называется суперскалярным, однако не все суперскалярные процессоры поддерживали внеочередное исполнение. Все современные процессоры поддерживают обе особенности.

Архитектура процессоров.

Процессорное ядро – конкретное воплощение микроархитектуры, являющееся стандартом для целой серии процессоров. В микроархитектуру входят длина конвейера, разновидности КЭШа и другие общие принципы.

Ядро – это воплощение микроархитектуры в кристалле, обладающее набором характеристик.

Ревизия – модификация ядра, крайне незначительно отличающаяся от предыдущей.

Частота работы ядра – как правило, каждое конкретное ядро может исполнять различное количество команд за один такт. Частота определяет количество тактов. В рамках одного и того же ядра увеличение частоты не всегда пропорционально увеличению производительности. Разные виды частот процессора делают процессоры, которые потом тестируют на частоту, то есть не существует процессора с точным, определенным значением показателя частоты.

12.Принципы взаимодействия процессора и ОП.

Контроллер памяти.

Команды и данные в процессор попадают из ОП. В современных компьютерах процессор как устройство к памяти обращаться не может. Он имеет в своем составе специализированное устройство, называемое контроллер памяти. Контроллер памяти является мостом между ОП и использующими её устройствами. Раньше контроллер памяти входил в состав chipset North Bridge. От его быстродействия во многом зависела скорость обмена данных между процессором и ОП. Процессор с помощью процессорной шины подсоединяется к контроллеру памяти. Также по процессорной шине идет обмен с видеокартой, жестким диском и другими устройствами. У классических процессоров шина одна. В современных процессорах (например, AMD) существует несколько процессорных шин. Некоторые из них работают со всеми устройствами, кроме памяти, а для памяти существует отдельная шина. В данном случае контроллер памяти встроен непосредственно в процессор. Плюсы: сокращение пути между процессором и ОП, но увеличение нагрузки на процессор при обмене с жестким диском или видеокартой с ОП.

Характеристики ОП:

Разрядность шины памяти. Вся память имеет 64-разрядную шину, то есть за один такт по шине передается 8 байт. Для шин памяти DDR. Некоторые контроллеры оснащены несколькими контроллерами, передача по которым идет независимо друг от друга. В стандартном процессоре контроллер двуканальный, в продвинутом – трехканальный.

Скорость чтения/записи. Теоретически ограничивается пропускной способностью самой памяти. 8 байт * 2 канала * 2 DDR * 200 МГц = 6,4 Гб.

Латентность. Характеристика, влияющая на фактическую скорость работы процессора с ОП. Латентность – это время, которое требуется для того, чтобы начать считывать информацию с определенного адреса. Чем больше объем памяти, тем больше её латентность.