Постановка задачи проектирования технических систем.

Постановка задачи проектирования технических систем.

2. Типовые проектные процедуры (ПП), ПП анализа и синтеза, их типичная последовательность.

Процедуры структурного синтеза по характеру проектируемого объекта делятся на:

- синтез схем (принципиальных, функциональных, структурных, кинематических и др.)

- конструкций (определение геометрических форм, взаимного расположения деталей)

- процессов (технологических, вычислительных и др.)

- документации (чертежей, пояснительных записок, ведомостей и др.).

Основные процедуры параметрического синтеза

- оптимизация номинальных значений параметров элементов

- оптимизация их допусков

- идентификация моделей

- расчеты на основе упрощенных методик

Детерминированная верификация может быть направлена на выявление соответствия структур объектов, заданных двумя различными описаниями (структурная верификация),или значений выходных параметров (параметрическая верификация). Параметрическая верификация может выполняться по полной совокупности параметров или по их части, в последнем случае различают верификацию статическую, динамическую, в частотной области.

Статистический анализ предназначен для получения статистических сведений о выходных параметрах при заданных законах распределения параметров элементов. Результаты статистического анализа можно представлять гистограммами, оценками числовых характеристик распределений выходных параметров.

Анализ чувствительности заключается в расчете коэффициентов чувствительности выходных параметров yiк изменениям параметров элементов (или внешних параметров) xi. Различают абсолютный и относительный коэффициенты чувствительности:

где xiн и yjн—номинальные значения параметров xi и yi соответственно.

Задачи, в которых исследование свойств объекта сводится к однократному решению уравнений модели при фиксированных значениях внутренних и внешних параметров, называются задачами одновариантного анализа. Задачи, требующие многократного решения уравнений модели при различных значениях внутренних и внешних параметров, называются задачами многовариантного анализа.

Основные виды анализа технических систем (ТС) при математическом

Моделировании.

Детерминированная верификация может быть направлена на выявление соответствия структур объектов, заданных двумя различными описаниями (структурная верификация),или значений выходных параметров (параметрическая верификация). Параметрическая верификация может выполняться по полной совокупности параметров или по их части, в последнем случае различают верификацию статическую, динамическую, в частотной области.

Статистический анализ предназначен для получения статистических сведений о выходных параметрах при заданных законах распределения параметров элементов. Результаты статистического анализа можно представлять гистограммами, оценками числовых характеристик распределений выходных параметров.

Анализ чувствительности заключается в расчете коэффициентов чувствительности выходных параметров yiк изменениям параметров элементов (или внешних параметров) xi. Различают абсолютный и относительный коэффициенты чувствительности:

где xiн и yjн—номинальные значения параметров xi и yi соответственно.

Модели нелинейных систем на фазовой плоскости. Анализ технических систем по фазовому портрету. Примеры построения фазовых портретов.

Совершенно так же, как и в линейной системе, процесс регулирования, описываемый уравнениями, содержащими нелинейности, может быть представлен на фазовой плоскости или в фазовом пространстве.

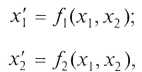

Рассмотрим и здесь в качестве основного примера случай, когда движения описываются двумя дифференциальными уравнениями первого порядка:

гдеf1(x1, х2) и f2(х1,х2) — заданные, в общем случае нелинейные функции указанных аргументов.

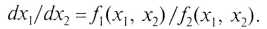

Дифференциальное уравнение фазовых траекторий получается, если вместо производных по времени ввести производнуюdx1/dx2.

Получаем:

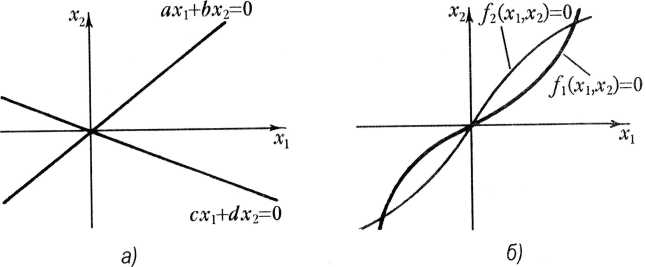

К фазовой траектории может быть проведена только одна касательная, и, следовательно, фазовые траектории не пересекаются во всех тех точках фазовой плоскости, где не обращаются одновременно в нуль f1(х1, x2) и f2(х1, х2). Особые точки системы находятся из условия dx1/dx2 = 0/0, то есть определяются как общие корни двух уравнений:

В предыдущем случае при рассмотрении линейной системы было:

и уравнения имели только одно общее решение: х1 = х2 =0. В плоскости х1, х2 этм условия в случае линейной системы определяют две прямые линии, пересекающиеся в начале координат (рис.1, а). Если же функции f1(х1, x2) и f2(х1, х2) нелинейны, то кривые, соответствующие уравнениям, могут пересекаться и вне начала координат. Система имеет в этом случае, кроме решения х1, =х2 = 0, и другие решения. В этом случае, кроме регулируемого режима, соответствующего началу координат, в системе возможны и иные положения равновесия (рис.1, б), и характер движения в системе зависит от величины отклонения от начала координат, вызванного возмущением.

Рис.1 Графики, соответствующие уравнениям для линейной (а) и нелинейной (б) систем

В рассматриваемом нелинейном случае особые точки могут быть лишь тех же типов, что и в линейной системе (фокусы, узлы и седла). Чтобы в нелинейном случае определить тип особой точки, надо составить соответствующее этой особой точке уравнение линейного приближения, разложив в окрестности этой точки в ряды правые части уравнений и сохранив затем в этих рядах только линейные члены. Эта операция эквивалентна «локальной» линеаризации системы вблизи особой точки.

Факторные модели и модели регрессионного анализа. Примеры реализации.

С помощью факторного анализа возможно выявление факторов, отвечающих за наличие линейных статистических связей корреляций между наблюдаемыми переменными.

Таким образом, можно выделить две цели факторного анализа:

- определение взаимосвязей между переменными, их классификация, т. е. «объективная R-классификация»;

- сокращение числа переменных.

Для выявления наиболее значимых факторов и, как следствие, факторной структуры, наиболее оправданно применять метод главных компонентов. Суть данного метода состоит в замене коррелированных компонентов некоррелированными факторами. Другой важной характеристикой метода является возможность ограничиться наиболее информативными главными компонентами и исключить остальные из анализа, что упрощает интерпретацию результатов. Достоинство данного метода также в том, что он – единственный математически обоснованный метод факторного анализа.

Факторный анализ – методика комплексного и системного изучения и измерения воздействия факторов на величину результативного показателя. Существуют следующие типы факторного анализа:

1. Детерминированный (функциональный) – результативный показатель представлен в виде произведения, частного или алгебраической суммы факторов.

2. Стохастический (корреляционный) – связь между результативным и факторными показателями является неполной или вероятностной.

3. Прямой (дедуктивный) – от общего к частному.

4. Обратный (индуктивный) – от частного к общему.

5. Одноступенчатый и многоступенчатый.

6. Статический и динамический.

7. Ретроспективный и перспективный.

Обязательные условия факторного анализа:

- Все признаки должны быть количественными;

- Число признаков должно быть в два раза больше числа переменных;

- Выборка должна быть однородна;

- Исходные переменные должны быть распределены симметрично;

- Факторный анализ осуществляется по коррелирующим переменным.

· По характеру взаимосвязи между показателями различают методы детерминированного и стохастического факторного анализа

· Детерминированный факторный анализ представляет собой методику исследования влияния факторов, связь которых с результативным показателем носит функциональный характер, т. е. когда результативный показатель факторной модели представлен в виде произведения, частного или алгебраической суммы факторов.

Стохастический анализ представляет собой методику исследования факторов, связь которых с результативным показателем в отличие от функциональной является неполной, вероятностной (корреляционной). Если при функциональной (полной) зависимости с изменением аргумента всегда происходит соответствующее изменение функции, то при корреляционной связи изменение аргумента может дать несколько значений прироста функции в зависимости от сочетания других факторов, определяющих данный показатель.

Регрессионная модель  — это параметрическое семейство функций, задающее отображение

— это параметрическое семейство функций, задающее отображение

где  — пространтсво параметров,

— пространтсво параметров,  — пространство свободных переменных,

— пространство свободных переменных,  — пространство зависимых переменных.

— пространство зависимых переменных.

Регрессионная модель объединяет широкий класс универсальных функций, которые описывают некоторую закономерность. При этом для построения модели в основном используются измеряемые данные, а не знание свойств исследуемой закономерности.

Примеры регрессионных моделей: линейные функции, алгебраические полиномы, ряды Чебышёва, нейронные сети без обратной связи, например, однослойный персептрон Розенблатта, радиальные базисные функции и прочее.

Частотный анализ в OrCAD.

Для выполнения частотного анализа в OrCAD необходимо использовать специализированные источники гармонических сигналов: VAC – источник напряжения; IAC – источник тока. Данные источники имеют 2 параметра: DC – значение постоянной составляющей выходного сигнала; AC – амплитуда переменной составляющей выходного сигнала.

Для выполнения частотного анализа на вкладке Analysis необходимо задать следующие опции:

- Analysistype (вид анализа) = ACSweep/Noise (частотный анализ/ анализ шума);

- ACSweeptype (тип частотного анализа) = Linear (линейное изменение частоты); Logarithmic (изменение частоты по логарифмическому закону). Если частота изменяется по логарифмическому закону, то в качестве основания может быть выбрана декада – Decade(десятичный логарифм) или Octave (логарифм по основанию 2).

Диапазон изменения частоты должен быть представлен положительными действительными числами, т.е. не допускается указывать в качестве начального и конечного значений частоты отрицательные числа и 0.

Данные характеристик будут получены в абсолютных единицах.

Таблица 4.2. Первые символы имен компонентов

| Первый символ имени | Тип компонента | ||

| В | Арсенид-галлиевый полевой транзистор (GaAsFET) с каналом n-типа | ||

| С | Конденсатор | ||

| D | Диод | ||

| Е | Источник напряжения, управляемый напряжением (ИНУН) | ||

| F | Источник тока, управляемый током (ИТУТ) | ||

| G | Источник тока, управляемый напряжением (ИТУН) | ||

| Н | Источник напряжения, управляемый током (ИНУТ) | ||

| I | Независимый источник тока | ||

| J | Полевой транзистор с управляющим р-n-переходом (JFET) | ||

| К | Связанные индуктивности и линии передачи, ферромагнитные сердечники | ||

| L | Индуктивность | ||

| М | МОП-транзистор (MOSFET) | ||

| N | Аналого-цифровой преобразователь на входе цифрового устройства | ||

| О | Цифроаналоговый преобразователь на выходе цифрового устройства | ||

| Q | Биполярный транзистор | ||

| R | Резистор | ||

| S | Ключ, управляемый напряжением | ||

| Т | Линия передачи | ||

| V | Независимый источник напряжения | ||

| W | Ключ, управляемый током | ||

| Y | Цифровое устройство | ||

| X | Макромодель (операционный усилитель, компаратор напряжения, регулятор напряжения, стабилизатор напряжения и др.) | ||

| Z | Статически индуцированный биполярный транзистор (IGBT) |

Заметим, что помимо перечисленных выше компонентов схем в состав моделируемого устройства могут входить и не электронные элементы (электрические машины, системы автоматического управления и др.), оформленные в виде макромоделей.

Язык PSpice. Анализ шума.

Статистические процессы в полупроводниках и резисторах приводят к возникновению мельчайших напряжений, которые принято называть шумами. Когда шумовые напряжения появляются в усилительных схемах, то, естественно, они тоже усиливаются и могут стать настолько значительными, что, попадая, к примеру, в динамики музыкальной установки, «режут» нам слух. Поэтому одним из наиболее важных критериев качества усилителя является величина отношения полезного сигнала к шумовому сигналу на выходе усилителя. Такое отношение (рассчитываемое логарифмически) обозначают как отношение сигнал/шум. В программе PSPICE анализ шумов называется Noise Analysis и является составной частью анализа AC Sweep.

Чтобы понять, как проводится анализ шумов, исследуем шумовую характеристику транзисторного усилителя в схеме с общим эмиттером.

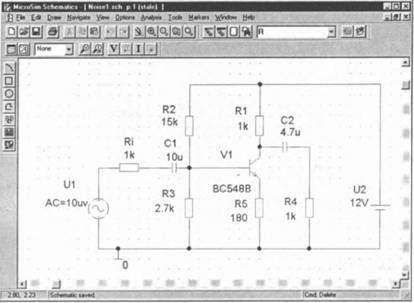

Шаг 8 Начертите схему с общим эмиттером, изображенную на рис. 9.13, и сохраните ее в папке Projects под именем NOISE1.sch.

Рис. 9.13. Схема с общим эмиттером, где рабочая точка стабилизируется путем установления отрицательной обратной связи по току

Смоделируем поведение этой схемы в диапазоне частот от 10 Гц до 1000 МГц.

Шаг 9 Откройте окноAC Sweep and Noise Analysis (рис. 9.14 и 9.15) и выполните необходимые установки в требуемом частотном диапазоне. Не забудьте установить флажок рядом с кнопкойAC Sweep… в окнеAnalysis Setup.

Рис. 9.14. Окно AC Sweep and Noise Analysis с установками для проведения анализа AC Sweep

Рис. 9.15. Окно AC Sweep and Noise Analysis с установками для проведения анализа шумов

В нижней части окнаAC Sweep and Noise Analysis расположен разделNoise Analysis. В полеOutput Voltage (Выходное напряжение) вы должны указать, в каком месте вашей схемы следует произвести расчет шумов. Допустим, вас интересует шумовая характеристика нагрузочного резистора R4, то есть напряжение V(R4:2). В поле вводаI/V нужно указать источник, для которого PSPICE вычислит эквивалентный входной шум. Это будет то напряжение шумов, какое должен генерировать данный источник, чтобы создавать в идеальной, свободной от шумов схеме такое же шумовое напряжение на выходе, как и в анализируемой схеме. В поле I/V надо обязательно ввести имя источника, иначе на экране появится сообщение об ошибке. В поле ввода Interval вы можете указать, с какими интервалами следует записывать в выходной файл подробные сведения о выходном шуме. Если вы введете в это поле, например, число 100, то в выходной файл будет записываться каждый сотый результат анализа. Это значит, что при расчете 100 контрольных точек на декаду в выходном файле окажется как раз один результат на декаду.

Шаг 10 Завершите установку параметров анализа шумов в окне AC Sweep and Noise Analysis по образцу на рис. 9.15, затем закройте это окно с помощью кнопки OK, запустите процесс моделирования и по его окончании выведите на экран PROBE диаграмму частотной характеристики выходного напряжения V(R4:2) — см. рис. 9.16.

Рис. 9.16. Частотная характеристика схемы с общим эмиттером

Диаграмма, изображенная на рис. 9.16, еще ничего не говорит о шумовой характеристике схемы. Вам еще только предстоит вызвать соответствующую диаграмму из окнаAdd Traces. С большой долей уверенности можно предположить, что шум будет значительно меньше, чем полезный сигнал. Поэтому вряд ли удастся хорошо рассмотреть их соотношение, представив обе диаграммы на одной оси координат Y, то есть на оси с общим масштабированием.

Создайте на своей диаграмме вторую ось координат Y (командаPlot Add Y Axis), а затем откройте окноAdd Traces (рис. 9.17).

Рис. 9.17. Содержание окна Add Traces после проведения анализа AC Sweep, включающего анализ шумов

Теперь в списке диаграмм появился целый ряд новых обозначений, которых раньше, при проведении обычных анализов AC Sweep, вы не встречали. Все эти новые обозначения начинаются с буквы N (то есть Noise, шум). За ними скрываются диаграммы, по которым вы можете выяснить, какой вклад вносят в полный шум отдельные резисторы и параметры транзистора. Под именем V(ONOISE) находится самый важный результат анализа шумов — спектральное распределение шумового напряжения в том месте, которое при предварительной установке было определено вами как выход.

Шаг 11 Отправьте обозначение V(ONOISE) в строку Trace Expression и щелкните по кнопке OK. Теперь на экране PRPOBE вы должны получить такую же диаграмму, как на рис. 9.18.

Рис. 9.18. Частотная характеристика и выходной шум схемы с общим эмиттером

Посмотрев на эту диаграмму, специалист сразу определит: шум в данной схеме, хотя его частотные компоненты и меньше полезного сигнала почти в 2000 раз, в целом настолько сильный, что будет создавать значительные звуковые помехи. Следовательно, необходимо выявить основную причину возникновения шума, а затем изменить схему таким образом, чтобы он уменьшился. В выходном файле вы найдете подробные данные относительно того, какой вклад вносят в полный шум резисторы и параметры транзистора (см. листинг). Например, из таблицы для частоты f=100 кГц вы узнаете, что значительное влияние на возникновение шумов оказывает внутреннее сопротивление источника напряжения. И здесь у разработчиков есть немало возможностей для оптимизации.

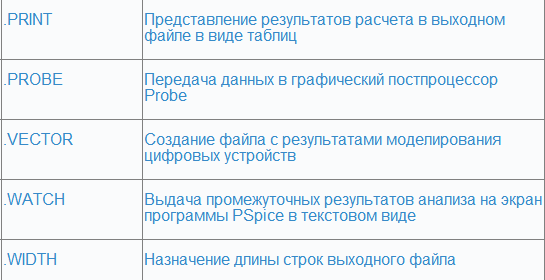

Примеры описания директив на языке PSpice.

Программа PSpice рассчитывает следующие характеристики электронных цепей:

· режим цепи по постоянному току в «рабочей точке» (Bias Point);

· режим по постоянному току при вариации источников постоянного напряжения или тока, температуры и других параметров цепи (DC Sweep);

· чувствительность характеристик цепи к вариации параметров компонентов в режиме по постоянному току (Sensitivity);

· малосигнальные передаточные функции в режиме по постоянному току (Transfer Function);

· характеристики линеаризованной цепи в частотной области при воздействии одного или нескольких сигналов (AC Sweep);

· спектральную плотность внутреннего шума (Noise Analysis);

· переходные процессы при воздействии сигналов различной формы (Transient Analysis);

· спектральный анализ (Fourier Analysis);

· "статистические испытания по методу Монте-Карло и расчет наихудшего случая (Monte Carlo/Worst Case);

· многовариантный анализ при вариации температуры (Temperature) и других параметров (Parametric).

С помощью модуля PSpice Optimizer выполняется параметрическая оптимизация.

Каждому виду расчета соответствует определенная директива.

Модели описания цифровой системы. Примеры.

Структура описания архитектурного тела VHDL. Примеры.

Полное VHDL-описание объекта состоит как минимум из двух отдельных описаний: описание интерфейса объекта и описание тела объекта (описание архитектуры).

Интерфейс описывается в объявлении объекта entity declarationи определяет входы и выходы объекта, его входные и выходные порты ports и параметры настройки generic. Параметры настройки отражают тот факт, что некоторые объекты могут иметь управляющие входы, с помощью которых может производиться настройка экземпляров объектов в частности, задаться временем задержки.

Например, у объекта Q1 три входных порта Х1, Х2, Х3 и два выхода У1, У2. Описаниеегоинтерфейсана VHDL имеетвид:

Entity Q1 is

Port (X1, X2, X3: in real; Y1, Y2: out real);

End Q1.

Порты объекта характеризуются направлением потока информации. Они могут быть:

входными (in)

выходными (out)

двунаправленными (inout)

двунаправленными буферными (buffer)

связными (linkage)

А также имеют тип, характеризующий значения поступающих на них сигналов:

целый (integer)

вещественный (real)

битовый (bit)

символьный (character)

Тело объекта специфицирует его структуру или поведение. Его описание по терминологии VHDL содержится в описании его архитектуры architecture.

VHDL позволяет отождествлять с одним и тем же интерфейсом несколько архитектур. Средства VHDL для отображения структур цифровых систем базируются на представлении о том, что описываемый объект entity представляет собой структуру из компонент componentсоединяемых друг с другом линиями связи. Каждая компонента, в свою очередь, является объектом и может состоять из компонент низшего уровня (иерархия объектов). Взаимодействуют объекты путем передачи сигналов signal по линиям связи. Линии связи подключаются к входным и выходным портам компонент. В VHDL сигналы отождествляются с линиями связи.

Описание структуры объекта строится как описание связей конкретных компонент, каждая из которых имеет имя, тип и карты портов. Карта портов port map определяет соответствие портов компонент поступающим на них сигналам, можно интерпретировать карту портов как разъем, на который приходят сигналы и в который вставляется объект-компонента.

Принятая в VHDL форма описания связей конкретных компонент имеет следующий вид:

Имя: тип связи (сигнал, порт).

Например, описание связей объекта Q1, представленного на рис. 3 выглядит следующим образом:

К1: SM port map (X1, X2, S);

K3: M port map (S, Y1);

K2: SM port map (S, X3, Y2);

Здесь К1, К2, К3- имена компонент; SM,M-типы компонент; Х1, Х2, Х3, S, Y1,Y2- имена сигналов, связанных с портами.

Полное VHDL описание архитектуры STRUCTURA объекта Q1 имеет вид:

Architecture STRUCTURA of Q1 is

Component SM port (A, B: in real; C: out real);

End component;

Component M port (E: in real; D: out real);

End component;

Signal S: real;

Begin

K1: SM port map (X1, X2, S);

K3: M port map (S, Y1);

K2: SM port map (S, X3, Y2);

End STRUCTURA;

Средства VHDL для отображения поведения описываемых архитектур строится на представлении их как совокупности параллельно взаимодействующих процессов. Понятие процесса process относится к базовым понятиям языка VHDL.

Архитектура включает в себя описание одного или нескольких параллельных процессов. Описание процесса состоит из последовательности операторов, отображающих действия по переработке информации. Все операторы внутри процесса выполняются последовательно. Процесс может находиться в одном из двух состояний - либо пассивном, когда процесс ожидает прихода сигналов запуска или наступления соответствующего момента времени, либо активном, когда процесс исполняется.

Особая роль в синхронизации процессов отводится механизму событийного воспроизведения модельного времени now.

Когда процесс вырабатывает новое значение сигнала перед его посылкой на линию связи, говорят, что он вырабатывает будущее сообщение transaction. С каждой линией связи (сигналом) может быть связано множество будущих сообщений. Множество сообщений для сигнала называется его драйвером driver.

VHDL реализует механизм воспроизведения модельного времени, состоящий из циклов. На первой стадии цикла вырабатываются новые значения сигналов. На второй стадии процессы реагируют на изменения сигналов и переходят в активную фазу. Эта стадия завершается, когда все процессы перейдут снова в состояние ожидания. После этого модельное время становится равным времени ближайшего запланированного события, и все повторяется.

Особый случай представляет ситуация, когда в процессах отсутствуют операторы задержки. Для этого в VHDL предусмотрен механизм так называемой дельта - задержки.

В случае дельта – задержек новый цикл моделирования не связан с увеличением модельного времени. В приведенном выше примере новое значение сигнала У1 вырабатывается через дельта- задержку после изменения сигнала S.

Другая способность VHDL-процессов связана с так называемыми разрешенными resolved сигналами. Если несколько процессов изменяют один и тот же сигнал, (сигнал имеет несколько драйверов), в описании объектов может указываться функция разрешения. Эта функция объединяет значения из разных драйверов и вырабатывает одно. Это позволяет, например, особенности работы нескольких элементов на общую шину.

В языке VHDL для наиболее часто используемых видов процессов – процессов межрегистровых передач – введена компактная форма записи.

Полное описание архитектуры POVEDENIE объекта Q1 в этом случае имеет следующий вид:

Architecture POVEDENIE of Q1 is

Signal S: real;

Begin

Y1<=S;

Y2<=S+X3 after 10 ns;

S<=X3+X2 after 10 ns;

End POVEDENIE;

Структура описания интерфейса проекта на языке VHDL. Примеры.

Каждый проект записан в отдельном каталоге, названном каталогом проектов. И каталог проектов и проект имеет то же самое название. Каждый каталог проектов содержит подкаталоги SRC ИGENERIC а также файлы описания проектов, которые имеют то же самое имя как и название проекта, только с расширением .ADF. Подкаталог SRC содержит исходные файлы VHDL или файлы диаграмм автоматов с конечными состояниями с расширением VHD или .ASF.Подкаталог GENERIC содержит файл рабочей области окна с .WSP расширением и рабочей библиотекой проектов с .VLB расширением. Оба имеют то же самое название как и имя проекта. Подкаталог GENERIC также содержит ряд рабочих файлов, которые используются в процессе синтеза и моделирования.Конфигурация проекта и его состояние описаны в следующих файлах:

*.ADF – Файл описания проекта, содержащий информацию относительно структуры проекта: исходные файлы и библиотеки, которые формируют проект. *.WSP – Файл рабочей области окна, содержащий данные относительно текущего состояния проекта. Он всегда востанавливает все параметры после закрытия проекта и повторного его открытия. Текущий статус содержит информацию о том какие файлы были открыты, и в каком месте текста расположен курсор какие закладки были выбраны, какие окна расскрыты и т.д.

Окно просмотра Проекта допускает, чтобы Вы выбрали проект верхнего уровня иерархиической модели. Все функциональные макро-файлы выполняться оттуда при помощи вызывов простых контекстных команд меню. Дважды нажимая на избранном файле Окна просмотра Проекта вы увидите содержимое в соответствующем окне редактирования. В процессе компиляции и верификации проекта Окно просмотра Проекта показывает все сигналы и их величины для выбранной сущности.

Окно просмотра Проекта состоит из трех панелей:

- Панель файлов (Files) показывает присоединенные к проекту файлы и содержание рабочих библиотек.

- Панель структуры (Structure) показывает структуру VHDL проекта, извлеченного из исходных файлов и объектов VHDL (сигналы и переменные), которые находятся внутри избранной области проекта.

- Панель Ресурсов (Resources) показывает папки, содержащие файлы с документацией по моделированию и сохраненные файлы формы сигнала.

Панель файлов:Верхняя часть Панели файлов показывает файлы ресурса текущего проекта. Каждый файл представлен отдельной иконкой. Форма иконки зависит от типа файла как показано далее. В случае VHDL исходных файлов и файлов диаграмм состояний автомата, цвет иконок содержит дополнительную информацию относительно состояния файла:

- Зеленый- Успешно скомпилированный

- Голубой- Не компилированный или измененный после последней компиляции

- Yellow - Ошибки произошли во время последней компиляции

Панель файлов показывает модули проекта, содержащиеся в различных определенных исходных файлах. Название модулей проекта избранных для моделирования в настоящее время показано полужирным. Верхняя часть Панели файлов показывает модули проекта, содержащиеся в выбранной рабочей библиотеке.

УСЛОВНЫЙ ОПЕРАТОР GENERATE

Для того чтобы управлять структурой проектируемого устройства используется условный оператор generate. Его синтаксис:

\условный оператор generate\ ::= \метка\: if \булевское выражение\ generate

[ {\объявление в блоке\}

begin]

{ \параллельный оператор\}

end generate [\метка\];

В зависимости от условия, заданного булевским выражением, оператор вставляет или нет в структуру устройства узлы, представленные параллельными операторами. Так как это булевское выражение влияет на структуру устройства, оно должно быть статическим. Впримере:

RESn: if \подключить_PULLUP\=1 generate RES1:for i in DATA_BUS'range generate U_ RES: PULLUP(DATA_BUS(i));end generate;end generate;Еслицелоезначение \подключить_PULLUP\ равно 1, токшине DATA_BUSподключаютсякомпонентынагрузочныхрезисторов PULLUP избиблиотеки UNISIM. Направлением научной деятельности автора является синтез структур вычислительных устройств. Поэтому язык VHDL нравится именно тем, что с помощью таких средств, как оператор generate можно программировать структуру устройства в зависимости от параметров ее настройки. Например, можно создать проект универсального цифрового фильтра, число ступеней которого изменяется в зависимости от заданного качества фильтрации.

Алфавит языка VHDL.

Как и любой другой язык программирования, VHDL имеет свой алфавит – набор символов, разрешенных к использованию и воспринимаемых компилятором. В алфавит языка входят:

- Латинские строчные и прописные буквы: A, B, . . . , Z и a, b, . . . , z

- Цифры от 0 до 9.

- Символ подчеркивания «_» (код ASCII номер 95).

Из символов, перечисленных в пп. 1–3 (и только из них!) могут конструироваться идентификаторы в программе. Кроме того, написание идентификаторов должно подчиняться следующим правилам:

- идентификатор не может быть зарезервированным словом языка;

- идентификатор должен начинаться с буквы;

- идентификатор не может заканчиваться символом подчеркивания «_»;

- идентификатор не может содержать двух последовательных символов подчеркивания «__»;

Примеры корректных идентификаторов:

cont, clock2, full_add

Примеры некорректных идентификаторов:

1clock, _adder, add__sub, entity

Следует отметить что прописные и строчные буквы не различаются, т.е. идентификаторы clock и CLOCK являются эквивалентными.

Символ «пробел» (код 32), символ табуляции (код 9), символ новой строки (коды 10 и 13).

Данные символы являются разделителями слов в конструкциях языка. Количество разделителей не имеет значения. Т.о. следующие выражения для компилятора будут эквивалентны:

count:=2+2;

count := 2 + 2 ;

count := 2

+

2;

Специальные символы, участвующие в построении конструкций языка:

+ – * / = <> . , ( ) : ; # ' " |

Составные символы, воспринимаемые компилятором как один символ:

<= >= => := /=

Разделители между элементами составных символов недопустимы.

Скалярные типы в VHDL.

Скалярные типы — это базовое множество предопределенных типов, из которых конструируются все остальные типы в VHDL. Всего определено четыре вида скалярных типов: целый, с плавающей точкой, перечисление (enumertaion) и физический тип. Также есть возможность задавать подтипы скалярных типов.

Целый тип (integer)

Объекты целого типа используются для представления абстрактных числовых значений, диапазон представления ограничен разрядностью платформы. Существует возможность задания диапазона при помощи добавочных целых типов. Для формирования значения целых типов используются целые литералы. Примеры объявления целых типов и объектов:

type Bus_width is range 0 to 64;

type Bus_width is range 63 downto 0;

– объявление переменных и сигналов данных типов

variable address_range: Bus_width:=32;

signal current_slot: Bus_index;

Для целых типов предопределены все обычные арифметические операторы и операторы отношения, при этом оба аргумента оператора должны быть одного типа. Для обеспечения сравнения объектов разного типа в VHDL определены преобразования для тесно связных типов. Все целые типы и типы с плавающей точкой являются тесно связанными типами, и их можно сравнивать при помощи явного преобразования:

if Bus_index (address_range) > current_slot …

При преобразовании между типом с плавающей точкой и целым типом выполняется округление до ближайшего целого.

Тип с плавающей точкой (real)

Объекты типа с плавающей точкой используются для представления абстрактных числовых значений, тип геа1 предопределен и включает вещественные числа. Добавочные типы с плавающей точкой могут быть объявлены явно заданием диапазона значений, допустимых для объектов данного типа. Для формирования значения типа с плавающей точкой используются действительные литералы. Примеры добавочных типов с плавающей точкой и формирования значений приведены ниже:

type Speed is range 0.0 to 100.0;

constant low_speed: Speed := 5.0;

variable current_speed: Speed;

Для типов с плавающей точкой действуют аналогичные целым типам правила преобразования при выполнении арифметических операций и операций отношения.

Перечислимый тип (enumeration)

Перечисление определяется множеством возможных значений объектов данного типа. Значения перечислимых типов упорядочены и отношение упорядочения определяется последовательностью их появления в списке объявления типа. Примерыобъявленияперечислимыхтиповиобъектов:

type Oruent is (North, South, West, East);

type bit4 is (‘U’, ’0′, ’1′, ‘Z’);

signal synch, ready: bit4;

variable direction: Orient;

variable test result:probability;

signal proceed:boolean; — предопределенныйперечислимыйтип

Существует несколько предопределенных перечислимых типов: boolean, bit, character и т.д.

Подтипы скалярных типов

Для ограничения диапазона принимаемых скалярным объектом значений используется объявление подтипа. Объявление подтипа определяет базовый тип (base type) и ограничение диапазона (range constraint); базовый тип и ограничение диапазона могут быть включены прямо в объявление объекта:

subtype SW_orient is Orient range South to West;

signal unit_orient: SW_orient;

signal unit_orient1: Orient range South to West;

В ходе моделирования проверяется соответствие назначаемого значения заданному диапазону, и в случае нарушения моделирование останавливается и выдается сообщение, описывающее это нарушение.

Операторы определяются для типов, а не для подтипов, поэтому объекты с общим базовым типом могут использоваться в одном выражении.

Предопределенные атрибуты скалярных типов

Характеристики скалярн