Проблематика проектирования комбинационных схем

Как и все цифровые устройства, функциональные узлы (рисунок 1), выполняющие типовые операции, делятся на комбинационные и последовательные (или другими словами устройства с памятью).

Рисунок 1 – Классификация функциональных узлов цифровых устройств

Выходные величины комбинационных устройств в установившемся режиме зависят только от текущего значения входных величин (аргументов). После завершения переходных процессов на выходах комбинационных устройств устанавливаются величины, на которые характер переходных процессов влияния не оказывает. С этой точки зрения переходные процессы в комбинационных устройствах не опасны. Но в цифровых устройствах в целом комбинационные устройства функционируют совместно с устройствами с памятью, что координально меняет ситуацию.

Во время переходных процессов на выходах комбинационных устройств временно появляются сигналы, не предусмотренные логическими формулами и называемые рисками сбоя или гонками. Риски возникают из-за временных состязаний сигналов в цепях цифровой электрической схемы. Со временем (после перехода схемы в устойчивое состояние) ложные сигналы исчезают, и выход комбинационных устройства приобретает значение, предусмотренное логической формулой, описывающей работу цепи.

С одной стороны это не страшно. Закончатся переходные процессы и схема заработает должным образом. Но, в случае, когда в схеме используется устройство с памятью все ложные сигналы могут быть записаны в него и в дальнейшем процесс удаления ненужной информации может занять много времени. Рассмотрим природу возникновения рисков сбоя.

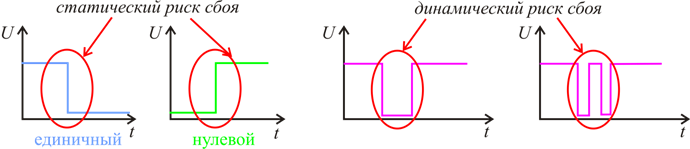

Различаю статические и динамические риски сбоя. Статические риски (рисунок 2) – это кратковременное изменение сигнала, которой должен был бы оставаться неизменным (единичным или нулевым, соответственно чему говорят о единичном или нулевом риске). Если же состояние выхода должно измениться, но вместо однократного перехода происходят многократные, то имеет место динамический риск. При динамическом риске первый и последний переходы всегда совпадают с алгоритмическими, предусмотренными логикой работы схемы. Статический риск такого свойства не имеет.

Рисунок 2 – Риски сбоя

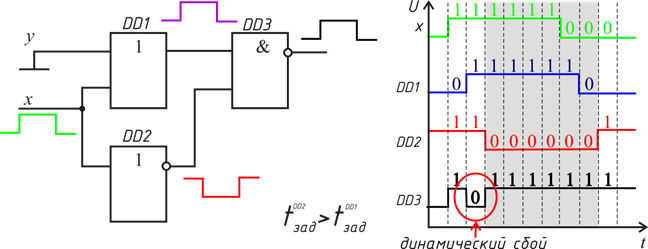

Для пояснения проблемы возникновения рисков рассмотрим схему, изображенную на рисунке 3.

Рисунок 3 – Пример, поясняющий возникновение динамического сбоя

Допустим элементы DD1 и DD2 обладают некоторыми внутренними задержками. Причем задержка сигнала в элементе DD2 больше задержки в элементе DD1. Результатом работы схемы является нестабильность выходного сигнала или другими словами динамический сбой.

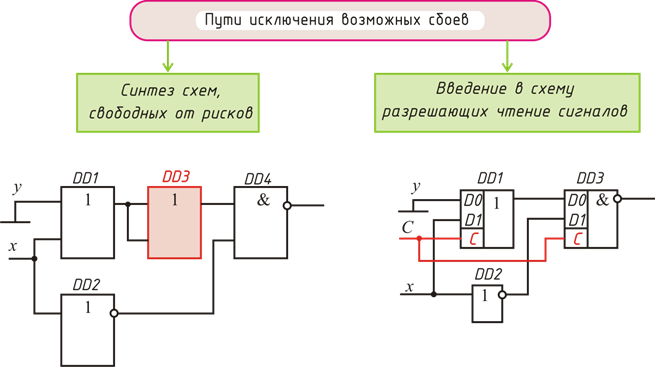

Для исключения возможных сбоев из-за явлений риска имеются два пути (рисунок 4). Первый состоит в синтезе схем, свободных от рисков, и требует сложного анализа процессов в схеме и введения избыточных элементов для исключения рисков. Этот пусть редко используется на практике.

Рисунок 4 – Пути исключения возможных сбоев в цифровых схемах

Второй путь основной для современной схемотехники, предусматривает запрещение воспроизведения сигнала комбинационных устройств на время переходных процессов. Прием информации выходов комбинационных устройств разрешатся только специальными сигналами синхронизации, подаваемыми на цифровые элементы после окончания переходных процессов в комбинационных устройствах. Таким образом, исключается воздействие ложных сигналов на элементы памяти соответствующие структуры называются синхронными.

В дальнейшем рассмотрим работу основных цифровых устройств.