Запоминающие элементы на мдп-структурах

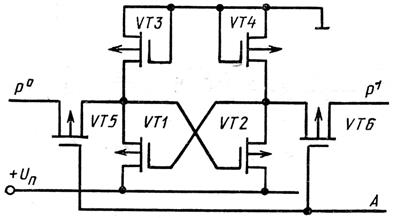

ЗУ на МДП-транзисторах.На рис. 13.31 показана схема ЗЭ на интегральном триггере, образованном МДП-транзисторами с каналом р-типа. Активными элементами

Рис. 13.31. Схема интегрального запоминающего элемента на МДП-транзисторах

триггера являются транзисторы VT1 и VT2,динамическими нагрузками которых служат транзисторы VT3 и VT4. Управление триггером при записи и считывании информации осуществляется через транзисторы VT5 и VT6.

В режиме хранения информации потенциалы разрядных шин Р0 и Р1 равны нулю, а потенциал шины А равен напряжению питания + Uп. Вследствие этого напряжения UЗИтранзисторов VT5 и VT6 имеют положительный знак и оба транзистора VT5 и VT6 закрыты. Триггер находится в одном из устойчивых состояний. Предположим, что триггер находится в состоянии хранения единицы, при котором транзистор VT1 закрыт, a VT2 — открыт. При этом потенциал стока закрытого транзистора VT1 близок к 0, а открытого VT2 — к + Uп.

Для считывания записанной информации потенциал адресной шины А уменьшают до нуля. В результате открывается транзистор VT6,так как напряжение UЗИ этого транзистора становится отрицательным и по абсолютному значению больше порогового. Вследствие этого в разрядной шине Р1появляется высокий потенциал, близкий к потенциалу стока транзистора VT2. Транзистор VT5 при этом остается закрытым, так как для него UЗИ≈0, и в разрядной шине Р0сохраняется нулевой потенциал.

При записи информации в триггер потенциал шины А также уменьшается до 0, а изменения потенциалов разрядных шин Р0и Р1 зависят от записываемой информации. Например, если в триггер необходимо записать 0, то потенциал разрядной шины Р1 сохраняется нулевым, а потенциал разрядной шины Р0 увеличивается до + Uп. В результате открывается транзистор VT1 и происходит увеличение потенциала стока этого транзистора, которое передается на затвор транзистора VT2, вследствие чего транзистор VT2 закрывается. При записи 1 потенциал разрядной шины Р0сохраняется нулевым, а потенциал шины Р1 увеличивается до + Uп. Транзистор VT6 открывается, что влечет за собой отпирание транзистора VT2 и запирание VT1.

Рассмотренный ЗЭ на МДП-транзисторах относится к классу статических запоминающих устройств. Существуют также ЗЭ динамических ЗУ, в которых информация запоминается на емкости затвора МДП-транзистора. Поскольку из-за имеющихся утечек заряд емкости постепенно уменьшается, необходимо периодически его восстанавливать.

ЗУ на МДП-структурах имеют большее время обращения, чем ЗУ на биполярных структрурах, однако они характеризуются меньшей потребляемой мощностью (статические ЗУ) и большей плотностью размещения информации.

Примерами ЗУ на МДП-структурах являются ИМС типа К501РЕ1П (ПЗУ на 2048 бит), КР505РЕ3 (ПЗУ емкостью 4096 бит), К505РУ4 (ОЗУ емкостью 256 бит) и др.

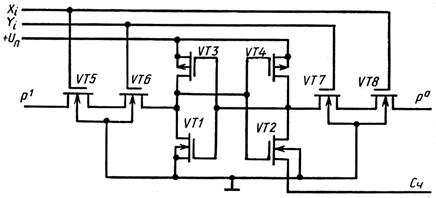

ЗУ на КМДП-транзисторах.Уменьшить время обращения к ЗУ и потребляемую им мощность можно, если вместо МДП-транзисторов использовать интегральные структуры с комплементарными МДП-транзисторами. Схема ЗЭ на КМДП-транзисторах приведена на рис. 13.32. Триггер выполнен на МДП-транзисторах VT1 и VT2 с каналами п-типа. Нагрузками транзисторов VT1 и VT2 являются МДП-транзисторы VT3 и VT4 с каналами р-ти-па. Управление триггером при записи и считывании информации осуществляется с помощью ключей на транзисторах VT5, VT6 и VT7, VT8, которые отпираются только в том случае, когда на адресные шины Xi и Уi, поступают одновременно единичные сигналы.

В режиме хранения информации Xi = Уi = 0 ключи

Рис. 13.52. Схема интегрального запоминающего элемента на КМДП -транзисторах

VT5, VT6 и VT7, VT8 закрыты, и триггер находится в одном из устойчивых состояний.

Для записи в триггер 1 на адресных шинах Xi и Уi устанавливают высокий уровень напряжения Xi = Уi ≈ + Uп,в разрядную шину Р1подают уровень 1, а в разрядную шину Р0— уровень 0. При этом триггер устанавливается в состояние, при котором транзистор VT1 закрыт, a VT2 — открыт.

При записи 0 в шину Р1подают уровень 0, а в шину Р0— уровень 1. В результате открытым оказывается транзистор VT1, а закрытым — транзистор VT2.

Считывание информации осуществляется по разрядным шинам Р1и Р0при Xi = Уi ≈ Uп. При этом шина Сч подключается к нулевому уровню или к «земле».

Интегральные ЗУ на КМДП-структурах имеются в ИМС серии К176 (К176РУ2 —ОЗУ на 256 бит с управлением, К176РМ1 —матрица-накопитель ОЗУ на 16 бит), в серии КР188 и др.

Недостатком ЗУ на биполярных и МДП-структурах является потеря информации при отключении источника питания. Этого недостатка лишены ЗУ, выполненные на интегральных МНОП-транзисторах.

ЗУ на МНОП-транзисторах.МНОП-транзистор отличается от МОП- (или МДП-) транзистора тем, что у него между пленкой диоксида кремния SiO2 и металлическим затвором помещается слой нитрида кремния Si3N4. Заряд, накопленный на границе раздела Si3N4 — SiO2, может сохраняться при отключенном питании в течение нескольких тысяч часов.

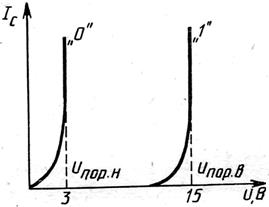

Для записи единицы в запоминающем элементе на основе МНОП-транзистора на затвор подается отрицательное напряжение —28 В, называемое критическим. При этом на границе слоев Si3N4 и SiO2 возникает заряд, а МНОП-транзистор устанавливается в состояние с высоким пороговым напряжением Uпор.в=15 В (рис. 13.33). Для записи нуля на затвор подают положительное критическое напряжение UЗ = 28 В, и МНОП-транзистор принимает состояние с низким пороговым напряжением Uпор.н = 3 В. Таким образом, состояния 1 и 0

Рис. 13.33. Передаточные характеристики МНОП-транзистора

отличаются межпороговой зоной ∆ Uпор = Uпор.в= Uпор.н = 12 В.

Для считывания записанной информации на затвор МНОП-транзистора необходимо подать напряжение UСЧ, удовлетворяющее условию Uпор.н< UСЧ < Uпор.в. При этом ток стока будет протекать через транзистор в том случае, если он находился в состоянии, характеризующемся высоким пороговым напряжением Uпор.в. Если же МНОП-транзистор находился в состоянии с низким значением Uпор.н, ток стока через транзистор протекать не будет. Для выделения записанной в МНОП-транзисторе информации в цепь стока включают резистор с малым сопротивлением.

Способность МНОП-транзисторов сохранять информацию при отключенном источнике питания позволяет использовать их для построения постоянных запоминающих устройств. Примером ПЗУ на МНОП-транзисторах являются интегральные матрицы-накопители на 128 и 256 бит, входящие в состав серии К519, и матрицы — накопители на 1024 и 2048 бит, входящие в состав серии КР558.

13.12. ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

НА ФУНКЦИОНАЛЬНЫХ ПРИБОРАХ.

Рассмотренные выше ЗЭ являются элементами интегральной микроэлектроники, схемотехнический путь развития которой связан с изготовлением на одном кристалле полупроводника большого количества электронных приборов, соединений между ними и изолирующих слоев. Микроскопические области полупроводника, в которых созданы те или иные полупроводниковые приборы, представляют собой статические неоднородности, свойства которых не должны изменяться за все время хранения и эксплуатации ИМС. Размеры статических неоднородностей уменьшаются с возрастанием уровня интеграции, но это уменьшение допустимо лишь до некоторого предела, который, как полагают специалисты, будет достигнут уже к 2000 г. В связи с этим в последние годы ведутся работы по исследованию новых физических принципов и эффектов с целью создания принципиально новых электронных устройств. Это направление получило название функциональной электроники. Работа приборов функциональной электроники основана на использовании для обработки и хранения информации динамических неоднородностей в однородном объеме твердого тела — гановских электрических доменов, цилиндрических магнитных доменов (ЦМД), пакетов зарядов в приборах с зарядовой связью (ПЗС), поверхностных и объемных акустических волн и др. Длительность существования динамических неоднородностей может быть кратковременной (в ПЗС) или долговременной (в приборах на ЦМД). Такие неоднородности создаются физическими методами и исчезают при снятии внешнего возбуждающего фактора. Динамические неоднородности обладают способностью управляемого переноса по объему тела и могут осуществлять перенос сигнала как в аналоговой, так и в дискретной форме.

В настоящее время обнадеживающие результаты применения физических явлений для создания функциональных устройств получены в нескольких направлениях исследований — акустоэлектронике, магнитоэлектронике, квантовой микроэлектронике и др.

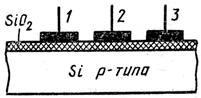

Запоминающие устройства на приборах с зарядовой связью.В ПЗС в качестве динамических неоднородностей используются пакеты зарядов неосновных носителей, создаваемых у поверхности полупроводника под действием внешнего электрического поля.

Структура ПЗС (рис. 13.34) представляет собой цепочку МДП-конденсаторов. Если на один из электродов 1, 2 или 3 подать положительное напряжение, то основные носители — дырки — уйдут в глубину подложки и под этим электродом образуется обедненная основными носителями область, которая получила название потенциальной ямы. В эту потенциальную яму соберутся неосновные носители — электроны, которые создадут в ней некоторый заряд (зарядовый пакет).

Рис. 13.34. Структура ПЗС

Если теперь подать напряжение на второй электрод U2> U1,то под этим электродом образуется более глубокая потенциальная яма, в которую перейдет заряд неосновных носителей из первой потенциальной ямы. Расстояния между электродами должны быть очень малыми, чтобы зарядовые пакеты, перетекали из одной потенциальной ямы в другую без потерь на диффузию.

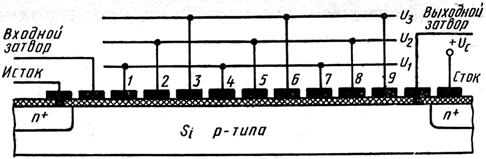

На рис. 13.35 приведена структура трехтактного сдвигового регистра на ПЗС. Он представляет собой МДП-транзистор с большим количеством затворов, в котором можно выделить три секции.

Рис. 13.35. Структура сдвигового регистра на ПЗС

Первая секция — входная — включает в себя исток и входной затвор. Все остальные затворы, подключенные к шинам U1, U2и U3, образуют вторую секцию, называемую секцией переноса. Третья секция — выходная — состоит из выходного затвора и стока.

Если на входной затвор подать напряжение Uвх> Uпopи достаточно большое напряжение на первый затвор секции переноса, то под входным затвором образуется канал п-типа, а под первым затвором секции переноса возникает потенциальная яма. В эту яму из истока по каналу перейдет часть электронов, которые создадут в ней пакет носителей заряда.

В следующем такте снимается напряжение с входного затвора. Проводящий канал между истоком и первой потенциальной ямой исчезает, а оставшийся заряд в потенциальной яме сохраняется. Это равносильно записи в данную ячейку логической единицы. Отсутствие заряда в потенциальной яме будет соответствовать логическому нулю.

Если после записи логической единицы в первую потенциальную яму подать напряжение на второй затвор секции переноса U2 > U1,то под вторым затвором будет образована более глубокая потенциальная яма, в которую перейдут электроны из первой потенциальной ямы. Для дальнейшего перемещения электронов в сторону стока напряжение U1уменьшают до нуля и подают напряжение на третий затвор U3>U2. При этом электроны из второй потенциальной ямы перейдут в третью, образованную под этим затвором. Таким образом, коммутируя различные по значениям напряжения U1, U2и U3,можно осуществить передвижение пакета неосновных носителей заряда от истока к стоку.

После переноса заряда в потенциальную яму под девятым затвором секции переноса подается напряжение на выходной затвор Uвых> Uпop. Между стоком и последней потенциальной ямой образуется канал п-типа, по которому электроны из потенциальной ямы начнут переходить в область стока, образуя в цепи стока электрический ток. Если же в потенциальную яму был записан логический нуль, то ток в цепи стока не появится или будет очень мал.

Максимальное время хранения зарядового пакета в потенциальной яме составляет 2*10-2 с. Поэтому ПЗС могут работать только в нестационарном состоянии потенциальных ям. Для управления работой устройств на ПЗС необходимы генераторы, формирующие синхронизированные между собой периодические последовательности тактовых импульсов. Интервал рабочих частот устройств на ПЗС ограничен сверху и снизу. Верхняя частота определяется потерями заряда при его продвижении между потенциальными ямами, а нижняя — процессами термогенерации, приводящими к накоплению в потенциальных ямах паразитных зарядов. Поэтому при проектировании запоминающих устройств на ПЗС должны быть предусмотрены элементы регенерации и специальные режимы работы, осуществляющие восстановление хранимой', информации.

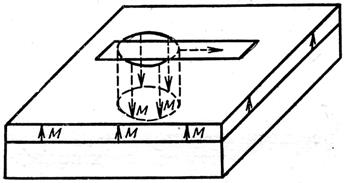

Запоминающие устройства на цилиндрических магнитных доменах.ЦМД предсталяют собой малые области, созданные в магнитных пленках. Намагниченность этих областей противоположна намагниченности пленки (рис. 13.36). Размеры ЦМД могут быть от единиц до десятков микрометров. Энергия ЦМД тем меньше, чем меньше магнитное поле, поэтому они стремятся перейти из области сильных магнитных полей в область более слабых полей, называемых магнитными энергетическими ямами. На этом свойстве основано управление движением ЦМД. Изменение магнитного поля в пленке, т. е. перемещение магнитных ям, осуществляется при помощи специального вращающегося магнитного поля.

Память, созданная на основе ЦМД,обладает высоким быстродействием (время цикла 5 * 10-7 с, считывания 10-7 с, записи 1,5 * 10-4 с) и стойкостью к радиации. ЦМД позволяет осуществлять многократную перезапись информации, а записанная информация сохраняется и при отключении источников питания.

Рис. 13.36. Запоминающий элемент на ЦМД

АНАЛОГО-ЦИФРОВЫЕ