Кроме параллельного соединения триггеров для построения регистров используются последовательное соединение этих элементов.

Последовательный регистр (регистр сдвига или сдвиговый регистр) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем).

Принципиальная схема последовательного (сдвигового) регистра, собранного на основеD триггеров и позволяющего осуществить преобразование последовательного кода в параллельный, приведена на рисунке 1. Обратите внимание, что если для параллельных регистров подходили как триггеры работающие по потенциалу (триггеры-защелки), так и триггеры, работающие по фронту, то для реализации последовательного (сдвигового) регистра подходят только D триггеры, работающие по фронту!

Рисунок 1. Схема последовательного (сдвигового) регистра

Внутри сдвигового регистра триггеры соединены последовательно, то есть выход первого соединён с входом второго и т.д. Условно-графическое изображение рассмотренного последовательного регистра приведено на рисунке 2.

Рисунок 2. Условно-графическое обозначение последовательного (сдвигового) регистра

Входы синхронизации в последовательных (сдвиговых) регистрах, как и в параллельных регистрах, объединяются. Это обеспечивает одновременность смены состояния всех триггеров, входящих в состав последовательного (сдвигового) регистра.

Преобразование последовательного кода в параллельный в последовательном (сдвиговом) регистре производится следующим образом. Отдельные биты двоичной информации последовательно подаются на вход сдвигового регистра D0. Каждый бит сопровождается отдельным тактовым импульсом синхронизации, который поступает на вход синхронизации последовательного регистра C.

После поступления первого тактового импульса логический уровень, присутствующий на входе D0, запоминается в первом триггере последовательного (сдвигового) регистра и поступает на его выход, а так как он соединён с входом второго триггера, то и на его вход. Если бы последовательный (сдвиговый) регистр был собран на D триггерах, работающих по потенциалу, то этот бит тут же записался во второй D триггер! В нашем случае этого не происходит, так как к этому моменту фронт на входе синхронизации C уже закончился.

После поступления второго тактового импульса логический уровень, присутствующий на входе второго триггера последовательного (сдвигового) регистра, запоминается в нем и поступает на его выход, а так как он соединён с входом третьего триггера, то и на его вход. Одновременно следующий бит входного последовательного кода запоминается в первом триггере последовательного (сдвигового) регистра.

После поступления четвертого тактового импульса в триггерах последовательного (сдвигового) регистра будут записаны логические уровни бит, которые последовательно присутствовали на его входе D0. Теперь этими битами можно воспользоваться, например, для отображения на индикаторах.

Пусть на вход последовательного (сдвигового) регистра поступает сигнал, временная диаграмма которого изображена на рисунке 3, тогда состояние выходов этого регистра будет последовательно принимать значения, записанные в таблице 1.

Рисунок 3. Временная диаграмма работы сдвигового регистра

На рисунке 3 вместе с логическими уровнями записываются значения бит, которые передаются по соединительной линии или присутствуют на выходах сдвигового регистра.

| № такта | | | | |

| Q0 | | | | |

| Q1 | X | | | |

| Q2 | X | X | | |

| Q3 | X | X | X | |

В качестве примера реализации последовательного (сдвигового) регистра можно назвать отечественную микросхему 1564ИР1 или иностранную 74НС164.

Универсальные регистры

Регистры сдвига выполняют обычно как универсальные последовательно-параллельные микросхемы. Это связано с необходимостью записи в регистр параллельного двоичного кода при преобразовании параллельного кода в последовательный.

Переключение регистра из параллельного режима работы в последовательный и наоборот осуществляется при помощи мультиплексора (коммутатора). Использование коммутатора позволяет входы D триггеров универсального регистра либо подключать к внешним выводам микросхемы, либо подключать к выходу предыдущего триггера.

Напомню, что двухвходовый мультиплексор можно реализовать при помощи логических элементов “2И-2ИЛИ”. Элементы “И” при этом работают в качестве электронных ключей, а элементы “ИЛИ” объединяют их выходы.

Схема универсального регистра с использованием коммутаторов на логических элементах “2И-2ИЛИ” приведена на рисунке 1.

Рисунок 1. Принципиальная схема универсального регистра

В этой схеме для переключения регистра из последовательного режима работы в параллельный используется вывод V. Подача на этот вход единичного потенциала превращает схему в параллельный регистр. При этом на входы ключей, подключенных к информационным входам D, подаётся единичный потенциал. Это приводит к тому, что сигналы с входов параллельной записи данных поступают на входы логических элементов “ИЛИ”, а на входы ключей, подключенных к выходам предыдущих триггеров, подаются нулевые потенциалы. То есть на выходах этих ключей будут присутствовать нулевые потенциалы, и они не будут мешать работе.

Подача на вход V нулевого потенциала приводит к отключению входов параллельных данных от входов триггеров. Сигналы же с выхода предыдущего триггера свободно проходит через верхние логические элементы “И” на вход последующего триггера, так как на его второй вход подаётся единичный потенциал.

Инверторы на входах V и C использованы для усиления входного сигнала по току. В результате входной ток микросхемы будет равен не суммарному току четырёх логических элементов “И”, а входному току инвертора.

Условно-графическое изображение универсального регистра приведено на рисунке 2. Вход последовательного ввода данных на этом рисунке обозначен как DI и отделён от других групп входов чертой. Точно так же выделены в отдельные группы и входы управления V и синхронизации C.

Рисунок 2. Обозначение универсального регистра на принципиальных схемах

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

27. Демультиплексор

Демультиплексорами называются устройства, которые позволяют подключать один вход к нескольким выходам. Демультиплексор можно построить на основе точно таких же схем логического "И", как и при построении мультиплексора. Существенным отличием от мультиплексора является возможность объединения нескольких входов в один без дополнительных схем. Однако для увеличения нагрузочной способности микросхемы, на входе демультиплексора для усиления входного сигнала лучше поставить инвертор.

Схема демультиплексора приведена на рисунке 1. В этой схеме для выбора конкретного выхода демультиплексора, как и в мультиплексоре, используется двоичный дешифратор.

Рисунок 1. Принципиальная схема демультиплексора, управляемого двоичным кодом

Однако, если рассмотреть принципиальную схему самого дешифратора, то можно значительно упростить демультиплексор. Достаточно просто к каждому логическому элементу 'И', входящему в состав дешифратора просто добавить ещё один вход – In. Такую схему часто называют дешифратором с входом разрешения работы. Условно-графическое изображение демультиплексора приведено на рисунке 2.

Рисунок 2. Условно графическое обозначение демультиплексора с четырьмя выходами

В этом обозначении вход In обозначен как вход E, а выходы не названы никак, оставлены только их номера.

В МОП микросхемах не существует отдельных микросхем демультиплексоров, так как МОП мультиплексоры, описанные ранее по информационным сигналам не различают вход и выход, т.е. направление распространения информационных сигналов, точно также как и в механических ключах, может быть произвольным. Если поменять входы и выход местами, то КМОП мультиплексоры будут работать в качестве демультиплексоров. Поэтому их часто называют просто коммутаторами.

Комбинационные устройства

Цифровыми устройствами комбинационного типа или цифровыми автоматами без памяти называются цифровые устройства, логические значения на выходе которых однозначно определяются совокупностью или комбинацией сигналов на входах в данный момент времени. К ним относятся суммирующие схемы, шифраторы и дешифраторы, мультиплексоры и демультиплексоры, цифровые компараторы и другие устройства. Цифровые устройства комбинационного типа выпускаются в виде интегральных микросхем или входят в состав больших интегральных микросхем, таких как процессоры, запоминающие и другие устройства.

Двоичные сумматоры

Одноразрядные сумматоры

В цифровой вычислительной технике используются одноразрядные суммирующие схемы с двумя и тремя входами, причём первые называютсяполусумматорами, а вторые — полными одноразрядными сумматорами. Полусумматоры могут использоваться только для суммирования младших разрядов чисел. Полные одноразрядные сумматоры имеют дополнительный третий вход, на который подаётся перенос из предыдущего разряда при суммировании многоразрядных чисел.

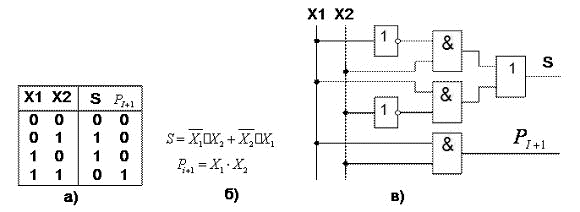

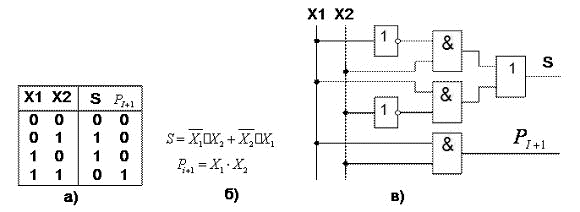

На рисунке 1, а) приведена таблица истинности полусумматора, на основании которой составлена его структурная формула в виде СДНФ (Рисунок 1, б). Функциональная схема, составленная на элементах основного базиса в соответствии с этой структурной формулой, приведена на рисунке 21, в).

Рисунок 1 Одноразрядный полусумматор:

а) таблица истинности, б) структурная формула, в) функциональная схема.

Основными параметрами, характеризующими качественные показатели логических схем, являются быстродействие и количество элементов, определяющее сложность схемы.

Быстродействие определяется суммарным временем задержки сигнала при прохождении элементов схемы. В приведённой выше схеме быстродействие определяется задержкой в трёх логических элементах.

Многоразрядные сумматоры

Методы построения многоразрядных сумматоров:

- Последовательное суммирование;

- Параллельное суммирование с последовательным переносом;

- Параллельное суммирование с параллельным переносом.

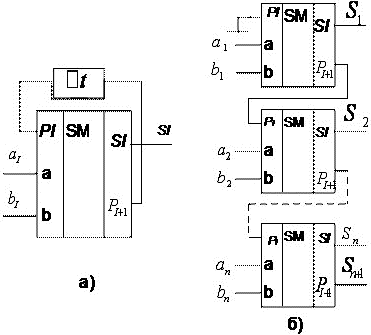

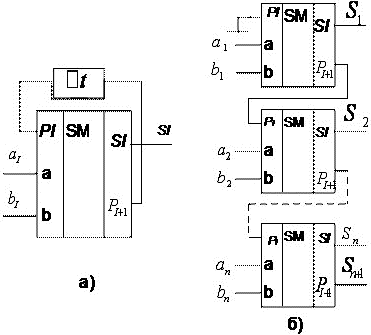

Рисунок 2. Суммирование многоразрядных чисел:

а) — Последовательное; б) — Параллельное с последовательным переносом

При последовательном суммировании используется один сумматор, общий для всех разрядов (Рисунок 2, а). Операнды должны вводиться в сумматор через входы аI и bI синхронно, начиная с младших разрядов. Цепь задержки обеспечивает хранение импульса переноса PI+1 на время одного такта, то есть до прихода пары слагаемых следующего разряда, с которыми он будет просуммирован. Задержку выполняет D-триггер. Результаты суммирования также считываются последовательно, начиная с младших разрядов. Для хранения и ввода операндов на входы сумматора, а также для записи результата суммирования обычно используются регистры сдвига.

Достоинство этого метода — малые аппаратные затраты.

Недостаток — невысокое быстродействие, так как одновременно суммируются только пара слагаемых.

Схема параллельного сумматора с последовательным переносом приведена на рисунке 2, б). Количество сумматоров равно числу разрядов чисел. Выход переноса PI+1 каждого сумматора соединяется со входом переноса PI следующего более старшего разряда. На входе переноса младшего разряда устанавливается потенциал «0», так как сигнал переноса сюда не поступает. Слагаемые aI и bI суммируются во всех разрядах одновременно, а переносPI поступает с окончанием операции сложения в предыдущем разряде.

Быстродействие таких сумматоров ограничено задержкой переноса, так как формирование переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал переноса не распространится по всей цепочке сумматоров.