Комбинацияланған логикалық (қисындық) сұлбаларды синтездеу

Өрнектердің күрделілігіне байланысты құрылатын схема да күрделі болып шығады. Сондықтан, көптеген жағдайда схема құруға пайдаланылатын логикалық өрнекті қарапайым түрге келтіру (яғни, минимизациялау) керек болады.

Минимизация жүргізудің бірнеше жолы бар, енді соларды қарастыралық.

1.1.4.1.1 Тікелей түрлендіру тәсілі

Бұл тәсілмен логикалық функцияларды түрлендіру (минимизациялау) функция құрамындағы көрші термдерді тауып, оларға логика алгебрасының жоғарыда келтірілген заңдары мен заңдылықтарын тікелей пайдаланып біріктіру арқылы жүзеге асырылады. Көрші термдерге бір аргументінің ғана айырмашылығы бар термдер жатады.

1.1.4.1.2 Карно картасы арқылы түрлендіру

Карно картасы – логикалық өрнектерді минимизациялауға ыңғайлан-дырылған, функцияның кестелі суреттелімінің ерекше түрі. Жоғарыда алын-ған мысалдағы функцияға құрылған Карно картасы 1.1-суретте келтірілген.

| X1 | ||||

| X2 | ||||

| X0 |

1.1 Сурет

Карно картасында көрші термдер бірден көзге түседі: келтірілген картаның 1-, 3-, 5-, 7-ұяшықтарындағы бірліктердің өзара бірігіп, нәтижесінде одан X0 ғана қалатындығы және 4-ұяшықтағы бірліктің тек қана 5-ұяшықтағы бірлікпен бірігетіндігі көрініп тұр.

Төрт аргументті функцияға арналған Карно картасының түрі 1.2-суретте келтірілген.

| X2 | |||||

| X3 | |||||

| X1 | |||||

| X0 |

1.2 Сурет

1.1.4.1.3 Арнайы түрлендіргішті пайдалану

Цифрлық құрылғыларды моделдеуге арналған бағдарламаларда мысалы, Electronics Workbench моделдеу жүйесінде минимизациялау жұмысын орындайтын арнайы түрлендіргіш (Logic Converter) орналастырылған.

7 Емтихан билеті

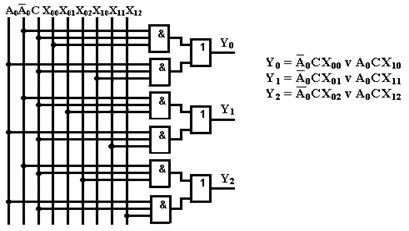

1. Матрицалық дешифраторды синтездеу.

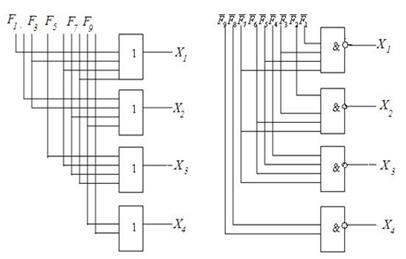

Матрицалық дешифратор – шығыс функциясы қандай да бір минтермге тең болатын k бөлек іске асырылған [n,1] полюстіктерінің бірігуі.

n=3 (үшразрядты) k =23 =8 дешифраторды синтездеу керек болсын.

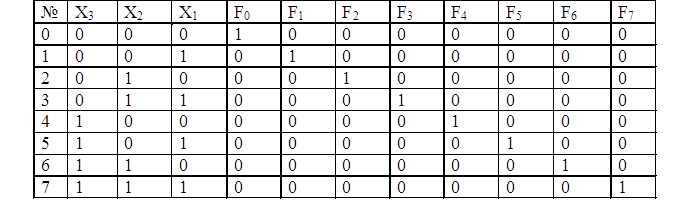

2- кестеде шындық кестесі көрсетілген

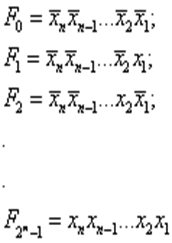

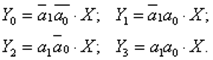

Жеке функциялардың түрлері:

F0 =  F4 =

F4 =

F1 =  F5 =

F5 =

F2 =  F6 =

F6 =

F3 =  F7 =

F7 =

2. Дешифратордың ЖӘНЕ қисындық элементтердегі жұмыс істеуі.

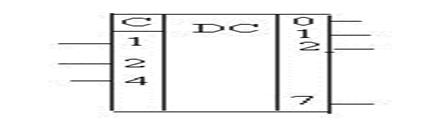

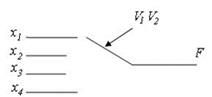

Шифратордың шартты белгісі 3-суретте көрсетілген

3-сурет

3-сурет

• Дешифратор.

Дешифратор – бұл көп шығысты комбинациялық логикалық схема (КЛС), мұнда айнымалылардың кірістегі әрбір комбинациясына шығыстардың тек біреуіндегі бірлік сигнал сәйкес келеді.

Екілік дешифратор екілік кодты «k-дан 1» кодына түрлендіреді.

ЭЕМ-де дешифратор арналық коммутация үшін, такті нөмірін, жады ұяшығының адресін дешифрлау үшін қолданылады.

n кірісі және k шығысы бар.

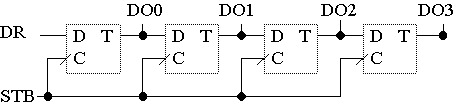

Дешифратордың кірістері разрядтың 1,2,4,8… екілік салмақтарымен белгіленеді, шығысы – олардың қозуын тудыратын теру номерлерімен белгіленеді. 2.24 суретте үшразрядты дешифратордың шартты белгіленуі көрсетілген. Дешифраторда кейде уақыттың белгілі бір интервалында шығыс сигналдың жасалуына рұқсат беретін стробтау операциясы орындалады.

4-сурет

4-сурет

- кірістегі екілік айнымалылар.

- кірістегі екілік айнымалылар.

Дешифраторларды әр түрлі элементтер базисінде құруға болады.

Мысалы, «ЖӘНЕ» кіріске тура және инверсті кіріс сигналы беріледі.

Дешифраторды тұрғызудың үш әдісі қоланылады:

а) сызықтық немесе матрицалық;

б) пирамидалық немесе ағаш тәрізді;

в) тікбұрышты немесе сатылы.

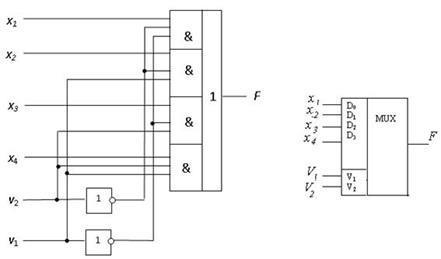

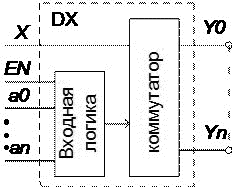

3. ЖӘНЕ-ЕМЕС үшін мультиплексор сұлбасы

Мультиплексор

Мультиплексор – бір шығысы бар көпкірістік КЛС, жалғыз ортақ шығыс шинасын, екілік кодпен берілген басқарушы сигналға байланысты, кірістердің біреуіне қосады (7- суретті қара).

Мультиплексор параллелді кодты тізбектейтін кодқа түрлендіру, кодтарды салыстыру үшін және т.б. қолданады.

Микросхемалар серияларында келесі мультиплексорлар қолданылады:

а) 4 те 1 (n=4 k=2 );

б) 8 да 1 (n=8 k=3);

в) 16 да 1 (n=16 k=4).

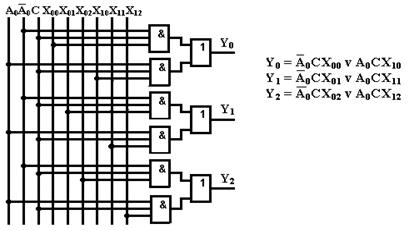

4 тен 1 мультиплексорын құрастырайық.

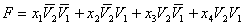

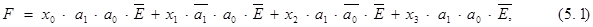

n=4, k=2 үшін (n=2k) жеке функция түрі келесідей болады:

7-сурет

7-сурет

ЖӘНЕ-ЕМЕС негізіндегі жеке функциялар (Де Морган теоремасы бойынша түрлендірілген) келесі түрде болады:

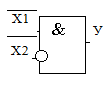

x1=

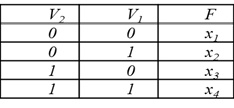

«ЖӘНЕ-ЕМЕС» элементтері негізіндегі схема 2-суретте көрсетілген.

1-сурет 2-сурет

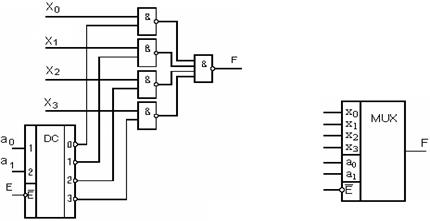

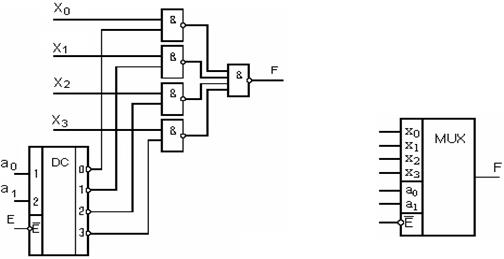

5.1-суреттегі схемада екі кірісті ЖӘНЕ-ЕМЕС логикалық элементі дешифратордың шығыс сигналдарымен басқарылады, ал дешифратордың кірісіне адрестік сигналдар берілген болатын. Сонымен, дешифратор көмегімен екі кірісті ЖӘНЕ-ЕМЕС логикалық элементтерінің бірі таңдалынады, және сол арқылы және екінші сатыдағы ЕМЕС логикалық элементі арқылы ақпарат шығысқа беріледі. Және бұл жағдайда мультиплексор жылдамдығы дешифратордағы және екі ЖӘНЕ-ЕМЕС логикалық элементтердегі сигналдардың таралуының бөгелу қосындысымен анықталады.

а) ә)

Сурет - 5.1. Мультиплексор схемасы (а) және оның шартты-графикалық белгіленуі (ә)

№ 8 Емтихан билеті

1. ЖӘНЕ – ЕМЕС үшін мультиплексор сұлбасы

2. Мультиплексорлар жұмыс принципі

3. эмиттерлі байланысқан логика ЭСЛ – сұлбалары

1. ЖӘНЕ – ЕМЕС үшін мультиплексор сұлбасы

| Х1 | Х2 | У | |

Мультиплексор. Мультиплексор деп ақпаратты бірнеше кіріс каналынан бір шығысқа тасымалдауды басқаратын құрылғы. Мультиплексорда ақпараттық кірспен қоса, адрестік (басқарушы) кіріс және мультиплекор жұмысына рұқсат беруші стробтаушы кіріс бар. Адрестік кірістегі сигналдар дәл қазір ақпараттық кірістердің қайсысышығыспен қосылғанын анықтайды. Әдетте m ақпараттық кірістермен n адрестік кірістер арасында m = 2n қатынасы орнаған.

1 стробтаушы, 2 адрестік және 4 ақпараттық кірістері мультиплексор жұмысын логикалық теңдеумен баяндауға болады:

|

мұнда Е – стробтаушы кірістегі сигнал, оның белсенді деңгейі мультиплексор жұмысына рұқсат береді.

Жұмысқа рұқсат беруші Е стробтаушы кірісіне логикалық 1 сигналы берілсе (E=1), онда xi ақпараттық және aj адрестік сигналдардың мәніне қарамастан (i = 0, 1, 2, 3 және j = 0, 1) мультиплексордың шығыс сигналы нөлге тең болады.

Басқаша айтқанда Е стробтаушы сигнал көмегімен таңдалған кірісті шығыспен жалғануына рұқсат беруге немесе бермеуге болады, яғни мультиплексор әрекетін бөгеуге болады.

(5.1) өрнегіне сәйкес жұмыс істейтін мультиплексордың схемасы және шартты-графикалық белгіленуі 5.1-суретте көрсетілген.

5.1-суреттегі схемада екі кірісті ЖӘНЕ-ЕМЕС логикалық элементі дешифратордың шығыс сигналдарымен басқарылады, ал дешифратордың кірісіне адрестік сигналдар берілген болатын. Сонымен, дешифратор көмегімен екі кірісті ЖӘНЕ-ЕМЕС логикалық элементтерінің бірі таңдалынады, және сол арқылы және екінші сатыдағы ЕМЕС логикалық элементі арқылы ақпарат шығысқа беріледі. Және бұл жағдайда мультиплексор жылдамдығы дешифратордағы және екі ЖӘНЕ-ЕМЕС логикалық элементтердегі сигналдардың таралуының бөгелу қосындысымен анықталады.

а) ә)

Сурет - 5.1. Мультиплексор схемасы (а) және оның шартты-графикалық белгіленуі (ә)

2. Мультиплексорлар жұмыс принципі

Мультиплексор – ЭЕМ функционалды түйіні, m –кірістердің бірінен n –разрядты кіріс сигналын n – разрядты шығысқа коммутациялауға арналған.

Мультиплексор есептеу машинасында қолданылады, мысалы, ақпараттың қандай көзінен ақпарат процессор кірісіне келіп түседі, саны анықтайды (ақпарат көзі – процессордың қызмет етуші регистрлері, L1 деңгейлі КЭШ жады, жедел жады, винчестер, сыртқы ЕСҚ және т.б.)

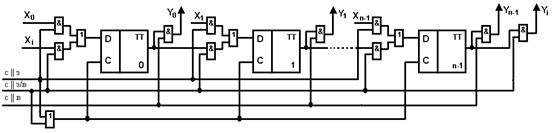

3 разрядтан 2 каналды мултьтиплексордың базалық сұлбасы:

2.24 – сурет. 3 разряд бойынша 2 каналды мультиплексор

мұндағы A0 – мекендік шина, егер

A0 = 0 (яғни  =1), онда ақпарат 0-ші каналдан қабылдайды;

=1), онда ақпарат 0-ші каналдан қабылдайды;

A0 = 1 (яғни  =0), онда ақпарат 1-ші каналдан қабылдайды.

=0), онда ақпарат 1-ші каналдан қабылдайды.

Xij – ақпарат арналары.

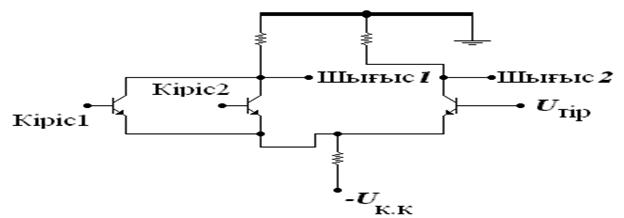

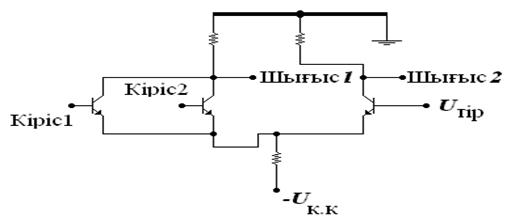

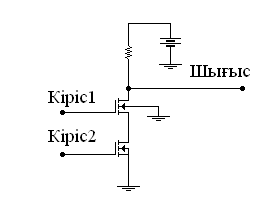

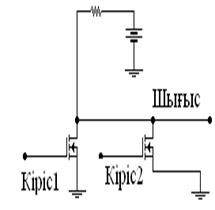

3. эмиттерлі байланысқан логика ЭСЛ – сұлбалары

ЭСЛ технологиясы ТТЛ технологиясы сияқты биполярлы, яғни элементтері биполярлы құрылымдардан жасалады. ЭСЛ элементтерінің негізі «ток ауыстырғышы» деп аталады, Немесе-Емес (3-сурет); 1-шығысында логикалық НЕМЕСЕ-ЕМЕС, ал 2-шығысында – НЕМЕСЕ логикалық функциясы бар.

ЭСЛ элементтерінің негізгі қасиеті мыналар: өте жоғары жылдамдық, үлкен жүктемлік қабілет, жұмыс температурасы мен қоректену кернеуі өзгергендегі динамикалық параметрлерінің жоғары тұрақтылығы, төмен онда келісілген желі мен жүктемеде жұмыс істеу қабілеті, салыстырмалы жақсы бөгеуілге тұрақтылық.

Жасалған сандық ЭСЛ ИС-ң ішінде К500 және К1500 сериялы микросұлбалар кең таралады, бұлар МС 10000 мен Ғ100К микросұлбаларының функционалдық аналогы.

К500 сериялы микросұлба істік шығыста пластмасслық және керамикалық қорапта шығарылады, ал К1500 сериялы микросұлба негізінен керамикалық қорапта шығыстары планарлы болып дайындалады.

Негізінде ЭСЛ элементтерінің екі не үш кірісі бар. Кіріс санын көбейту кіріс паразисттік сиымдылығын өсіреді, бұл жылдамдықты төмендетеді.

ЭСЛ схемаларының кіріс кедергісі төмен болғандықтан жылдамдықтары жоғары және активті режимде жұмыс істейді, кіріске түскен бөгеттер күшейеді. Бөгеуіл төзімділігін жоғарылату үшін коллекторлы қорек көзінің шинасын жуан жасайды және жалпы шинамен байланыстырады.

3-сурет - ЭСЛ базалық элементі

ТТЛ схемаларымен салыстырғанда ЭСЛ схемалары жоғары жылдамдықта, бірақ бөгеуіл төзімділіктері төмен. ЭСЛ схемалары кристалда көп орын алады, көп қуат қолданып шығыс транзисторы ашылып үлкен ток жүреді. Осы технология бойынша жасалған схемалар оң кернеулі қорек көзін пайдаланатын басқа технология схемаларымен өзара байланыспайды.

9 ЕМТИХАН БИЛЕТІ

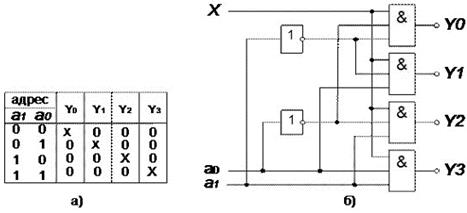

1. Демультиплексорлар жұмыс принципі.

Бір кіріске түсетін ақпаратты N шығысқа басқарылатын коммутацияны іске асыратын функциональдық түйіншікті демультиплексор дейміз.Сонымен демультиплексор мультиплексордың іске асыратын операциясына кері операция. Демультиплексордің жалпылама сұлбасы

көрсетілген.

көрсетілген.

Жалпы жағдайда шығатын желілердің саны N адрестік кірістердің n санымен анықталады және N=2n тең. n=2 жағдай үшін демультиплексордің жұмыс істеуі көрсетілген ақиқат кестесіне сәйкес іске асырлады.

Ақиқат кестесі- а) және 4-канальдыдемультиплексордың функциональдық сұлбасы -б)Ақиқат кестесінен демультиплексордыңсипатама теңдеуін жазамыз:

Бұл теңдеулерге сәйкес демультиплексордың функциональдық сұлбасы (б суретте) келтірілген. Оның құрамында екі инвертор және төрт «ЖӘНЕ» элементі бар.Демультиплексора и дешифратора Ақиқат кестесін және функциональдық сұлбасын салыстыра отырып, олардың функциясының ұқсас екенін жеңіл көруге болады.Егер функция X=1тұрақты болса, онда мультиплексор дешифратордың функциясын орындайды.Дешифратор мен демультиплексордың микросхемалары ИЕ деген бірдей шартты белгісі бар, орындайтын функцияларының ұқсастығын еске ала отырып,оларды «Дешифратор-демультиплексор» деп атаймыз және дешифратормен демультиплексордың екеунің де функциясын орындай алады.

2. Цифрлық компараторлар жұмыс принципі.

Цифрлық компараторлар-екі санның тең екендігінің немесе қайсысының үлкен екендігін анықтайтын салыстырудың универсаль құрылғысы болып саналады.

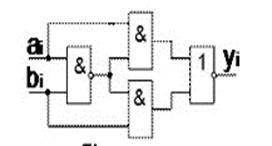

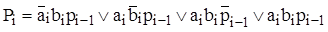

Екі бір разрядты санды салыстыру қарапайым есебін карастырайық. Бұл жұмысты іске асыратын бір разрядты компаратордың сұлбасы көрсетілген.

Бұл сұлбаның жұмыс істеу принципін қарастырғанда мыныны: егер ai<bi, сонда

ai = 0, алbi = 1 және керісінше екенін еске алу керек. Көп разрядты сандарды салыстыру үшін келесі алгоритм қолданылады. Басында үлкен разрядтарының мәні салыстырылады. Егер олар әр түрлі болса,онда бұларды салыстыру нәтижесін солар анықтайды. Егер олар тең болса, онда одан кейінгі кіші разрядтарды, тағысы басқалар.Цифрлық компараторлар жеке микросхема түрде шығарылады. Мысалы, К561ИП2 екі 4-разрядты санды теңсіздік таңбасымен анықтайды.

Суретте оның ШГБ (шарты графикалық белгісі) келтірілген. Құрылғының екі салыстыратын санның разрядын өсіру қасиеті бар. Мысалы, 8-разрядты сандарды салыстыру үшін екі төртразрядты микросхемаларды қолдануға болады.Бұл мақсатта МС К561ИП2 үш қосымша кіріс қарастырылған:A > B, A = B және A > B, оларға кіші разрядты салыстыруды орындайтын микросхемалардың сәйкес шығыстары келтірілген. Егерде тек бір ғана микросхема қолдынылатын болса, онда A = B кірісіне лог. «1»,ал A < B және A > Bлог. «0» беру керек.

3. Қосындылағыштар түрлері

Қосындылағыш арифметикалық-логикалық құрылғының (АЛҚ) негізгі түйіндерінің бірі болып табылатын және ол екілік код түрінде көрсетілген сандармен арифметикалық қосу, алу операцияларын орындауға араналған. Азайту операциясы кері және қосымша кодтарды қолдану арқылы орындалады. Қосындылағыштарды бірразрядты және көпразрядты қосындылағыштар деп бөледі. Қосындылағыштардың мұндай жіктелуі қосындыланатын кодтардың разрядтарының саны бойынша іске асырылады. Көпразрядты қосындылағыштарды тізбекті және параллельды деп бөледі. Тізбекті қосындылағыштарды қосу операциясы тізбектей орындалады. Паралельды қосындылағыштарда кіріс кодтарының барлық разрядтары біруақытта қосындыланады, ал тасымал сигналы әртүрлі әдістермен қалыптасады. Осыған сәйкес паралельды қосындылағыштарды тізбекті, параллельды, топтық, топ аралық параллельды тасымалдары бар деп бөледі.

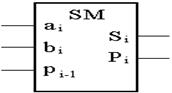

Бірразрядты қосындылағыш, шартты графикалық белгіленуі суретте келтірілген, оның S қосындысының функциясы және көрші үлкен разрядқа Р тасымалы қалыптасатын, үш кірісі (екі қосынды және кіші разрядтан тасымал) және екі шығысы бар.

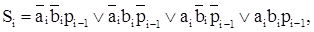

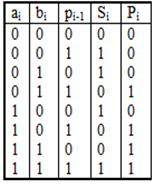

Si қосындысының функциясы және Pi тасымалы үшін, бірарзрядты қосындылағыштың ақиқаттық кестесімен сәйкес логикалық өрнектер мына түрге ие болады

.

.

Бірразрядты қосындылағыштың шартты белгіленуі.

Бірразрядты қосындылағыштың шартты белгіленуі.

Қосындылағыштың ақиқаттық кестесі

Қосындылағыштың ақиқаттық кестесі

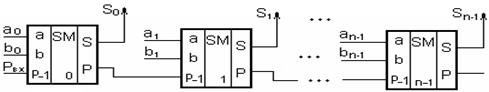

Тізбекті тасымалы бар параллельды қосындылағыш тасымал тізбектері бойынша тізбектей қосылған біразрядты қосындылағыштардың тізбегі ретінде құрылады. Параллельды қосындылағышта қосу операциясы қосынды кодтардың барлық разрядтары бойынша біруақытта орындалады.

Тізбекті тасымалы бар параллельды қосындылағыштың сұлбасы

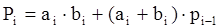

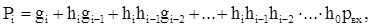

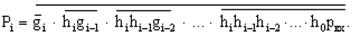

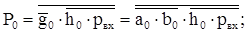

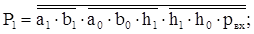

Параллельлы тасымалы бар параллельды қосындылағыштар максималды шапшаңдылыққа ие. Оларда тасымал сигналдарының разрядтан разрядқа тізбектей таралу үрдісі жоқ және нәтижелер уақыт бойынша параллельды алынады. Бір уақытылы тасымалды ұйымдастыру мақсаты мынада: қосындылағыштың әр i-ші разрядында қосындының кодаларын қосу кезінде  тасымал функциясы қалыптасады, ол теңдеуге сәйкес мына түрге ие болады

тасымал функциясы қалыптасады, ол теңдеуге сәйкес мына түрге ие болады

,

,  (1)

(1)

және

және  белгіленулерін енгізіп, (1) өрнегін қайта жазайық:

белгіленулерін енгізіп, (1) өрнегін қайта жазайық:  . (2) Сәйкесінше тасымал сигналы үшін де өрнекті жазайық

. (2) Сәйкесінше тасымал сигналы үшін де өрнекті жазайық

|

(3)

(3) өрнегін (2) қою арқылы, алатынымыз

(4)

(4)

Осы әрекеттерді нқльдік разрядқа дейін орындап i-ші разрядта тасымал сигналының қалыптасу заңын сипаттайтын өрнекті аламыз

(5)

(5)

мұндағы  – қосындылағыштың кірісіне берілетін тасымал сигналы. Тасымал функцияларының нормалды дизъюнктивті пішімі болады және ЖӘНЕ-НЕМЕСЕ ЛЭ базисінде жүзеге асырылуы мүмкін.

– қосындылағыштың кірісіне берілетін тасымал сигналы. Тасымал функцияларының нормалды дизъюнктивті пішімі болады және ЖӘНЕ-НЕМЕСЕ ЛЭ базисінде жүзеге асырылуы мүмкін.

Жоғарыда айтылғанды ескере отырып, (5) өрнекті ЖӘНЕ-НЕМЕСЕ базисінде жазайық

|

Бұдан 4-разрядты қосындылағышта тасымал сигналының қалыптасу өрнегі келесі түрге ие болады:

КЕНЕСБАЕВА АЙДАНА

№10 ЕМТИХАН БИЛЕТІІ

1.Тізбектелінген логикалық (қисындық) сұлбалар.

2.Триггерлерді кластарға бөлу.

Триггер – кіріс сигналдарының көмегімен бір күйден екінші күйге өтуге, екі мүмкін күйдің бірінде бола алатын қарапайым тізбектей құрылғы. Триггер тізбектес логикалық құрылғылардың базалық элементі болып табылады. Триггердің кірістері ақпараттық және басқару (қосымша) болып бөлінеді. Ақпараттық кірістер триггердің күйін басқару үшін қолданылады. Басқару құрылғылары әдетте триггерлерді кейбір күйге алдын ала құруға және синхронизациялауға қолданылады.

Триггерлердің екі шығыстары болуы мүмкін: тура және инверсті.

Триггерлерді әртүрлі белгілері бойынша классификациялайды, сондықтан классификацияның көптеген түрлері бар. Өкінішке орай, бұл классификациялар белгіленген жүйені құрмайды, бірақ инженерлер оны білуі тиіс.

Триггерлерді келесі белгілері бойынша классификациялайды:

• Ақпаратты қабылдау әдісі бойынша;

• Құрылу принципі бойынша;

• Функционалды мүмкіндіктері бойынша.

Триггерлерді асинхронды және синхронды деп ажыратады.

Асинхронды триггер ақпаратты сигнал шыққан сәтте өзінің күйін өзгертеді.

Синхронды триггер С (ағылшын тілінен алғанда clock)синхронизациясының кірісіндегі сигналға сай ақпаратты сигналдармен реакцияға түседі.

Синхронды триггерлер өз кезегінде С синхронизациясы кірісінің статикалық және динамикалық басқару триггерлеріне бөлінеді.

Статикалық триггерлер ақпараттық сигналдарды С логикалық бірлігі (тура кіріс) немесе логикалық нөл кірісінде (инверсті кіріс) қабылдайды.

Динамикалық триггерлер ақпараттықт сигналдарды С кірісіндегі сигналдардың 0-ден 1-ге (тура динамикалық С-кіріс) немесе 1-ден 0-ге (инверсті динамикалық С-кіріс) өзгерген кезде қабылдайды.

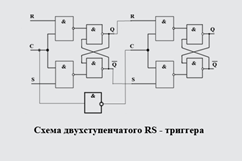

Динамикалық триггерлер өз кезегінде бірсатылы (біртактілі) және екісатылы (екітактілі) болып бөлінеді. Бірсатылы триггерде ақпаратты сақтайтын бір саты, ал екісатылықта – осындай екі саты бар. Алдымен ақпарат бірінші сатыға жазылады, содан кейін екіншісіне қайта жазылады да, шығысында көрінеді. Екісатылы триггерді ТТ арқылы белгілейді.

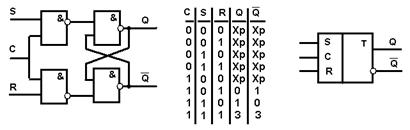

3.Тактіленген триггерлер түрлері.

Триггер деп - бiр бит мәндi сақтауға қабiлеттi, логикалық құрылғы. Ол екi тұрақты күйi бар және сатылы типтi қарапайым құрылғы.

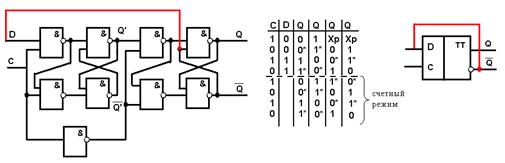

Тактіленетін RS-триггер (сур.8.3) өз жағдайын С кірісіне тактілік импульс келгенде ғана өзгерте алады. Тактілік импульстар арасындағы R және S ақпараттық кірісіне әсер етуші бөгеттер, триггер жұмысына әсерін тигізбейді. Рұқсат етілмейтін жағдай CRS=1 болып табылады .

Сур.8.3. Тактіленетін RS-триггер

Қорек көзін қосқан кезде триггер жағдайы анықталмаған күйде қалады (Q шығысындағы үзік сызық). S және C кірісіндегі бірлік деңгейлер сәйкес келгеннен кейін триггер бірлік жағдайда құрылады..

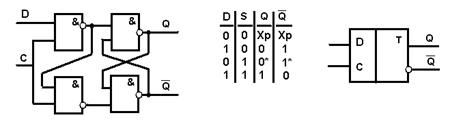

D-триггердің бір ақпаратты (D) және тактіленетін(С) кірісі бар (сур.8.4). С=1 кезінде ол қайталағыш ретінде жұмыс істейді (Q=D). С=0 ауысу кезінде триггер жабылып және сақтау режиміне ауысады (D кірісіне ақпаратты алады).Бұндай триггерлер жөнінде,ол тактілі импульстің тұрақты деңгейімен тактіленеді деп айтады.

Сур.8.4

Тактілі импулсьтің тұрақты фронтымен тактіленетін D-триггер (сур.8.5), алдыңғыдан айырмашылығы динамикалық тактілі кірісті триггер деп айтады.

Сур.8.5

С=0 кезінде бірінші саты триггері D сигналын қайталайды, екінші саты триггері жабық. Тактілі импулсьтің тұрақты фронтымен тактіленетін D-триггер (сур.8.5), алдыңғыдан айырмашылығы динамикалық тактілі кірісті триггер деп айтады.

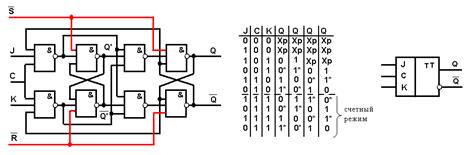

Жұп немесе Т-триггер (сур.8.6) Т жұп кірісіне әр импульс келуімен, ол жағдайын қарама-қарсы өзгертеді. Ол динамикалық кірісті RS- және D-триггер базасында құрылады.

Сур.8.6

Көбінесе әмбебап функцияны JK-триггер орындайды (сур.8.7). Ол динамикалық кірісті RS-триггер базасында құрылады, бірақ одан айырмашылығы J және K ақпаратты кірісінде логикалық бірлік сәйкес келгенде,жұп сияқты жұмыс істейді.

Сур.8.7

Синхронды триггерлердің ауысу функциялары:

Сур.8.8. RS- және JK-триггерлер жағдайының кестесі

Тактіленетіндермен қатар, көптеген триггерлік құрылғының микросұлбаларының бірлік және нөлдік жағдайға алдын ала құру үшін, асинхронды кірістері бар (сур.8.9).

Рис.8.9

11-Емтихан билеті

1-сұрақ

Триггер – ЭЕМ-нің функционалды түйіні, жады элементтерін және оларды басқару сұлбасын қамтыйды.

Триггерлердің жіктелуі:

1. сигналдардың келіп түсу уақыты бойынша:

- асинхронды;

- синхронды:

· біртактылы: бірсатылы, екісатылы;

· көпсатылы.

2. базисі бойынша :

- ЖӘНЕ-ЕМЕС;

- НЕМЕСЕ-ЕМЕС;

- аралас базисте.

3. типтері бойынша: RS, D, JK, T, DV, DT, RST және т.б.

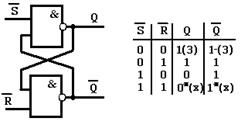

Асинхронды триггер.

Тек RS-типті.

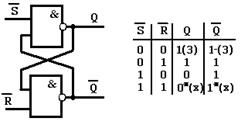

2.6 – сурет. ЖӘНЕ-ЕМЕС базисіндегі асинхронды RS-триггер

2.7 – сурет. НЕМЕСЕ-ЕМЕС базисіндегі асинхронды RS-триггер

Синхронды триггерлер.

Синхронды біртактылы бірсатылы триггерлер.

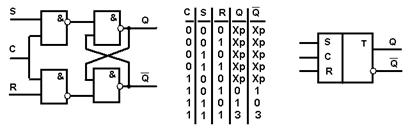

2.8 – сурет. ЖӘНЕ-ЕМЕС базисіндегі синхронды RS-триггер

2.9 – сурет. ЖӘНЕ-ЕМЕС базисіндегі D-триггер

Синхронды біртактылы екісатылы триггерлер.

|

2.10 – сурет. Тыйым салынған байланысты сұлба бойынша құрастырылған, ЖӘНЕ-ЕМЕС базисіндегі JK-триггер

|

2.11 – сурет. Терістеушіні қамтитын сұлба бойынша құрылған, ЖӘНЕ-ЕМЕС базисіндегі D-триггер

Атында V – типті әріпі бар триггерлер V атты қосымша синхрокірісті қамтыйды. Триггерлер RST, DvT: аралас функцияларды орындайды.

RST – RS және T-триггерлердің қызметтерін орындай алады,

DvT – V қосымша синхрокіріске ие, D және T-триггерлердің қызметтерін атқара алады.

2-сұрақ

Триггер – ЭЕМ-нің функционалды түйіні, жады элементтерін және оларды басқару сұлбасын қамтыйды.

Асинхронды триггер.

Тек RS-типті.

2.6 – сурет. ЖӘНЕ-ЕМЕС базисіндегі асинхронды RS-триггер

2.7 – сурет. НЕМЕСЕ-ЕМЕС базисіндегі асинхронды RS-триггер

Синхронды триггерлер.

Синхронды біртактылы бірсатылы триггерлер.

2.8 – сурет. ЖӘНЕ-ЕМЕС базисіндегі синхронды RS-триггер

3-сұрақ

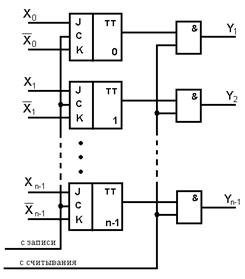

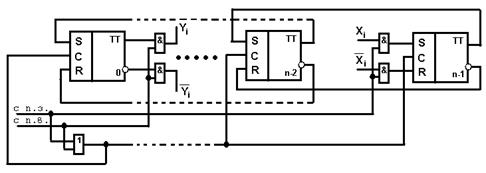

Регистрлер.

Регистр – ЭЕМ функционалды түйіні, ақпараттың n-разрядты сөзін жазу, сақтау және оқуға арналған. Регистрлер біртактылы немесе екітактылы екісатылы триггерлерде құрылады. Қосымша регистрлер ақпаратты түрлі модификацияларда жылжытуға мүмкіндік береді.

Сондай-ақ, регистрлерде  сияқты логикалық операцияларды орындап, ақпаратты разрядтардың берілген санына жылжытуға болады.

сияқты логикалық операцияларды орындап, ақпаратты разрядтардың берілген санына жылжытуға болады.

Жіктелуі:

1. жазу-оқу тәсілдері бойынша регистрлер мынадай түрлерге жіктеледі:

- тізбекті – тізбектей жазады және ақпаратты оқиды;

- параллельді – параллельді жазу, ақпаратты параллельді оқумен ерекшеленеді;

- тізбекті-параллельді – тізбекті жазумен және ақпаратты параллельді оқумен ерекшеленеді;

- параллельді-тізбекті – ақпаратты параллельді жазумен және тізбектей оқумен ерекшеленеді;

- әмбебап – параллельді және тізбекті жазумен және параллельді және тізбекті оқумен ерекшеленеді.

2. келіп түсетін және жіберілетін ақпараттардың фазалығы бойынша:

- бірфазалық – D-триггерлерде;

- жұпфазалық – RS және JK-триггерлерінде;

- аралас:

· бір фазалы енгізу, қосфазалы шығару;

· қосфазалы енгізу, бірфазалы шығару.

3. тактылау тәсілі бойынша:

- біртактылы – тактылық сигналдардың бір тізбегімен басқарылады;

- көптактылы – тактылық сигналдардың бірнеше тізбегімен басқарылады.

Базалық сұлбасы:

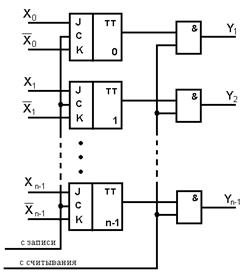

1. Ақпаратты қос фазалы енгізетін және бірфазалы шығаратын (оқитын) JK-триггеріндегі параллельді регистр. Ақпаратты қосфазалы шығару мүмкіндігі де бар.

2.12 – сурет. JK-триггеріндегі параллельді регистр

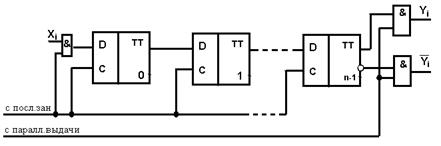

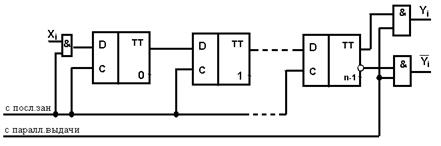

2. Ақпаратты солдан оңға бір фазалы енгізетін және қос фазалы шығаратын D-триггеріндегі тізбекті регистрлер.

2.13 – сурет. D-триггеріндегі тізбекті регистр

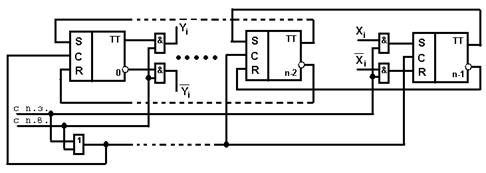

Ақпаратты солдан оңға қос фазалы енгізетін және бір фазалы шығаратын RS- триггеріндегі тізбекті регистрлер.

2.14 – сурет. RS-триггеріндегі тізбекті регистр

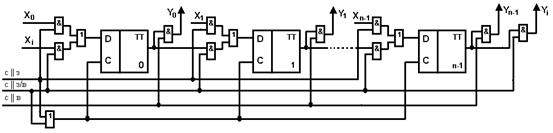

3. Әмбебап, бірфазалы тізбекті D-триггеріндегі регистр, ақпаратты солдан оңға және параллель енгізеді, оқу тізбектей және параллельді жүреді (бір фазамен).

2.15 – сурет. D-триггеріндегі әмбебап регистр

12 - Емтихан билеті

1.Тактіленетін RS-триггер

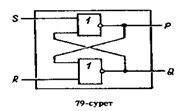

Бір бит информацияны зердеде сақтайтын электрондық схема триггер деп аталады.

Оның RS-триггер деп аталатын қарапайым түрін қарастырамыз (79-сурет).

Егер осы триггердің кірістеріне S=1, R = 0 беретія болсақ, онда (Q-дің күйіне тәуелсіз) жоғарғы вентильдің шығысында 0 шығады. Осыдан кейін төменгі вентильдің кірісінде R = 0, Р = 0 болып шығады да, Q шығысы 1-ге тең болады.

Егер енді триггерге сигнал беруді тоқтататын болсақ (S = 0, R = 0), онда жогарғы вентильдің кірістерінің мәндері S=0 және Q=1 болатындықтан, оның Р шығысы 0 болып қалады. Осы сияқты, төменгі вентильдің кірістері R= 0 және Р=0 болғандықтан, Q шығысы бұрынғысынша 1 болады. Сонымен, S = 0, R=0 мәндері ауысу кезінде Р және Q шығыстарының тағайындалған мәндері өзгермейді.

Дәл осылайша, кірістерге S=0, R=1 мәндерін берген кезде де шығыстарда Q = 0, Р = 1 мәндері пайда болады және R (R = 0, S = 0) кірісінен «1»-ді алып тастаған кезде де шығыстардың осы мәндері өзгермейді.

Сонымен, S = 0, R = 0 мәндеріңде триггер: Q = 1 және Q = 0 екі күйде бола алады. Олай болса, Q шығысы биттін есте сақталған мәні болып табылады.

| Кіріс S | Кіріс R | Триггердің әрекеті | Шығыс Q |

| есте сақтау 1 есте сақтау 0 битгі сақтау | есте сақталған бит |

Бір триггер бір-ақ битті есте сақтай алатындықтан, байтты (8 бит) есте сақтау үшін 8 триггер, килобайтты есте сақтау үшін 1024*8 = 8192 триггер және т. с. с. керек. Зерденің көлемі 1 см3-ден кем қазіргі микросхемалар миллион бит информацияны есте сақтайтьш қабілеті бар

2.Регистрлер.

Регистр – ЭЕМ функционалды түйіні, ақпараттың n-разрядты сөзін жазу, сақтау және оқуға арналған. Регистрлер біртактылы немесе екітактылы екісатылы триггерлерде құрылады. Қосымша регистрлер ақпаратты түрлі модификацияларда жылжытуға мүмкіндік береді.

Сондай-ақ, регистрлерде  сияқты логикалық операцияларды орындап, ақпаратты разрядтардың берілген санына жылжытуға болады.

сияқты логикалық операцияларды орындап, ақпаратты разрядтардың берілген санына жылжытуға болады.

Жіктелуі:

4. жазу-оқу тәсілдері бойынша регистрлер мынадай түрлерге жіктеледі:

- тізбекті – тізбектей жазады және ақпаратты оқиды;

- параллельді – параллельді жазу, ақпаратты параллельді оқумен ерекшеленеді;

- тізбекті-параллельді – тізбекті жазумен және ақпаратты параллельді оқумен ерекшеленеді;

- параллельді-тізбекті – ақпаратты параллельді жазумен және тізбектей оқумен ерекшеленеді;

- әмбебап – параллельді және тізбекті жазумен және параллельді және тізбекті оқумен ерекшеленеді.

5. келіп түсетін және жіберілетін ақпараттардың фазалығы бойынша:

- бірфазалық – D-триггерлерде;

- жұпфазалық – RS және JK-триггерлерінде;

- аралас:

· бір фазалы енгізу, қосфазалы шығару;

· қосфазалы енгізу, бірфазалы шығару.

6. тактылау тәсілі бойынша:

- біртактылы – тактылық сигналдардың бір тізбегімен басқарылады;

- көптактылы – тактылық сигналдардың бірнеше тізбегімен басқарылады.

Базалық сұлбасы:

1. Ақпаратты қос фазалы енгізетін және бірфазалы шығаратын (оқитын) JK-триггеріндегі параллельді регистр. Ақпаратты қосфазалы шығару мүмкіндігі де бар.

2.12 – сурет. JK-триггеріндегі параллельді регистр

2. Ақпаратты солдан оңға бір фазалы енгізетін және қос фазалы шығаратын D-триггеріндегі тізбекті регистрлер.

2.13 – сурет. D-триггеріндегі тізбекті регистр

Ақпаратты солдан оңға қос фазалы енгізетін және бір фазалы шығаратын RS- триггеріндегі тізбекті регистрлер.

2.14 – сурет. RS-триггеріндегі тізбекті регистр

3. Әмбебап, бірфазалы тізбекті D-триггеріндегі регистр, ақпаратты солдан оңға және параллель енгізеді, оқу тізбектей және параллельді жүреді (бір фазамен).

3,Қозғау регистрлер.

Регисторлардың екі түрі, сандық ақпаратты сақтауға арналған жады регистрі және сақтаумен бірге ақпаратты оңға немесе солға қозғай алатын, бірнеше тактіге кешіктіре алатын, сатылы екілік кодты параллельдіге және керсінше түрлендіре алатын қозғау регистірі болып жіктеледі.

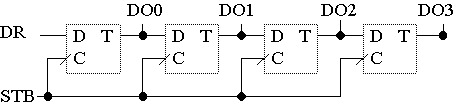

Рис 9.1

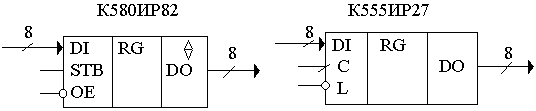

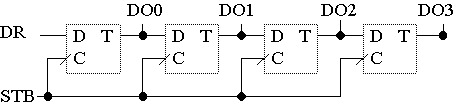

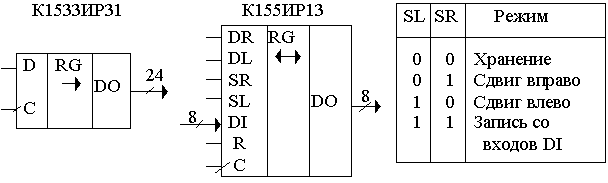

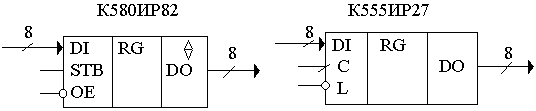

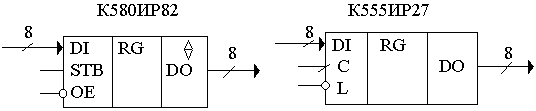

Қозғау регистрі динамикалық кірісті D-триггерінде құрылады. Мысалға, сегізразрядты жады регистрінің микросұлбасы тұрақты деңгеймен (К580ИР82) тактіленеді және тактілі импульстің (К555ИР27) фронтмен (сур.9.1). Ақпаратты оң жақ микросұлбаға жазу тек L кірісінің логикалық нөлінде С тұрақты фронтында болады.

Рис.9.2

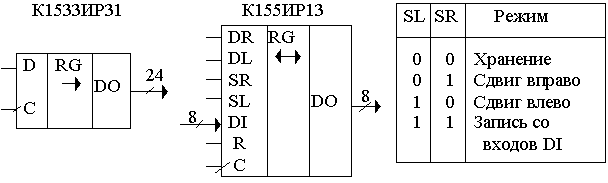

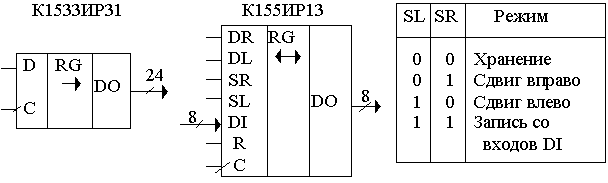

Қозғау регистрінің микросұлбасының ішінде(сур.9.3), мысалға К155ИР13 әмбебап регистр болып табылады. Жады регистрі көбінесе D-триггерінде, олардың тактілерін біріктіре отырып құрады. Мысалға, сегізразрядты жады регистрінің микросұлбасы тұрақты деңгеймен (К580ИР82) тактіленеді және тактілі импульстің (К555ИР27) фронтмен (сур.9.1). Бірінші микросұлба шығысынан сақталған мәліметтер ОЕ кірісінің логикалық нөлде оқылады.

Рис. 9.3

. 13-Емтихан билеті

1 сұрақ. Бірсатылы триггерлердегі қозғалыс резистрлері.

Регисторлардың екі түрі, сандық ақпаратты сақтауға арналған жады регистрі және сақтаумен бірге ақпаратты оңға немесе солға қозғай алатын, бірнеше тактіге кешіктіре алатын, сатылы екілік кодты параллельдіге және керсінше түрлендіре алатын қозғау регистірі болып жіктеледі.

Рис 9.1

Қозғау регистрі динамикалық кірісті D-триггерінде құрылады. Мысалға, сегізразрядты жады регистрінің микросұлбасы тұрақты деңгеймен (К580ИР82) тактіленеді және тактілі импульстің (К555ИР27) фронтмен (сур.9.1). Ақпаратты оң жақ микросұлбаға жазу тек L кірісінің логикалық нөлінде С тұрақты фронтында болады.

Рис.9.2

Қозғау регистрінің микросұлбасының ішінде(сур.9.3), мысалға К155ИР13 әмбебап регистр болып табылады. Жады регистрі көбінесе D-триггерінде, олардың тактілерін біріктіре отырып құрады. Мысалға, сегізразрядты жады регистрінің микросұлбасы тұрақты деңгеймен (К580ИР82) тактіленеді және тактілі импульстің (К555ИР27) фронтмен (сур.9.1). Бірінші микросұлба шығысынан сақталған мәліметтер ОЕ кірісінің логикалық нөлде оқылады.

Рис. 9.3

2-сұрақ. Мультиплексорлар, жұмыс принципі.

Мультиплексор деп бірнеше кіріс арналары бойынша бір шығысқа келіп түсіп, басқарылатын ақпарат берілуі үшін арналған комбинациялық құрылғы. Ақпараттық кірістерден басқа мультиплексорда адрестік (басқарушы) және мультиплексор жұмысына рұқсат беретін стробирлау кірістері болады. Адрестік кірістердегі сигналдар ақпараттық кірістердің қайсы сол мезетте шығысқа қосулы екенін анықтайды. Әдетте ақпараттық кірістер саны m-мен адрестік кірістер саны n арасында мынадай қатынаста болады, m = 2n.

Мультиплексор – ЭЕМ функционалды түйіні, m –кірістердің бірінен n –разрядты кіріс сигналын n – разрядты шығысқа коммутациялауға арналған.

Мультиплексор есептеу машинасында қолданылады, мысалы, ақпараттың қандай көзінен ақпарат процессор кірісіне келіп түседі, саны анықтайды (ақпарат көзі – процессордың қызмет етуші регистрлері, L1 деңгейлі КЭШ жады, жедел жады, винчестер, сыртқы ЕСҚ және т.б.)

3 разрядтан 2 каналды мултьтиплексордың базалық сұлбасы:

2.24 – сурет. 3 разряд бойынша 2 каналды мультиплексор

мұндағы A0 – мекендік шина, егер

A0 = 0 (яғни  =1), онда ақпарат 0-ші каналдан қабылдайды;

=1), онда ақпарат 0-ші каналдан қабылдайды;

A0 = 1 (яғни  =0), онда ақпарат 1-ші каналдан қабылдайды.

=0), онда ақпарат 1-ші каналдан қабылдайды.

Xij – ақпарат арналары.

3-сұрақ. Эмиттерлі байланысқан логика – ЭСЛ сұлбалары.

ЭСЛ элементтерінің негізгі қасиеті мыналар: өте жоғары жылдамдық, үлкен жүктемлік қабілет, жұмыс температурасы мен қоректену кернеуі өзгергендегі динамикалық параметрлерінің жоғары тұрақтылығы, төмен онда келісілген желі мен жүктемеде жұмыс істеу қабілеті, салыстырмалы жақсы бөгеуілге тұрақтылық.

Жасалған сандық ЭСЛ ИС-ң ішінде К500 және К1500 сериялы микросұлбалар кең таралады, бұлар МС 10000 мен Ғ100К микросұлбаларының функционалдық аналогы.

К500 сериялы микросұлба істік шығыста пластмасслық және керамикалық қорапта шығарылады, ал К1500 сериялы микросұлба негізінен керамикалық қорапта шығыстары планарлы болып дайындалады. Сурет1 көрсетілген К500 сериялы базалық ЭСЛ элементі үш бөліктен құралады: токтық ауыстырғыш (ТА), шығыс эмиттерлік қайталағыштар (ЭҚ) және тірек кернеуінің көзі тізбегі (ТКК).

Негізінде ЭСЛ элементтерінің екі не үш кірісі бар. Кіріс санын көбейту кіріс паразисттік сиымдылығын өсіреді, бұл жылдамдықты төмендетеді.

ТА - Т0, Т1 және Т2 транзисторларында RЭ, RК1 және RК2 резисторларында тұрғызылған. ТА-ң негізінен кілттік режимде жұмыс істейтін дифференциалдық күшейткіш құрайды, бұл кезде Т0, Т1 и Т2 транзисторлары қанығу режимінде енеді. ТА кіріс сигналдарын күшейтеді, элементтің қажетті бөгеуіл тұрақтылықпен қамтамасыз етеді,

А)токтық кілттің схемасы, Б) ЭСЛ базасының элементі.

А)токтық кілттің схемасы, Б) ЭСЛ базасының элементі.

№14 Емтихан билетіі

1. ЭСЛ базалық сұлбасының жұмыс істеу қағидасы

ЭСЛ технологиясы

ЭСЛ технологиясы ТТЛ технологиясы сияқты биполярлы, яғни элементтері биполярлы құрылымдардан жасалады. ЭСЛ элементтерінің негізі «ток ауыстырғышы» деп аталады, Немесе-Емес (3-сурет); 1-шығысында логикалық НЕМЕСЕ-ЕМЕС, ал 2-шығысында – НЕМЕСЕ логикалық функциясы бар.

ЭСЛ схемаларының кіріс кедергісі төмен болғандықтан жылдамдықтары жоғары және активті режимде жұмыс істейді, кіріске түскен бөгеттер күшейеді. Бөгеуіл төзімділігін жоғарылату үшін коллекторлы қорек көзінің шинасын жуан жасайды және жалпы шинамен байланыстырады.

3-сурет - ЭСЛ базалық элементі

ТТЛ схемаларымен салыстырғанда ЭСЛ схемалары жоғары жылдамдықта, бірақ бөгеуіл төзімділіктері төмен. ЭСЛ схемалары кристалда көп орын алады, көп қуат қолданып шығыс транзисторы ашылып үлкен ток жүреді. Осы технология бойынша жасалған схемалар оң кернеулі қорек көзін пайдаланатын басқа технология схемаларымен өзара байланыспайды.

2. МДП-тің логикалық (қисындық) элементтері

пМДП технологиясы

пМДП технологисының жоғарыда қарастырылған технологиялардан айырмашылығы олар МДП транзисторларына негізделген, биполярлы құрылымдарға қарағанда мынадай жетістіктерге ие болады:

- кіріс тізбегі (затвор тізбегі) статикалық режимде ток қолданбайды (жоғары кіріс кедергісі бар);

- өндірістің қарапайым технологиясы және кристалдағы алатын орны аз.

пМДП негізінде жасалған негізгі логикалық схемалар НЕМЕСЕ-НЕ, ЖӘНЕ-ЕМЕС (4-5сурет).

4-сурет. НЕМЕСЕ-ЕМЕС схемасы 5-сурет. ЖӘНЕ-ЕМЕС схемасы

Бұл схема кемшіліктеріне ТТЛШ және ЭСЛ схемаларымен салыстырғандағы аз жылдамдығы жатады.

3. Қозғау регистрлері

Регисторлардың екі түрі, сандық ақпаратты сақтауға арналған жады регистрі және сақтаумен бірге ақпаратты оңға немесе солға қозғай алатын, бірнеше тактіге кешіктіре алатын, сатылы екілік кодты параллельдіге және керсінше түрлендіре алатын қозғау регистірі болып жіктеледі.

Рис 9.1

Қозғау регистрі динамикалық кірісті D-триггерінде құрылады. Мысалға, сегізразрядты жады регистрінің микросұлбасы тұрақты деңгеймен (К580ИР82) тактіленеді және тактілі импульстің (К555ИР27) фронтмен (сур.9.1). Ақпаратты оң жақ микросұлбаға жазу тек L кірісінің логикалық нөлінде С тұрақты фронтында болады.

Рис.9.2

Қозғау регистрінің микросұлбасының ішінде(сур.9.3), мысалға К155ИР13 әмбебап регистр болып табылады. Жады регистрі көбінесе D-триггерінде, олардың тактілерін біріктіре отырып құрады. Мысалға, сегізразрядты жады регистрінің микросұлбасы тұрақты деңгеймен (К580ИР82) тактіленеді және тактілі импульстің (К555ИР27) фронтмен (сур.9.1). Бірінші микросұлба шығысынан сақталған мәліметтер ОЕ кірісінің логикалық нөлде оқылады.

Рис. 9.3

№ 15 – Емтихан билеті

1. Екісатылы триггерлердегі қозғалыс регистрлері

Екісатылы триггерлер ақпаратты сақтайтын екі сатысы бар, тактілі импульспен басқарылады, ақпарат басында бірінші сатыға, ал сосын екінші сатыға қайта жазылып, триггердің шығысында пайда болады.

Екісатылы триггерлердің жадының екі ұяшығы болады, яғни ақпаратты жазу сәйкесінше әр түрлі уақытта жүзеге асады. Екісатылы триггерлерде регистр мастер-көмекші ретінде құрылған. Егер жазылудың кірісіне төменгі деңгейдегі кернеу сигналы берілсе, триггер-мастері кіріс міліметтерін қабылдайды. Мәліметтер көмекші-триггерлармен тактілі кірісіндегі оң түсуі кезінде тасымалданады.

Жұмыс істеу барысына қарай отырып екісатылы триггерін инверстік динамикалық басқару триггеріне ұқсатуға болады, әйтсе де екі сатысы статикалық басқаруға ие.

2. Есептеу құралдарының түрлері

Есептеу құралдары аналогты және сандық (цифрлық) деп бөлінеді.

Аналогты есептеу құралдары – бұлар сигналдарды күшейтуге, түрлендіруге және өңдеуге арналған құрылғылар, яғни үзіліссіз функцияға негізделеді. Аналогты құрылғылардың артықшылықтары ( салыстырмалы түрде қарапайымдылығы, сенімділігі және шапшаңдығы) оның кеңінен қолданылуына септігін тигізді.

Сандық(цифрлық) құрылғылар импульстік сигналдарды екілік немесе қандай да бір код та өңдеуге құрылған.

3. Есептеу құралдарының түрлерінің негізгі параметрлері.

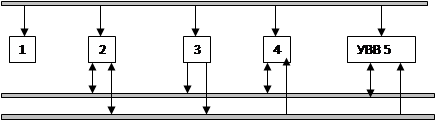

Бір не бірнеше микропроцессоры бар, басқарушы программаларды және интерфейстік сұлбаларды сақтайтын жады бар құрылғыны есептеу құралдары деп атайды. Есептеу құралдарының түрлері МикроЭВМ, калькулятор, компьютер.

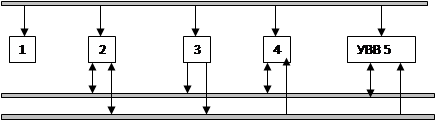

Мысалы МикроЭВМ-ді алсақ, интерфейстік сұлбалар МикроЭВМ-ді кіріс-шығыс құрылғыла-рымен байланыстырады. Аталған тораптар бір- бірімен магистарльдарсмен байланысқан. МикроЭВМнің негізгі құраушылары микропроцессор, программаларды сақтайтын тұрақты жады, оперативті жады, тактілік импульстер генераторы, басқару пульты және интерфейстік құрылғылар.

16-Емтихан билеті

1.Есептеу құралдарының түрлерінің негізгі параметрлері.

Бір не бірнеше микропроцессоры бар, басқарушы программаларды және интерфейстік сұлбаларды сақтайтын жады бар құрылғыны есептеу құралдары деп атайды. Есептеу құралдарының түрлері МикроЭВМ, калькулятор, компьютер.

Мысалы МикроЭВМ-ді алсақ, интерфейстік сұлбалар МикроЭВМ-ді кіріс-шығыс құрылғыла-рымен байланыстырады. Аталған тораптар бір- бірімен магистарльдарсмен байланысқан. МикроЭВМнің негізгі құраушылары микропроцессор, программаларды сақтайтын тұрақты жады, оперативті жады, тактілік импульстер генераторы, басқару пульты және интерфейстік құрылғылар

2,Қосындылайтын есептеу құралы.

Есептеу құралы — есептеу және мәліметтерді өңдеу процессінің маңызды компоненті болып табылады. Есептеуге арналған алғашқы құрал ретінде есептеу таяқшаларын атауға болады, бұл құрал қазіргі кезде де бастауыш сынып оқушыларын есепке үйрету үшін қолданылады. Даму жолында бұл құралдар күрделене түсті (мысалы, финикиялық саз фигуралары).