Выполнение лабораторной работы. Выполните исследование двухтактного синхронного триггера с асинхронной установкой и сбросом.

|

Выполните исследование двухтактного синхронного триггера с асинхронной установкой и сбросом.

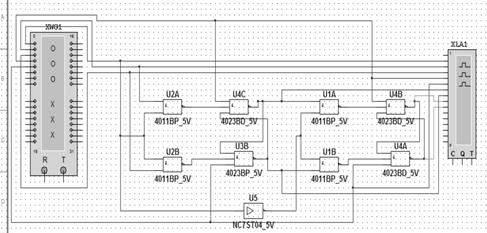

Соберите схему, приведенную на рис. 2.6. 3.

Рис. 2.6. 3. Исследуемая схема двухтактного триггера

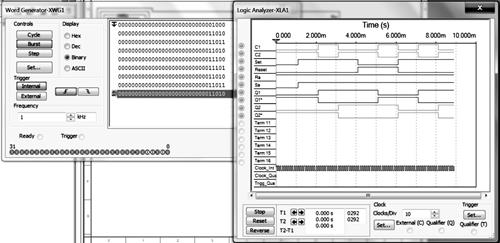

Запрограммируйте генератор слов для проведения эксперимента. В первой строке генератора слов обязательно задайте сигналы установки триггеров первой и второй ступени в «0» (рис. 2.6.4).

Рис. 2.6. 4. Программирование генератора слов и результаты моделирования

После первого шага оба триггера установлены в «0». Второй шаг – на Set установлена «1», на Reset – «0». Третий шаг – С1 = «1», первый триггер принимает информацию и по началу импульса синхронизации С1 переходит в состояние Q1 = «1». С2 принимает значение «0» – второй триггер хранит прежнюю информацию. Четвертый шаг – С1= «0», С2 = «1», второй триггер принимает информацию из первого триггера и по окончанию импульса синхронизации С1 переходит в состояние Q2 = «1».

Оформите отчет по лабораторной работе. Отчет должен содержать название работы, цель, основные определения, исследуемую схему, временные диаграммы с пояснением, выводы.

На основе RS – триггеров строятся схемы триггеров, применяемых для счета импульсов (Т – триггеры), для задержки импульсов (D – триггеры) и другие. Универсальный JK – триггер (в основе тоже RS – триггер) может работать в режиме любого из перечисленных выше триггеров.

Вопросы для подготовки к отчету:

1. Для чего в цифровых схемах используют двухтактные триггеры?

2. Как создать двухтактный триггер из 2-х однотактных?

3. Почему выходной триггер схемы переключается по срезу импульса синхронизации?

7. Лабораторная работа № 7

Исследование D-триггера

Цель работы: Изучить принципы функционирования однотактного и двухтактного D-тpиггepа.

Задание:Ознакомиться с теорией построения и работы D – тpиггepа. Провести исследование однотактного и двухтактного D – тpиггepа в программе Multisim.

Теоретическое введение

D-тpиггep, триггер задержки (Delay) имеет один информационный вход (D-вход) и вход управляющий задержкой выходного сигнала относительно входного (синхронизирующего импульс на входе С).

|

Основное назначение D – триггера – задержка сигнала, поданного на вход. Как и RS – триггер, он может быть построен на различных логических элементах (И-НЕ, ИЛИ-НЕ).

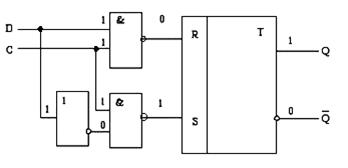

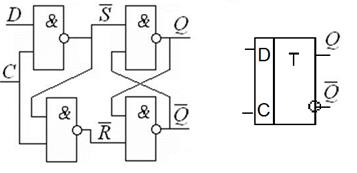

D – триггер легко построить на основе схемы асинхронного RS – триггера. (рис. 2.7.1).

Рис. 2.7.1. Схема однотактного D-триггера на основе RS-триггера

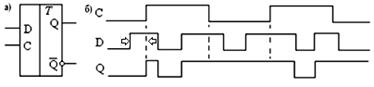

Обозначение на схемах и временные диаграммы работы D – триггера приведены на рис.27.2.

Рис. . 2.7.2. Временные диаграммы работы D-триггера

При С = «0» изменение входного сигнала не сказывается на состоянии триггера (режим хранения), и только при С = «1» триггер принимает состояние, определяемое входным сигналом D. На рисунке стрелочками выделено время задержки сигнала на выходе триггера относительно сигнала на D-входе.

Большее распространение получила схема D-триггера, приведенная на рис. 2.7.3.

Рис. 2.7.3. Однотактный D-триггер

В таблице 2.7.1. показаны состояния цифрового автомата при C = 1 в зависимости от управляющего сигнала D и предыдущего состояния триггера.

Таблица переходов D-триггера

Таблица 2.7.1.

| Qt | Dt | Q(t+1) |

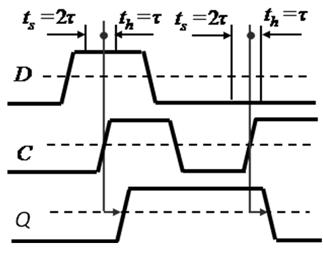

Временная диаграмма работы D-триггера приведена на рис.2.7. 4.

Рис. 2.7.4. Временная диаграмма работы D-триггера

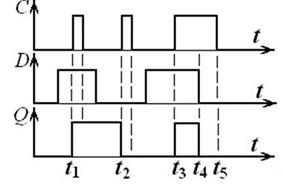

Разновидностью D – триггера является DV – триггер, который дополнительно к D – входу имеет управляющий V– вход (рис.2.7.5).

Рис. 2.7.5. DV-триггер, его обозначение и временная диаграмма

При V = «1» триггер работает аналогично D – триггеру, а при V = «0» сохраняет исходное состояние независимо от изменения сигнала на D- и С-входах.

D – триггер с динамическим управлением

Широкое применение в практике построения цифровых устройств находят D – триггеры с динамическим управлением (155TM2, 564ТМ2). Они реагируют на информационные сигналы только в момент изменения сигнала на С – входе от «0» к «1» (прямой динамический вход) или от «1» к «0» (инверсный динамический вход).

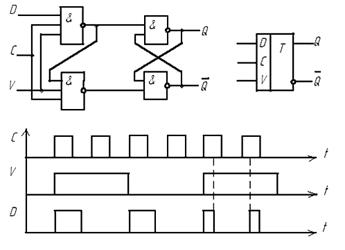

D – триггер с динамическим управлением конструируется из трех RS – триггеров асинхронного типа. Они построены на элементах И-НЕ, при этом два из них выполняют коммутирующую функцию, а третий является выходным. Выходные сигналы коммутирующих триггеров предназначены для управления выходным триггером. Внутренняя схема D – триггеров, примененных в микросхеме К155ТМ2 , содержит дополнительные асинхронные входы R* и S*. Они позволяют принудительно записывать в D – триггер логический ноль или логическую единицу. Принципиальная схема одного триггера микросхемы К155ТМ2 приведена на рисунке 2.7.6.

Рис. 2.7.6. D-триггер с динамическим управлением и его обозначение на схемах

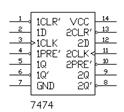

D – триггер ИС К155ТМ2 является аналогом триггера микросхемы SN7474, изображение которой в среде Multisim представлено на рис. 2.7.7.

Рис. 2.7.7. Микросхема SN7474

Микросхема SN 7474 содержит два независимых комбинированных D –триггера, имеющих общую цепь питания. У каждого триггера имеется один информационный вход D(1D, 2D), вход синхронизации CLK(1CLK, 2CLK) и два дополнительных входа 1PRE*, 2PRE* и 1CLR*, 2CLR* независимой асинхронной установки триггера в единичное и нулевое состояние, а также комплементарные выходы 1Q, 2Q и 1Q*, 2Q*.

Работа триггера микросхемы SN 7474 отражена в таблице переходов 2.7.2.

Таблица переходов (состояний) триггера SN 7474

Таблица 2.7.2.

| Режим работы | Входы | Выходы | ||||

| #PRE | #CLR | D | CLK | Q | #Q | |

| Асинхронная установка | х | х | ||||

| Асинхронный сброс | х | х | ||||

| Неопределенность (запрет) | х | х | ||||

| Загрузка «1» (установка) | ûé | |||||

| Загрузка «0» (сброс) | ûé |

Анализ работы схемы

1. При С= «0» сигналы X2 и X3 принимают значение X2=X3=«1» и выходной триггер Т3 (рис. 2.7.6) находится в режиме хранения, а Х1 = D*, X4 = X1* = D.

2. При положительном перепаде синхросигнала C(0→1) функционирование RS – триггеров Т1 Т2 и Т3при различных значениях входного сигнала D показано в таблице 2.7.3. Состоянием обычного асинхронного триггера Т3 управляют сигналы X2 (R*) и X3 (S*).

Функционирование RS-триггеров Т1 Т2 и Т3

Таблица 2.7.3.

| D(t) | C | Триггер Т1 | Триггер Т2 | Триггер Т3 Q(t+1) | ||

| X1 | X2 | X3 | X4 | |||

0 0 | Q(t) | |||||

| D*= 1 | C*= 0 | Хранение | ||||

1 1 | Q(t) | |||||

| Хранение | С*= 0 | X1* =1 | ||||

3. Анализ схемы при С=1.ПриС=1 триггер Т3 сохраняет своё состояние, так как блокируется от воздействия сигнала по D-входу. При С=1 выполняется условие: X2≠X3. Возможны 2 случая.

а) Пусть X2=0, X3=1. Тогда действие D-входа блокировано вентилем &1, а триггер Т3 будетнаходится в «0».

б) Пусть X2=1, X3=0. В этом случае вентиль &1 разблокирован, но значение сигнала X3=0 сохраняет значение X2=1 и блокирует действие D-входа по цепи &1 и &4.Триггер Т3 будет находится в состоянии «1».

4. Отрицательный перепад синхросигнала С(1→0)

При С«1→0» триггер Т3переходит в режим хранения, т.к. сигнал С=0 устанавливает X2=X3=1 (R*=S* =1).

Временная диаграмма работы динамического триггера показана

на рис. 2.7.8.

Рис. 2.7.8. Временная диаграмма работы динамического триггера

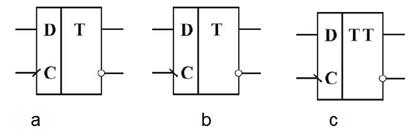

В применяемых в России условных обозначениях триггеров направление косой черты на входе C показывает, по какому фронту происходит срабатывание триггера: по переднему фронту – прямая косая черта, по заднему – обратная косая черта (рис. 2.7.9).

Триггеры, построенные по двухступенчатой схеме, предусматривают применение такого же способа обозначения синхронизирующего входа C, для того чтобы с помощью него показать, по какому фронту этого сигнала информация с выходов первичной ступени обработки передается во вторую ступень и поступает на его выходы

Понять различие в схемах помогает обозначение, уточняющее тип элемента — для одноступенчатого триггера предусматривается обозначение T, а для такого же двухступенчатого — TT.

Рис. 2.7.9. D-триггер с динамическим входом:

a) – управление передним фронтом импульса (фронт); b) – управление задним фронтом импульса (спад). с) – двухтактный триггер с переключением по спаду импульса.

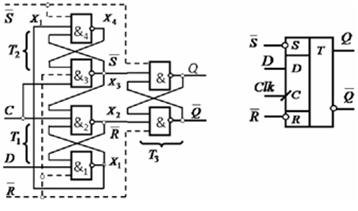

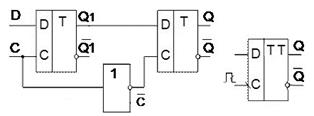

Двухтактный D-триггер

D-триггер, тактируемый фронтом, построен по схеме «мастер-помощник» на двух триггерах D1 и D2, тактируемых импульсом и одном инверторе D3 (рис. 2.7.10). Это двухтактный триггер. Из схемы видно, что информационный вход D второго триггера соединён с выходом Q1, то есть триггеры соединены последовательно. Триггер D1 «мастер» тактируется прямым уровнем синхросигнала, а «помощник» D2-инверсным. При C=1 информация с входа D записывается на выход Q1, триггер D2 при этом закрыт. При переходе тактового сигнала C из 1 в 0 на тактовом входе триггера D2 формируется сигнал С*=1, триггер D2 открывается и записывает на основной выход Q информацию с выхода Q1. Таким образом, двухступенчатый триггер тактируется задним фронтом сигнала C, что и отмечается косой чертой на входе С графического изображения триггера.

Рис. 2.7.10. Двухтактный D-триггер и его графическое изображение

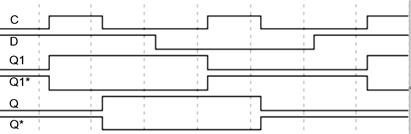

Временные диаграммы работы двухтактного D-триггера приведены на рис. 2.7.11.

Рис. 2.7.11. Временные диаграммы работы двухтактногоD-триггера