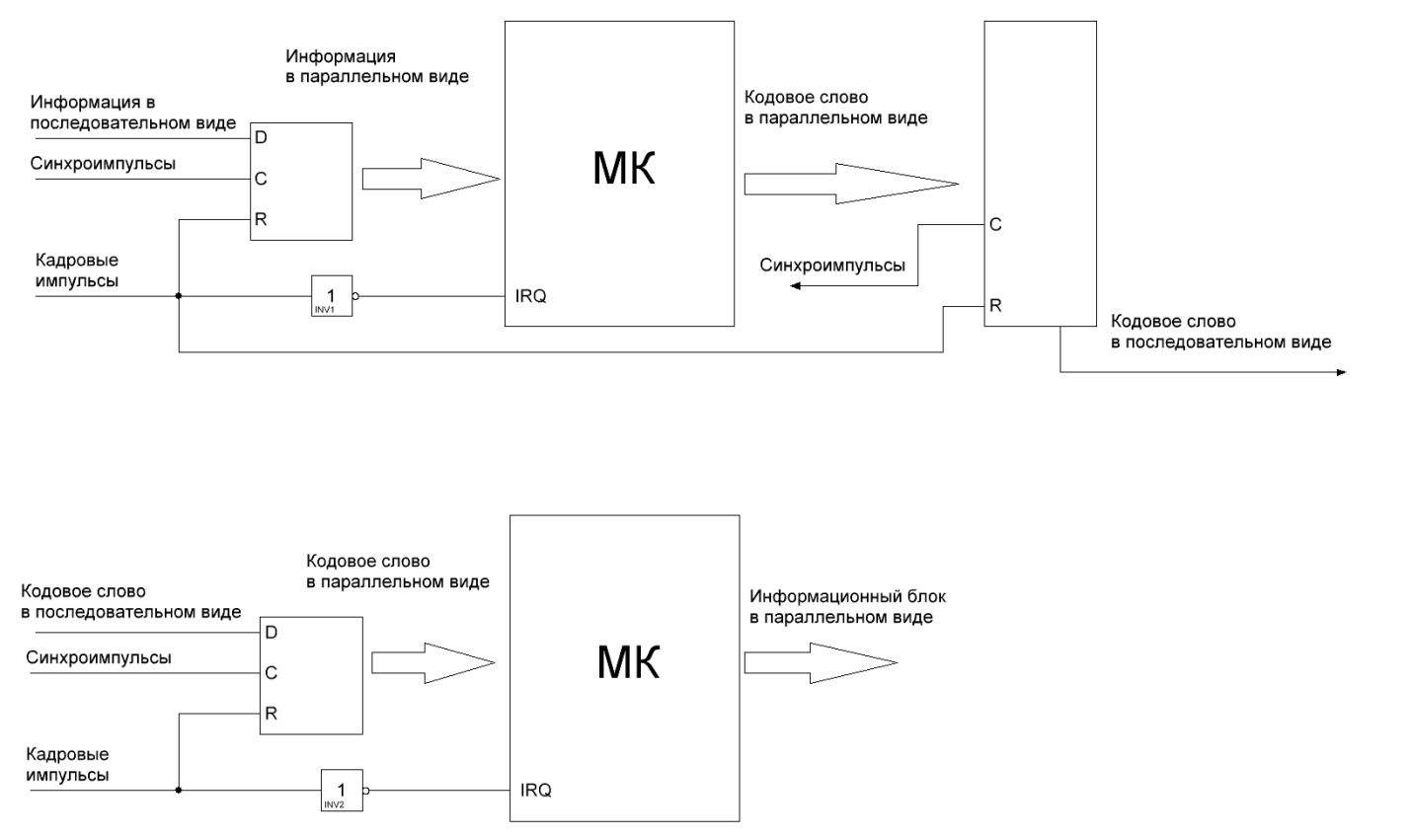

Структурная схема кодека

рис. 2

Структурная схема кодека, основанного на микроконтроллере M68HC11

Рассмотрим принцип кодирования информации.

Имеем информационный блок длиной 14 символов. Его размещаем в две однобайтовые ячейки:

| х | х | х | х | х | х |

| х | х | х | х | х | х | х | х |

Первые два старших бита оказываются не заняты, так что их обнуляем. Информация, пришедшая в последовательном виде как информационный блок, подается на вход двух 8-битных сдвиговых регистров, соединенных последовательно:

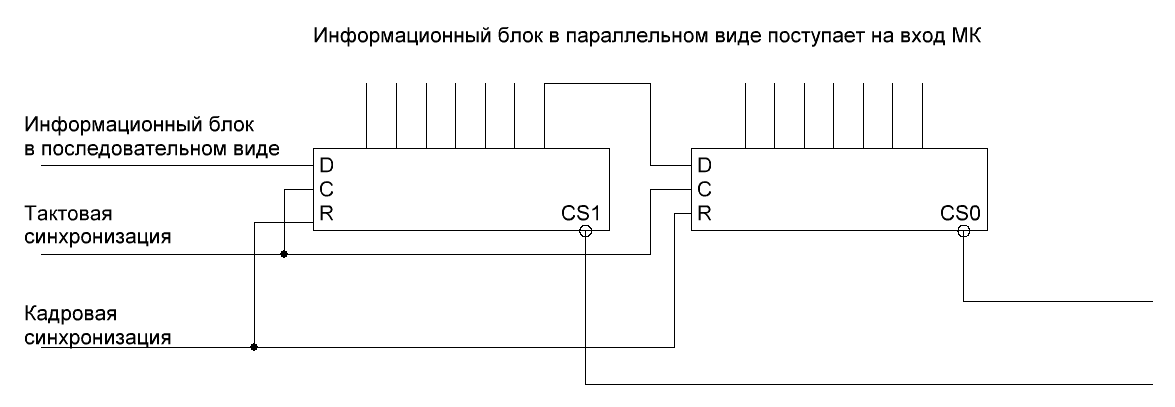

Рис.3 Принцип преобразования последовательных информационных блоков в параллельные

На входы С приходят тактовые импульсы, на входы R приходят импульсы синхронизации по кадрам (блокам). Когда оба регистра заполняются, они хранят в себе 16-разрядное слово, 14 разрядов которого – информационный блок, а два старших разряда – нули; в этот момент приходит импульс синхронизации по кадрам одновременно на микроконтроллер, который по этому запросу начинает считывать получившуюся информацию через два 8-разрядных параллельных порта, настроенных на ввод, а регистры обнуляются, и снова начинают заполняться вновь прибывающим словом.

Проверочные символы (k=7) размещаем в однобайтовую ячейку следующим образом:

| х | х | х | х | х | х | х |

После того, как мы получаем с помощью кодера проверочный блок, мы «присоединяем» его с помощью трех регистров сдвига к уже имеющемуся информационному блоку, и получаем кодовое слово в параллельном виде:

| x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x |

Информационный блок Проверочный блок

Полученную информацию нужно декодировать. Для этого берем кодовое слово, помещаем его опять в сдвиговые регистры с параллельной выгрузкой, синхронизированные с микроконтроллером, и загружаем в МК, уже в параллельном виде. После обработки на выходе МК получаем декодированный информационный блок в параллельном виде.

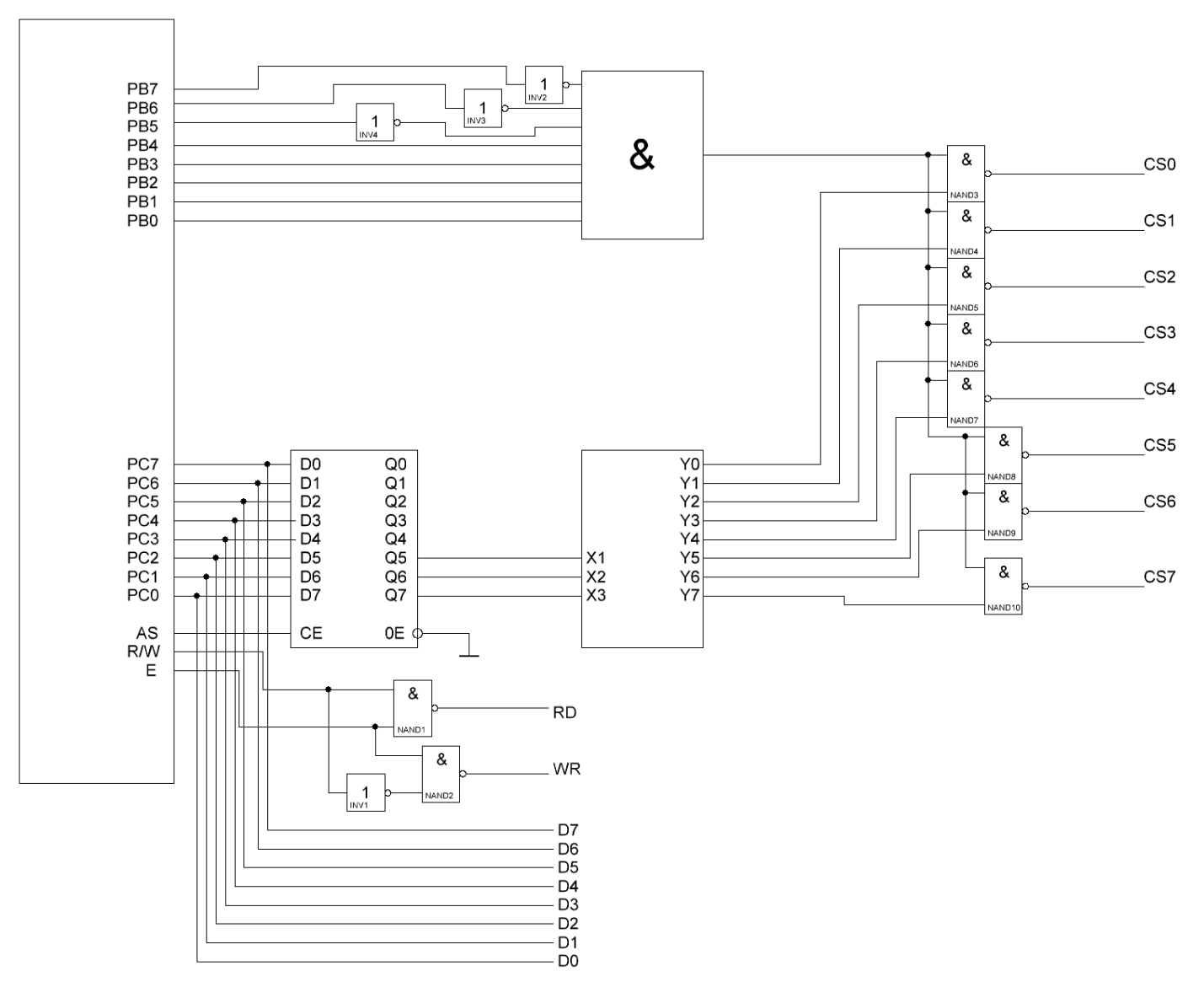

Чтобы реализовать кодек, потребуется 5 портов, работающих на ввод и 3, работающих на вывод: в кодере 2 – для ввода информационного блока, 1 – для вывода проверочного блока (информационный блок «присоединяется» к нему извне. В декодере 3 – для ввода кодового слова в последовательном виде и 2 – для вывода информационного блока в параллельном виде. Всего потребуется 8 портов. Выбранный микроконтроллер не обладает таким количеством портов, поэтому в данной работе будет использоваться специальная схема подключения внешних портов, показанная на рис.4

Рис.4 Реализация внешней магистрали адреса/данных микроконтроллера MC68HC11E1

Слева показана часть микроконтроллера MC68HC11E1 – порты B и C и выводы для разрешения чтения/записи данных через порт С в микроконтроллер.

Принцип работы данной магистрали состоит в следующем.

В МК программно задается один из незанятых адресов ОЗУ 1f00…1f07, т.е. всего 8, как и количество требуемых портов. Один такой адрес занимает 16 разрядов и поступает на выводы PB7…PB0 и PC7…PC0. На выводы порта В (PB7…PB0) поступает 1f, (т.е. 00011111 в двоичной форме). Старшие 3 разряда являются нулями; они через инверторы подаются на логический элемент 8И, остальные 5 разрядов поступают на него без инверторов, так как в диапазоне адресов 1f00…1f07 не изменяют своего значения. Выводы порта С подключаются к одному из 8-разрядных внешних портов, а также к регистру-«защелке», который нужен для компенсации «потери» портов В и С. Три вывода этого регистра, соответствующие младшим разрядам адреса (т.е. помеченным как «х» в 8 младших разрядах адресов 1f00…1f07 – 00000ххх в двоичной форме) подключены к дешифратору 3х8, выводы которого, в свою очередь, подключены вместе с выходом элемента 8И к элементам 2И-НЕ; их выходы подключаются к выводам выборки кристаллов CS внешних портов.

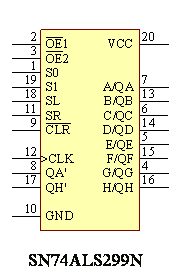

В качестве внешних портов удобно использовать универсальные регистры SN74ALS299N. Такой регистр изображен на рис.5.

Рис. 5 Универсальный регистр

Микросхема представляет собой универсальный восьмиразрядный сдвиговый регистр с выходом на три состояния и может применяться в качестве буферного запоминающего устройства, для преобразования данных из параллельной формы в последовательную и наоборот.

Возможны четыре режима работы.

1. Синхронная параллельная загрузка осуществляется путём подачи напряжения высокого уровня на управляющие входы S0, S1. На объединённые входы-выходы, находящиеся в состоянии высокого импеданса, подаётся восьмиразрядное слово, которое по положительному фронту импульса на входе СLK записывается в триггеры.

2. Сдвиг вправо осуществляется синхронного с приходом положительного фронта тактового импульса на входе СLK при установке на S0 высокого, а на S1 низкого уровней. В этом режиме данные последовательно считываются со входа SR.

3. Сдвиг влево осуществляется синхронного с приходом положительного фронта тактового импульса на СLK при установке на S1 высокого, а на S0 низкого уровней. В этом режиме данные последовательно считываются с выхода SL.

4. Режим блокировки реализуется при подаче на оба управляющих входа S0, S1напряжения низкого уровня.

Сброс выходов в состояние низкого уровня происходит асинхронно при подаче нуля на ~CLR. Напряжения высокого уровня на любом из входов ~OE1, ~OE2 переводит входы-выходы в состояние высокого импеданса, но не оказывает при этом влияния на режимы работы регистра.

Таблица установки режимов работы показана на рис.6.

| Режим | Вход | Вход-выход | Выход | |||||||||||||||

| ~ CLR | S0 | S1 | ~ OE1 | ~ OE2 | CLK | SL | SR | A/ QA | B/ QB | C/ QC | D/ QD | E/ QE | F/ QF | G/ QG | H/ QH | QA1 | QH1 | |

| Уста- новка | L | L | Х | L | L | Х | Х | Х | L | L | L | L | L | L | L | L | L | L |

| L | Х | L | L | L | Х | Х | Х | L | L | L | L | L | L | L | L | L | L | |

| L | H | H | Х | Х | Х | Х | Х | Х | Х | Х | Х | Х | Х | Х | Х | L | L | |

| Удер- жание | H | L | L | L | L | Х | Х | Х | D10 | D20 | D30 | D40 | D50 | D60 | D70 | D80 | D10 | D80 |

| H | X | X | L | L | L | X | X | D10 | D20 | D30 | D40 | D50 | D60 | D70 | D80 | D10 | D80 | |

| Сдвиг вправо | H | H | L | L | L | ↑ | X | H | H | D1n | D2n | D3n | D4n | D5n | D6n | D7n | H | D7n |

| H | H | L | L | L | ↑ | X | L | L | D1n | D2n | D3n | D4n | D5n | D6n | D7n | L | D7n | |

| Сдвиг влево | H | L | H | L | L | ↑ | H | X | D2n | D3n | D4n | D5n | D6n | D7n | D8n | H | D2n | H |

| H | L | H | L | L | ↑ | L | X | D2n | D3n | D4n | D5n | D6n | D7n | D8n | L | D2n | L | |

| Загруз- ка | H | H | H | X | X | ↑ | X | X | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D1 | D8 |

Рис.6 Таблица установки режимов работы универсального регистра SN74ALS299N

Нас будут интересовать режимы удержания (для считывания с порта) и загрузки (для записи в порт).

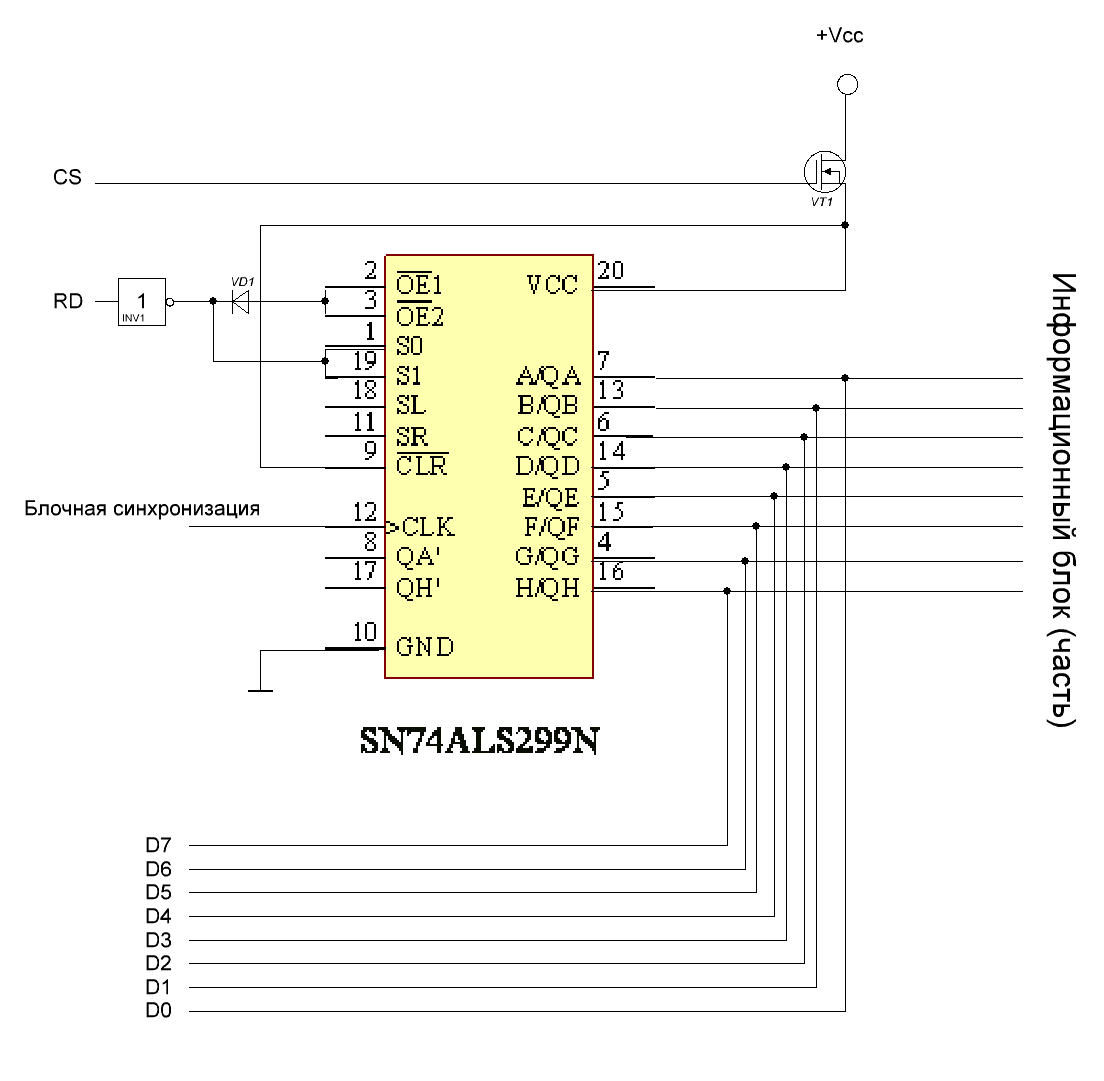

Рис. 7 Схема подключения одного внешнего порта ввода с помощью универсального регистра (кодер)

На рис. 7 показано подключение внешнего порта, работающего на ввод. Когда приходит импульс блочной синхронизации, часть информационного блока (8 разрядов) уже в параллельном виде (после сдвиговых регистров на входе) записывается в регистр, т.к. на CLK высокий уровень, на S0, S1 тоже. Когда МК переходит в режим чтения, на CLK – низкий уровень, т.к. блочный импульс ещё не пришел, а на входах OE1, OE2, S0, S1 – низкий уровень, т.е. регистр работает в режиме удержания до тех пор, пока не придет следующий импульс блочной синхронизации, и т.д.

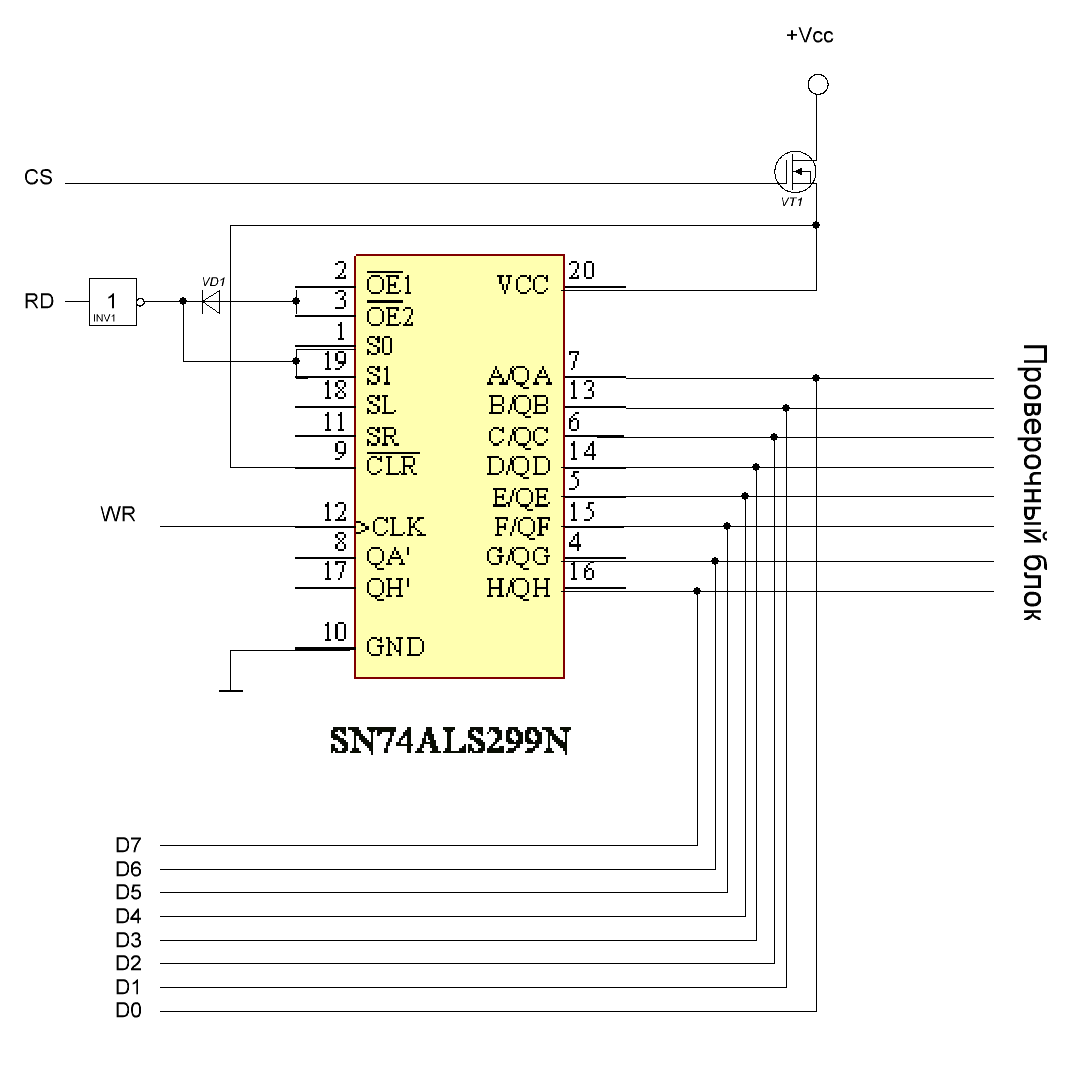

Рис. 8 Схема подключения внешнего порта вывода на примере кодера

На рис.8 показано подключение внешнего порта вывода. Когда МК переходит в режим записи, на выводе WR – высокий уровень, т.е. и на CLK. На выводе RD в это время – низкий уровень, поскольку WR и RD подключены зависят от одного и того же вывода R/W (см. рис. 4). На OE1 и OE2 из-за диода в это время режим высокоимпедансного состояния (Х). На S0, S1 – высокий уровень (из-за инвертора). Информация записывается в регистр, затем МК выходит из режима записи, и на входе CLK устанавливается низкий уровень, а на OE1, OE2, S0, S1 также устанавливается низкий уровень.

В обоих схемах на вход CS приходит сигнал выборки кристалла (низкий уровень), а транзистор (полевой, p-канальный) открывается и «разрешает» микросхеме питание.

Алгоритм чтения/записи такой:

Когда МК переходит в режим чтения с порта, адресами, которые выдает МК, решается, какой из 5 портов ввода подключить. Сигнал, зависящий от адреса, идет на один из выводов CS0-CS7.

Например, если нужно считать 16-разрядный информационный блок с помощью 8-разрядной шины D7…D0, происходит следующее:

По адресу 1f0(x) с помощью дешифратора и подключенной к нему обвязки (рис.4) сигнал низкого уровня идет на один из выводов CS0-CS7, что включает один из портов ввода (рис.7), на котором уже имеется считанная со сдвиговых регистров информация. МК переходит в режим чтения, считывает 8 старших разрядов информационного блока, сохраняет их в ОЗУ, затем выдает адрес 1f0(x+1), сигнал CS идет на следующий порт ввода, где лежит младшие 8 разрядов информационного блока, МК опять переходит в режим чтения, считывает эти 8 разрядов и сохраняет их в ОЗУ по другому адресу. После этого начинается обработка информационного блока внутри МК.

Когда МК считал и обработал информацию с внешних портов ввода, он выдает адреса портов вывода, регистр–защелка их запоминает, дешифратор дает активный уровень на одном из своих выводов, таким образом выбирая один из 3 портов вывода. После прихода высокого уровня на вывод WR информация отправляется на выбранный порт.