Моделирование телеуправления

Модели уровней сервиса связи

В указаниях рассматривается пример разработки программной эмуляции системы телемеханики в соответствии с моделью EPA. При этом приведенные решения должны рассматриваться лишь как возможный вариант приближенной и упрощенной реализации модели EPA. В задании на проект могут быть указаны дополнительные требования и ограничения на реализацию модели.

Физический уровень

Физический уровень обеспечивает передачу и прием битового потока. Этот уровень взаимодействует с канальным уровнем, от которого получает байты для передачи и которому передает байты, полученные из линии связи. Для телеуправления пункт управления передает приказы, которые воспринимаются контролируемыми пунктами. Рассмотрим отдельно физические уровни при работе на передачу и прием.

Физический уровень обеспечивает передачу и прием битового потока. Этот уровень взаимодействует с канальным уровнем, от которого получает байты для передачи и которому передает байты, полученные из линии связи. Для телеуправления пункт управления передает приказы, которые воспринимаются контролируемыми пунктами. Рассмотрим отдельно физические уровни при работе на передачу и прием.

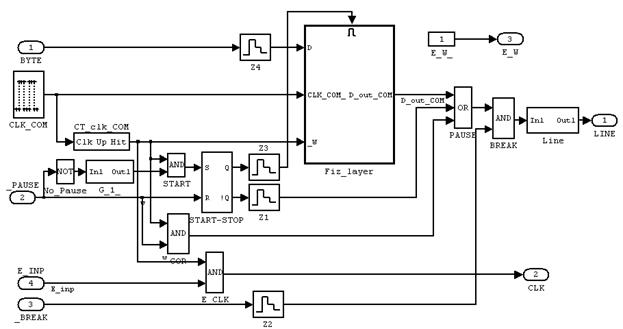

Физический уровень передающей станции. Канальный уровень поставляет физическому уровню последовательность байт, следующих друг за другом без пауз. После передачи кадра формируется пауза. Эта пауза используется для информирования приемной стороны об окончании кадра. Для организации указанной последовательности действий предположим, что сформированный кадр хранится в канальном уровне в очереди и канальный уровень извещает физический о готовности кадра. Выборка байтов кадра производится с частотой, определяемой физическим уровнем. При таких соглашениях физический уровень передающей станции может быть представлен в виде подсистемы, приведенной на рис. 29.

Входные порты: BYTE – байты данных канального уровня, _PAUSE – сигнал паузы, _BREAK – сигнал обрыв (вводится для тестирования приемной стороны), E_INP – разрешение от канального уровня на чтение информации (готовность кадра). Выходные порты: LINE – для выдачи бит в линию связи, CLK – синхросигнал чтения очередного байта из буфера (очереди) канального уровня, E_W – разрешение на запись очередного байта (готовность физического уровня к приему байта). Подсистема маскируется, в качестве входного параметра назначается бодовый интервал dt. Все временные параметры подсистемы будут задаваться через бодовый интервал, что, предположительно, позволит получить подсистему, способную работать при различной скорости передачи данных в линии связи.

На рис. 30 представлена упрощенная модель для проверки работы физического уровня в направлении передачи информации от системы телемеханики в линию связи. Тактовый генератор CLK_COM определяет скорость передачи битового потока в линию связи. Счетчик бит CT_clk_COM отсчитывает каждый 11-й бит символа (его выходной сигнал обозначен w), и таким образом является счетчиком символов (байт). Выход счетчика при наличии разрешения от канального уровня поступает на выходной порт CLK для выдачи сигнала считывания очередного байта. Таким образом, считывание производится на интервале выдачи в линию связи стоп-бита (11-го бита символа). На этом интервале производится загрузка очередного байта данных (порт BYTE) в регистр физического уровня. Триггер START-STOP обеспечивает формирование паузы и разрешение работы физического уровня после окончания паузы. Синхронизация начала работы осуществляется логической схемой START. При этом окончание и начало паузы согласуется с 11-м битом. Дискретизаторы нулевого уровня обеспечивают согласование дискретных времен входных сигналов и блоков физического уровня. Элемент Line согласует логические уровни сигналов физического уровня и интерфейса RS-232C (+5 и -5 В).

Рис.30. Схема модели физического уровня передатчика

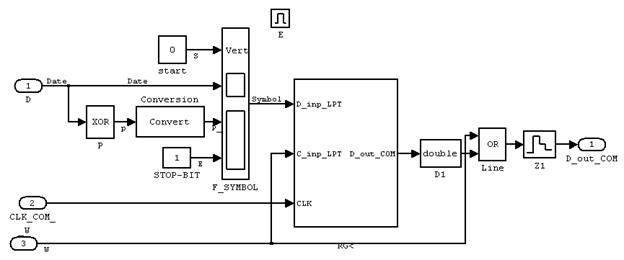

Схема формирования символа для передачи в линию связи показана на рис.31. Регистр сдвига RG< был рассмотрен выше. Логический элемент «сумма по модулю 2» (XOR) определяет бит четности символа. Символ формируется схемой вертикальной конкатенации старт-бита, байта данных, бита паритета четности и стоп-бита. Сформированный символ записывается в параллельный порт регистра сдвига в интервал времени, соответствующий стоп-биту (сигнал w), а затем регистром сдвига с частотой

Рис. 31. Формирование символа физического уровня

определяемой портом CLK_COM_ выдается в линию связи. Стоп-бит поступает в линию связи независимо от регистра сдвига через схему Line. Элемент Conversion обеспечивает инвертирование байта данных таким образом, что бы в линию связи он поступал младшим битом вперед.

Физический уровень приемной станции. Модель физического уровня приведена на рис. 32. Линия связи при нормальной работе поставляет физическому уровню (на вход LINE) последовательность бит или находится в состоянии «пауза» (Pause). При нарушении целостности линии определяется состояние «обрыв» (Break). Пауза используется в качестве разделителя между поступающими кадрами.

Физический уровень приемной станции. Модель физического уровня приведена на рис. 32. Линия связи при нормальной работе поставляет физическому уровню (на вход LINE) последовательность бит или находится в состоянии «пауза» (Pause). При нарушении целостности линии определяется состояние «обрыв» (Break). Пауза используется в качестве разделителя между поступающими кадрами.

При нормальной передаче пауза внутри кадра недопустима. Биты сгруппированы в символы. Физическому уровню приемника известна бодовая скорость, он распознает символы и проверяет их на корректность. Работа физического уровня начинается с приема паузы из линии связи, переход из логической единицы в ноль (окончание паузы) классифицируется как начало первого символа кадра. При этом запускается тактовый генератор, работающий с 16-ти кратной частотой по отношению к бодовой скорости, на 5-ом импульсе этого генератора осуществляется определение уровня входного сигнала.

На начальном этапе используется следующий алгоритм определения логического значения сигнала. При уровне сигнала более +3 В фиксируется логический 0, при значении сигнала менее -3 В фиксируется логическая 1. Если уровень сигнала в пределах от -3 В до +3 В, то значение текущего бита приравнивается к предыдущему. Производится подсчет принятых бит. При приеме символа производится также проверка на четность и сравнение результатов проверки с принятым битом четности. 11-й элемент символа должен быть стоп-бит. При отрицательном результате проверок вырабатывается сигнал ошибки. Физический уровень выделяет из принятого символа байт данных BAYTE_ и передает его канальному уровню. Выдача байта осуществляется во время приема стоп-бита, с этой целью формируется сигнал w-11, который передается на выходной порт C_byte. Сигнал готовности канального уровня к чтению байта поступает на входной порт E_OUT.

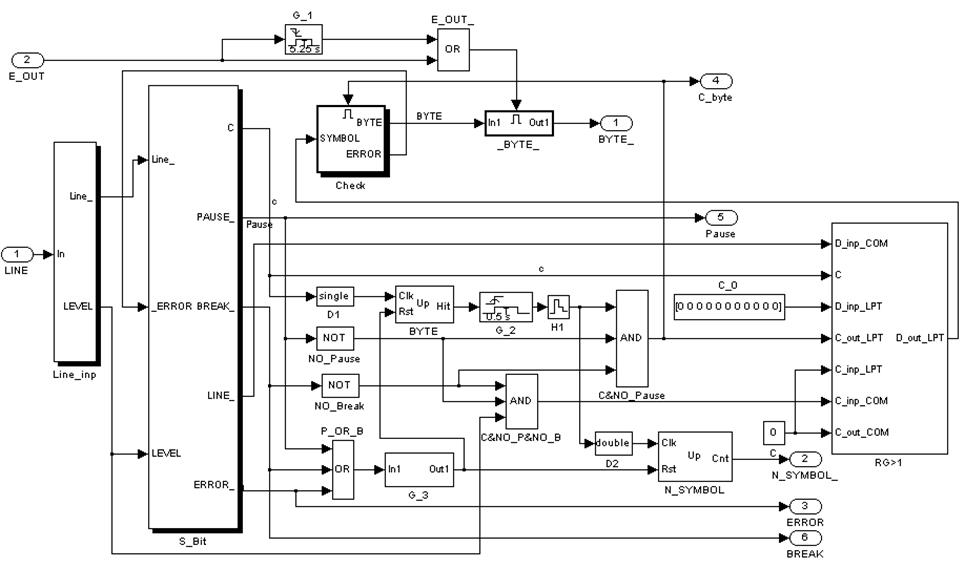

Схема модели физического уровня приемника дана на рис.33. Входной сигнал с линии поступает на линейный приемник Line_inp, где осуществляется измерение уровня сигнала и формирование логических значений 1 и 0. Логические значения поступают на его выходной порт Line_. Второй порт signal_ вырабатывает логическую 1 при нахождении уровня входного сигнала в допустимом пределе и разрешает ввод данных в сдвигающий регистр RG>.

Селектор бит S_Bit осуществляет определение значения бита на каждом бодовом интервале. Определяемые биты выставляются на его выходной порт LINE. Порты PAUSE, BREAK селектора бит активизируются при определении соответствующего состояния линии. Сигнал ERROR_ транслируется селектором со своего входного порта _ERROR. Порт С активизируется на каждом бодовом интервале во время проверки значения текущего бита и вырабатывает строб-сигнал (на 5-м импульсе внутреннего тактового генератора).

Подсистема Check осуществляет проверку текущего символа на корректность и выделяет из символа байт данных. Сформированный регистром сдвига RG< символ поступает на входной порт SYMBOL. Работа подсистемы разрешается элементом C&NO_Pause при условии, что линия связи не находится ни в состоянии «пауза», ни в состоянии «обрыв» и принимаемый бит является 11-м в текущем символе (стоп-битом).

Выделенный байт данных выставляется на порт BYTE, а при обнаружении ошибки активный сигнал вырабатывает порт ERROR

Счетчик символов кадра N_SYMBOL увеличивает свои показания при каждом принятом символе и сбрасывается в исходное состояние при возникновении активного значения одного из сигналов «ошибка», «пауза» или «обрыв» (логическая схема P_OR_B).

Регистр сдвига RG> осуществляет прием бит по входу D_inp_COM и выдачу символов по выходу D_out_LPT. Его вход C принимает строб-сигнал интервала идентификации текущего бита, который используется в качестве тактового сигнала сдвига регистра. Порт С_inp_COM разрешает ввод очередного бита, а порт C_out_LPT разрешает выдачу символа по выходу D_out_LPT. Остальные порты блокированы соответствующими элементами схемы.

Генераторы импульсов G_1, G_2, G_3 обеспечивают согласование работы элементов по времени, а преобразователи D1 и D2 – по типу данных модели.

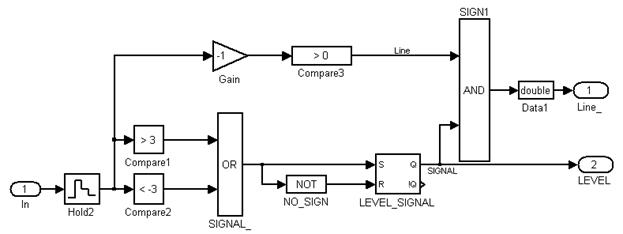

Модель линейного блока физического уровня представлена на рис. 34. Блок преобразует уровни сигналов интерфейса RS-232 в логические уровни (Compare3) и проверяет допустимость принятого сигнала по амплитуде (Compare1, Compare2, SIGNAL_, LEVEL_SIGNAL). При допустимом уровне принимаемого сигнала его логическое значение выставляется на выходной порт Line_. Результат проверки выдается на выходной порт LEVEL.

Рис. 34. Схема линейного блока физического уровня приемника (Line_inp)

Рис. 33. Схема модели физического уровня приемника.

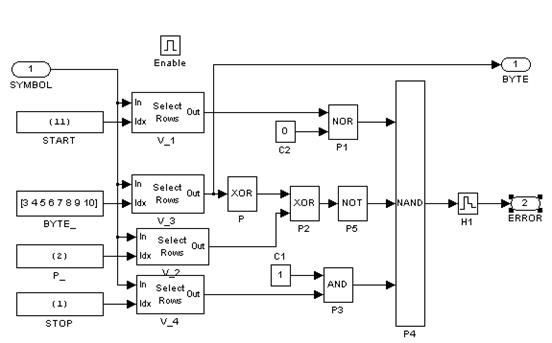

Схема модели контроля правильности полученного символа Check дана на рис. 35. При активизации блока Check блоки селекции V_1…V_4 выделяют элементы символа с учетом приема символа младшим битом вперед. Логические блоки P1, P3 осуществляют сравнение контролируемых бит с шаблонами. Блок P вычисляет признак четности байта символа, блоки P2, P5 сравнивают вычисленное значение с битом четности символа. Результаты проверок обрабатываются и выставляются на порт ERROR. Выделенный из принятого символа байт передается на порт BYTE.

Рис.35. Схема контроля символа (Сheck)

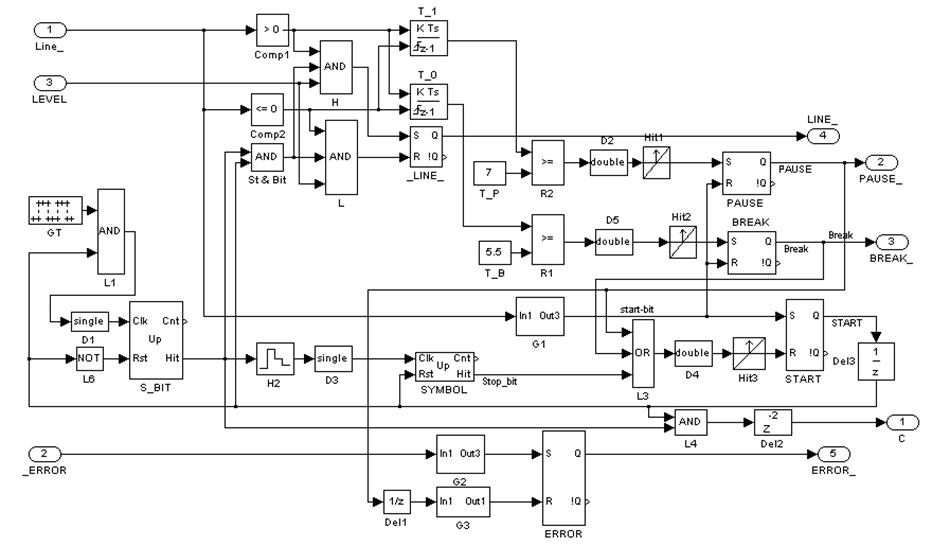

Схема модели селектора бит приведена на рис. 36. Тактовый генератор GT выдает импульсы с частотой в 16 раз превышающую бодовую. В схемы его сигналы поступают после срабатывания триггера START. Этот триггер возбуждается при получении из линии связи перепада 1/0 через генератор одиночного импульса G1.Сброс триггера START производится при одном из следующих условий: получен стоп-бит, обнаружено состояние «пауза», обнаружено состояние «обрыв» через логический блок L3.

Элемент задержки Del3 на выходе триггера START обеспечивает разрыв алгебраической петли. Тактовые сигналы GT поступают на счетчика S_BIT, который на 5-ом импульсе выдает с его выхода Hit логическую единицу (строб). Выделенный интервал времени используется для проверки значения принимаемого бита. Бит данных, поступивший через порт Line_, обрабатывается компараторами Comp1, Comp2 и поступает на схемы выделения сигналов высокого H или низкого L состояния. Выделенные сигналы переключают триггер _LINE_ который и выдает принимаемые биты на порт LINE_.

Одновременно производится определение длительностей высокого и низкого состояний, которое затем сравнивается с пороговыми значениями признаков паузы T_P и обрыва T_B. Элементы сравнения R1 и R2 при превышении установленных порогов возбуждают соответствующие триггеры PAUSE или BREAK. Триггер фиксации ошибки _ERROR возбуждается от входного порта _ERROR, а сбрасывается при возникновении состояния «пауза». Выход этого триггера поступает на выходной порт ERROR_. Стробы проверки уровня бит при возбужденном состоянии триггера START выдаются на выходной порт C.

Рис. 36. Схема модели селектора бит физического уровня приемника

Канальный уровень

Канальный уровень обеспечивает передачу и прием кадров. Этот уровень взаимодействует с прикладным и физическим уровнями, являясь посредником между ними. Протокол обмена между канальными уровнями передающей и приемной стороны включает в себя средства защиты от искажения, потери или дублирования кадра. Рассмотрим канальные уровни передающей и приемной станций при работе телеуправления.

Канальный уровень передающей станции. Канальный уровень приведен на рис. 37. Он получает от прикладного уровня блоки данных ASDU и количество попыток посылки кадра приемной стороне. Уровень формирует заголовок кадра, подсчитывает контрольную сумму и оформляет окончание кадра. Формат кадра зависит от типа передаваемого сообщения. Ограничимся рассмотрением процедуры передачи приказа. Сформированный кадр в виде последовательности байт предоставляется физическому уровню, который осуществляет выборку последовательность байт в соответствии со скоростью передачи в линии связи. Для согласования скоростей формирования кадра и выборки его байт используется очередь.

Канальный уровень передающей станции. Канальный уровень приведен на рис. 37. Он получает от прикладного уровня блоки данных ASDU и количество попыток посылки кадра приемной стороне. Уровень формирует заголовок кадра, подсчитывает контрольную сумму и оформляет окончание кадра. Формат кадра зависит от типа передаваемого сообщения. Ограничимся рассмотрением процедуры передачи приказа. Сформированный кадр в виде последовательности байт предоставляется физическому уровню, который осуществляет выборку последовательность байт в соответствии со скоростью передачи в линии связи. Для согласования скоростей формирования кадра и выборки его байт используется очередь.

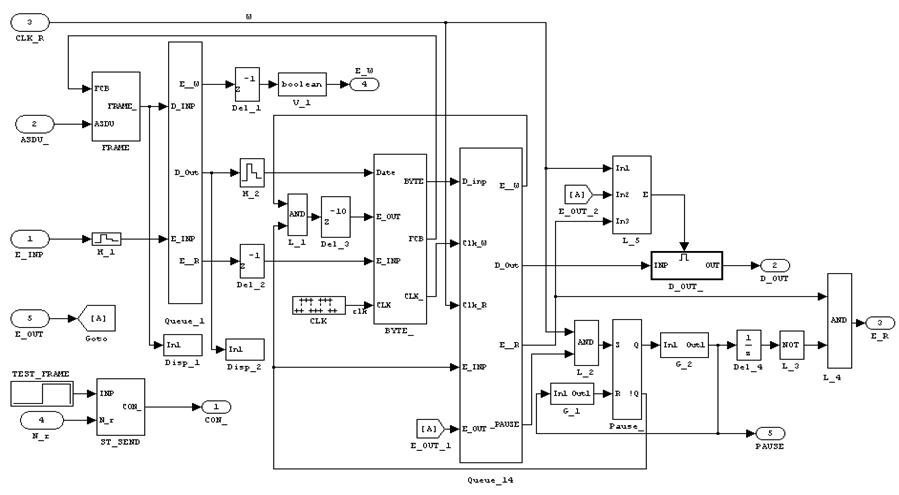

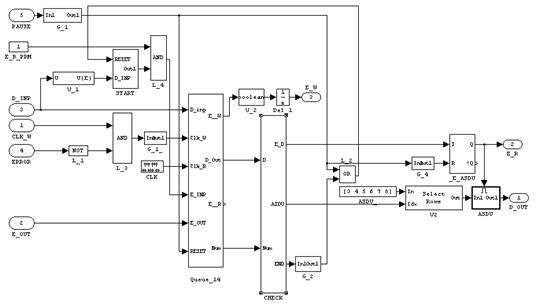

Рассмотрим формирование кадра переменной длины (формат L). Схема модели канального уровня приведена на рис.38. Полученный от прикладного уровня блок ASDU оформляется в кадр блоком FRAME и записывается (при наличии разрешения от прикладного уровня на входе E_INP) в регистр хранения Queue_1. Регистр хранения выполнен на основе очереди размером в одну запись. После записи данных регистр хранения выставляет активный сигнал на порт E_R, а данные - на порт D_Out. Блок BYTE_ с частотой, определяемой генератором CLK, осуществляет последовательное считывание байт кадра и запись их в выходную очередь Queue_14. Разрешение на запись в эту очередь вырабатывается после ее опустошения (считывание всех ранее записанных данных) и выставляется на порт E_W. Разрешение на чтение очереди Queue_14 выставляется на порт E_R после заполнения очереди входными данными, сами данные выставляются на порт D_Out. Номер кадра FCB вычисляется в блоке BYTE_ и записывается в командный байт кадра блоком FRAME. Данные поступают на выходной порт схемы D_OUT только при совпадении трех условий (блок L_5):

наличие синхросигнала считывания (это сигнал, совпадающий с моментом времени выдачи физическим уровнем стоп-бита, порт CLK_R),

разрешение на прием данных физическим уровнем (порт Е_OUT схемы)

разрешение на выдачу данных регистром Queue_14 (порт E_R регистра).

Триггер Pause_ вырабатывает сигнал «пауза» при условии получения сигнала о начале паузы от блока Queue_14, синхронизируя его со стоп-битом. Сброс триггера Pause_ осуществляется после отсчета требуемого интервала времени (блоки G_1, G_2). Сигнал «пауза» останавливает запись в блок Queue_14, запрещает считывание данных из блока BYTE_ и снимает разрешение чтения данных физическим уровнем (порт E_R).

Счетчик посылок кадров ST_SEND сравнивает число разрешенных попыток посылки одного и того же кадра с количеством выполненных посылок и при достижении установленного лимита (порт N_r) выставляет отрицательное сообщение для прикладного уровня.

Рис. 38. Схема модели канального уровня передатчика

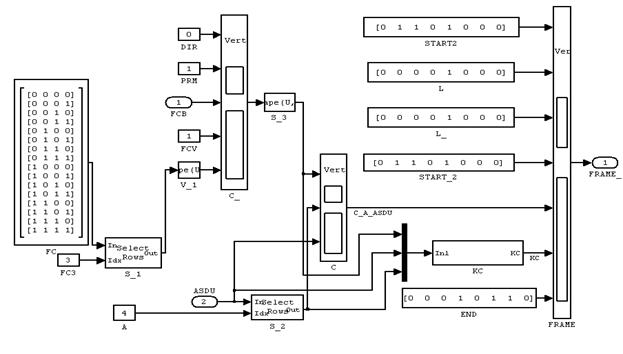

На рис. 39 приведена схема формирования кадра. Кадр формируется путем вертикальной конкатенации байт заголовка кадра (START2, L, L, START2), командного байта С, байта адреса приемной станции А, блока данных ASDU, байт контрольной суммы (КС) и окончания кадра (END). Командный байт формируется путем включения в него бита номера кадра FCB, и кода команды FC. Код команды выбирается из таблицы возможных кодов селектором S_1.

Рис. 39. Схема формирования кадра блоком FRAME

Адрес приемной станции копируется из блока ASDU элементом S_2. Контрольная сумма вычисляется по данным командного байта С, байта адреса А и байт блока ASDU путем суммирования по модулю 256 в блоке КС и записывается в состав кадра.

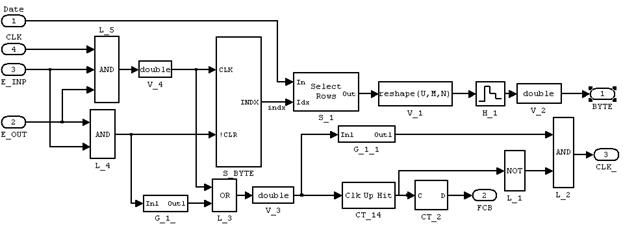

На рис. 40. приведена схема выборки байта из регистра хранения.

Рис. 40. Схема выборки номера байта BYTE_

С частотой определяемой сигналом входного порта CLK в блоке S_BYTE вырабатывается последовательность индексов (INDEX), которые используются для выбора очередного байта из кадра, поступившего на входной порт Date. Байты выставляются на порт BYTE. Блок СТ_14 осуществляет счет выданных байт и в конце кадра (после 14-го байта) выдает сигнал на порт CLK_, блок СТ_2 определяет бит с номером кадра (FCB).

С частотой определяемой сигналом входного порта CLK в блоке S_BYTE вырабатывается последовательность индексов (INDEX), которые используются для выбора очередного байта из кадра, поступившего на входной порт Date. Байты выставляются на порт BYTE. Блок СТ_14 осуществляет счет выданных байт и в конце кадра (после 14-го байта) выдает сигнал на порт CLK_, блок СТ_2 определяет бит с номером кадра (FCB).

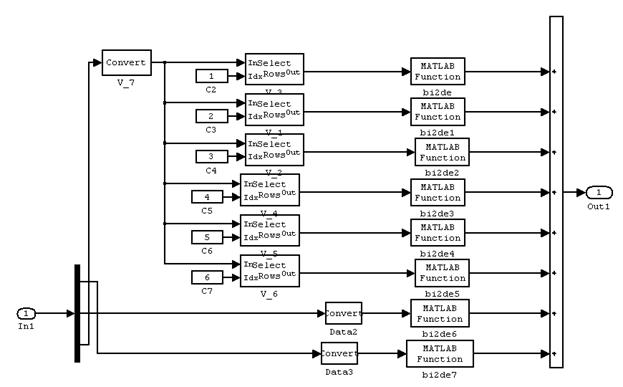

Вычисление суммы по модулю 256 показано на рис. 41. Входные данные данного блока вычисляются путем перевода бинарного представления каждого контролируемого байта кадра в десятичное исчисление и суммирования полученных результатов. Для выполнения приведенных вычислений применяются функции MATLAB bi2de. Одна из возможных схем вычислений приведена на рис. 42

Рис. 42. Вычисление суммы байт

Канальный уровень приемной станции. Модель канального уровня приведена на рис. 43. Канальный уровень получает от физического уровня байты, формирует из них кадр, проверяет его на отсутствие искажений, выделяет из кадра блок ASDU и передает его прикладному уровню. От физического уровня блок получает тактовые импульсы записи CLK_W, входные байты D_INP, сигналы ошибки приема байта ERROR, состояния паузы в линии PAUSE. Кроме того на вход поступают разрешение прикладного уровня на запись в него данных E_OUT. Прикладному уровню блок передает через порт D_OUT блок ASDU и сигнал разрешения считывания данных E_R. Для физического уровня вырабатывается сигнал разрешения записи данных в канальный уровень E_W.

Схема модели канального уровня приведена рис. 44. Блок START осуществляет проверку принятых байт на соответствие их шаблону START2. При обнаружении такого байта дается разрешение на заполнение очереди принимаемого кадра Queue_14.

Схема модели канального уровня приведена рис. 44. Блок START осуществляет проверку принятых байт на соответствие их шаблону START2. При обнаружении такого байта дается разрешение на заполнение очереди принимаемого кадра Queue_14.

Рис. 44. Схема модели канального уровня приемника

Ввод данных в очередь осуществляется при отсутствии активного сигнала ERROR от физического уровня. Частота записи данных соответствует частоте приема символов физическим уровнем. При получении сигнала PAUSE осуществляется дополнительное разрешение на очистку очереди, что необходимо при получении такого сигнала до полного приема кадра. Сброс схемы START осуществляется после приема последнего байта кадра или после получения сигнала PAUSE.

Регистр входных данных после заполнения очереди выставляет на порт E_W сигнал разрешения чтения данных, а сами данные поставляются через порт D_out. Кроме того на порт Num выставляются данные о номере считываемого из регистра байта. Блок CHECK осуществляет проверку принятого кадра на отсутствие искажений. При приеме неискаженного кадра блок данных прикладного уровня выставляется на порт ASDU, одновременно переводится в активное состояние порт разрешения выдачи данных E_D. На порт END активный сигнал выставляется при приеме последнего байта кадра. Элемент V2 осуществляет выборку блока ASDU из принятого кадра и при наличии разрешения выставляет на выходной порт схемы D_OUT. Одновременно выставляется разрешающий сигнал, разрешающий чтение блока данных ASDU прикладным уровнем (порт E_R).

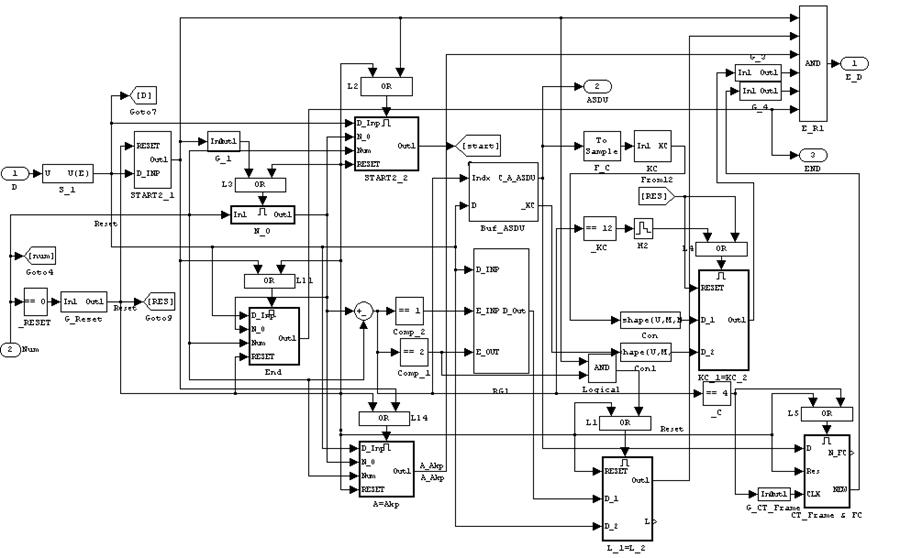

Схема блока проверки кадра дана на рис. 45. Схема получает вводимые в регистр хранения данные через порт D. Одновременно через порт Num поступает номер байта в регистре. На основании этой информации блок START_2_1 осуществляет поиск первого байт со значением START2. При получении этого значения запоминается номер принятого байта в блоке N_0. Полученные данные используются для вычисления номера текущего байта относительно первого полученного байта (с кодом START2). Срабатывание блока START2_1 разрешает работу всех схем проверки элементов кадра. Кроме того, срабатывание блока START_2_1 выставляет логическую единицу на схему проверки отсутствия искажения кадра Е_R1. Второй и третий байт кадра должны содержать длину кадра и быть равными друг другу. Проверку осуществляет блок «L_1=L_2». При этом второй байт запоминается в регистре RG1 и выдается для проверки при приеме третьего байта.

Рис. 45. Проверка принятого кадра на искажения.

При удовлетворительной проверке схема проверки также выставляет логическую единицу на схему отсутствия искажений кадра. Четвертый байт проверяется по шаблону START2, результат проверки также поступает на схему E_R1. Блок «A=Akp» проверяет соответствие адреса приемной станции адресу, указанному в заголовке кадра. При положительном результате проверки блок выставляет логическую 1 на схему E_R1. В блоке Buf_ASDU выделяются командный байт и байта адреса заголовка кадра, а также блок данных прикладного уровня ASDU и байт с контрольной суммой. Байт с контрольной суммой выставляется на порт _KC, остальные байты на порт C_A_ASDU.

В блоке КС по выделенным байтам вычисляется контрольная сумма, которая сравнивается с контрольной суммой, записанной в анализируемом кадре. Сравнение осуществляет блок «KC_1=KC_2», результат сравнения выставляется на схему E_R1. В схеме «СТ_Frame & FC» производится анализ функционального кода FC и номера кадра FCB. Номер функционального кода выставляется на порт N_FC. В случае, если кадр классифицируется как новый, на порт NEW выставляется логическая единица, которая поступает на логическую схему E_R1. Блок End проверяет, равен ли последний байт кадра шаблону «конец кадра» и результат проверки выставляет на схему E_R1.

После опустошения буфера очереди Queue_14 на порт Num рассматриваемой схемы поступает значение 0, которое используется для генерации схемой G_Reset импульса, осуществляющего сброс всех схем проверки кадра в исходное состояние. Поскольку проверяющие блоки выполнены в виде Enable-подсистем, то в момент сброса выставляется также сигнал на разрешение работы этих блоков.

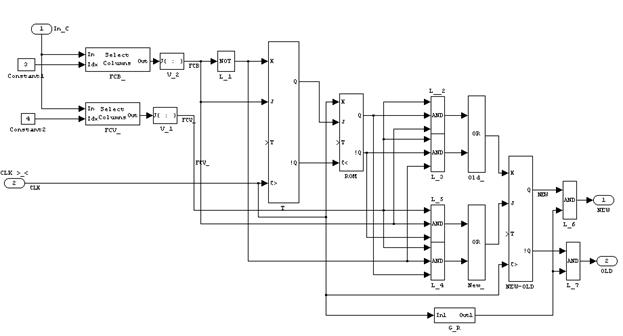

На рис. 46 приведен пример реализации схемы определения нового значения кадра, которая применена в блоке «CT_Frame & FC». Схема получает на входной порт In_C контрольный байт заголовка кадра, из которого выделяет биты актуальности счетчика кадров FCV и номер кадра FCB. Принятое значение номера кадра запоминается в регистре T при поступлении фронта синхронизирующего сигнала CLK. Предыдущее значение номера кадра хранится в триггере ROM и считывается из триггера T по срезу синхронизирующего сигнала CLK. Логические схемы L_2…L_5 сравнивают старое значение кадра с новым, результат сравнения запоминается в триггере NEW-OLD (по фронту CLK) и выставляется на выходные порты NEW и OLD.

Рис. 46. Схема определения нового значения кадра

Прикладной уровень

Прикладной уровень обеспечивает формирование блока данных ASDU для посылки вторичной станции и извлечение из принятого блока данных сообщения для пользовательского процесса. Этот уровень взаимодействует с процессом пользователя и канальным уровнем. Рассмотрим работу прикладного уровня только для процесса передачи приказа.

Прикладной уровень обеспечивает формирование блока данных ASDU для посылки вторичной станции и извлечение из принятого блока данных сообщения для пользовательского процесса. Этот уровень взаимодействует с процессом пользователя и канальным уровнем. Рассмотрим работу прикладного уровня только для процесса передачи приказа.

Прикладной уровень первичной станции. Прикладной уровень получает от пользовательского процесса задания на передачу приказа и передает ему квитанцию (положительную или отрицательную), полученную от вторичной станции, о результатах исполнения приказа. На основе полученного приказа уровень формирует блок данных прикладного уровня ASDU, который передается канальному уровню. При получении от канального уровня принятого блока ASDU прикладной уровень извлекает из него квитанцию и передает результаты пользовательскому процессу.

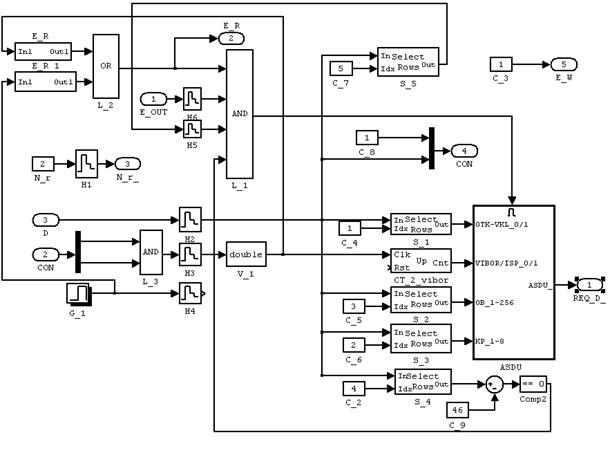

Модель прикладного уровня передающей станции приведена на рис. 47. Процесс пользователя при запросе на выполнение функции передачи приказа выдает прикладному уровню канального сервиса через порт REQ_D следующую информацию. Код операции: отключить/включить (0/1), номер контролируемого пункта (1…8), номер объекта (1…255), номер функции (для приказа 45 или 46) и выставляет запрос на предоставление сервиса для выполнения указанной функции – сигнал REQ.

После обработки запроса (передаче канальному уровню сформированного блока ASDU и предельного количества попыток передачи кадра, а также получения от канального уровня уведомления о выполнении операции передачи кадра) прикладной уровень выставляет процессу пользователя уведомление об исполнении функции на выходной порт CON. Уведомление (квитанция) может быть как положительным, так и отрицательным).

Порт N_r служит для передачи предельного количества попыток передачи кадра, порт Е_R для извещения о готовности данных для чтения, а порт E_W о готовности прикладного уровня к приему данных от процесса пользователя. Порт D обеспечивает прием данных от процесса пользователя, а входной порт CON прием извещения (квитанции) от канального уровня. Схема модели представлена на рис. 48.

Элемент ASDU в модели формирует блок данных прикладного уровня. Выборка кода операции осуществляется селектором S_1 из данных, полученных от пользовательского процесса. Этап команды выбор или исполнение определяется счетчиком положительных уведомлений от прикладного уровня СТ2_vibor. Уведомления поступают на входной порт COM и содержат сигнал значения уведомления и его актуальности. Номер объекта OB_1-256 и контролируемого пункта KP_1-8 выбирается селекторами S_2, S_3 из данных пользовательского процесса. Селектор S_4 выбирает идентификатор блока данных, который задает номер функции пользовательского процесса. В модели рассматривается только передача приказа за два этапа (функция 46), наличие которой в данных процесса пользователя осуществляет компаратор Comp_2. Селектор S_5 выбирает сигнал запроса на обслуживание функции. Элементы E_R и E_R_1 отсчитывают временные интервалы для разрешения работы элемента ASDU. Первый из них срабатывает при получении положительного уведомления от канального уровня, а второй в начале процесса моделирования. Необходимый сигнал для инициализации работы прикладного уровня генерируется внутренним генератором G_1. Логическая схема L_1 производит проверку всех условий, необходимых для выдачи блока ASDU на выходной порт REQ_D_ (наличие запроса от пользовательского процесса S_5, готовности канального уровня принять данные Е_OUT, совпадение номера функции с ожидаемым Comp2.

Рис. 48. Схема модели прикладного уровня передающей станции

Разрешение на чтение данных уровня приложения (порт E_W) и максимальное количество попыток посылки кадра (порт N_r_) генерируется внутри прикладного уровня. Положительное уведомление для пользовательского процесса (выходной порт CON) выставляется при получении положительного уведомления от канального уровня.

Элементы H1…H6 обеспечивают согласование дискретного времени прикладного уровня с временами смежных уровней. Преобразователь типа данных V_1 обеспечивает требуемую форму представления данных для работы элементов модели.

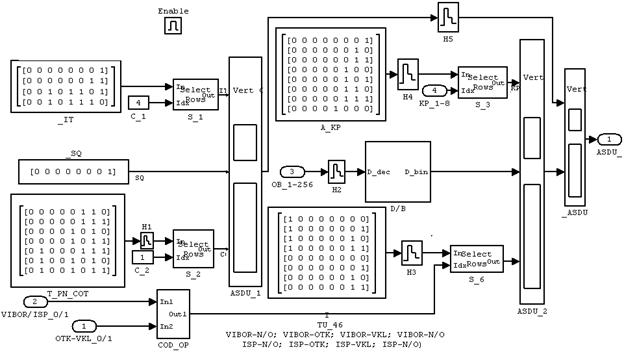

На рис. 49 приведена модель подсистемы формирования блока ASDU. Блок ASDU состоит из 6-ти байт. Три первых байта объединяются блоком конкатенации ASDU_1 путем выбора из таблиц соответствующих строк. Следующие три байта объединяются блоком ASDU_2. При этом байт выбора объекта формируется по заданному номеру в блоке D/B путем определения группы и номера в группе. Выбор последнего байта, содержащего собственно команду управления (элемент информации), производится в зависимости от операции и номера кадра селектором S_6. Значение строк приведено под таблицей, а вычисление индекса осуществляется в элементе COD_OP. Формирование 6-байтового блока осуществляется элементом _ASDU. Элемент COD_OP вычисляет номер строки путем линейного преобразования заданного этапа операции (порт VIBOR/ISP_0/1) и характера операции (порт OTK-VKL_0/1).

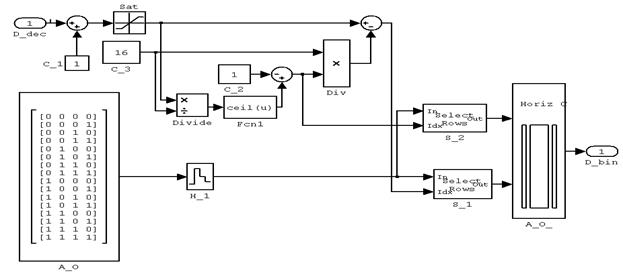

Модель формирования кода номера объекта D/B приведена на рис. 50. Десятичный код номера объекта, получаемый с входного порта D_dec, обрабатывается блоком ограничение Sat, для получения значения в допустимом интервале 1-256. Код номера объекта состоит из двух частей, 4 бита для кодирования группы и 4 бита для кодирования объекта в группе. Делением на 16 определяется номер группы, а вычислением остатка номер объекта в группе.

Рис. 49. Модель подсистемы формирования блока ASDU

Вычисленные индексы используются селекторами S_1 и S_2 для выбора из таблицы двоичных кодов на четыре разряда требуемых строк, которые затем объединяются в байт путем горизонтальной конкатенации элементом A_O_ и выставляется на выходной порт D_bin.

Рис. 50. Модель формирователя кода номера объекта

Прикладной уровень вторичной станции. Прикладной уровень получает от канального уровня блок данных ASDU и извлекает из него информацию, необходимую процессу пользователя. В рамках курсового проекта рассматриваем прием команды на включение или отключение одного из объектов контролируемого пункта, обслуживаемого данной станцией. В этом случае процессу пользователя передается номер контролируемого пункта, номер объекта, номер функции, этап команды и извещение о получении данных из кадра IND.

Прикладной уровень вторичной станции. Прикладной уровень получает от канального уровня блок данных ASDU и извлекает из него информацию, необходимую процессу пользователя. В рамках курсового проекта рассматриваем прием команды на включение или отключение одного из объектов контролируемого пункта, обслуживаемого данной станцией. В этом случае процессу пользователя передается номер контролируемого пункта, номер объекта, номер функции, этап команды и извещение о получении данных из кадра IND.

Для канального уровня прикладной выдает извещение (квитанцию) о приеме команды, для передачи ее первичной станции.

Модель прикладного уровня приемной станции дана на рис.51. Входные порты имеют следующие назначения:

E_INP – разрешение на прием данных от канального уровня

D_INP – данные от канального уровня

E_OUT – разрешение на выдачу данных от процесса пользователя

Выходные порты:

E_R – разрешение на чтение данных уровня приложения для процесса пользователя

E_W – разрешение на запись данных канального уровня в уровень приложения

IND – сообщение для процесса пользователя с указанием функции и ее параметров

IND – сообщение для процесса пользователя с указанием функции и ее параметров

Схема модели уровня приложения приемной станции показано на рис. 52. Блок данных ASDU, поступивший на входной порт D_INP разделяется на отдельные байты с помощью селекторов S_1…S_6. Первые 4 байта после получения разрешения на чтение данных (порт E_INP) проверяются на соответствие шаблонам. При совпадении с шаблоном соответствующий блок проверки выставляет логическую единицу. Логическая схема L1 выдает разрешение при совпадении всех проверок (идентификатора типа блока, классификатора переменной структуры, причины передачи и адреса контролируемого пункта). Элемент С дешифрирует информационный элемент (команду) и выделяет из нее биты характера операции (OTK, VKL) и биты этапа команды выбор и исполнение (Select, Exco). Байт, содержащий адрес объекта, дешифрируется элементом А_О и полученный результат (номер группы и объект в группе) совместно с дешифрованной командой выдается через элемент IND_ на выходной порт IND. Выдача производится при наличии разрешение от логической схемы L1. Разрешение на работу элементов проверки и дешифрации команды выдается внешней схемой через порт E_INP, при этом запускаются генераторы одиночного импульса в схеме G_1. Один из них (E_R) выдает сигнал на разрешение чтения данных прикладного уровня процессом пользователя (через порт E_R), другой (Reset) осуществляет сброс всех элементов проверки. Сброс элемента дешифрации команды С осуществляется позже, чем остальных элементов, что необходимо для фиксации результатов на выходном порте D_OUT элемента IND_, поскольку фиксация производится в момент снятия разрешающего сигнала на элементе IND_. Этот момент наступает при сбросе элементов проверки.

Декодирования адреса объекта осуществляется в элементе A_O путем выделения старшего и младшего полубайтов адреса и перевода их в десятичную форму.

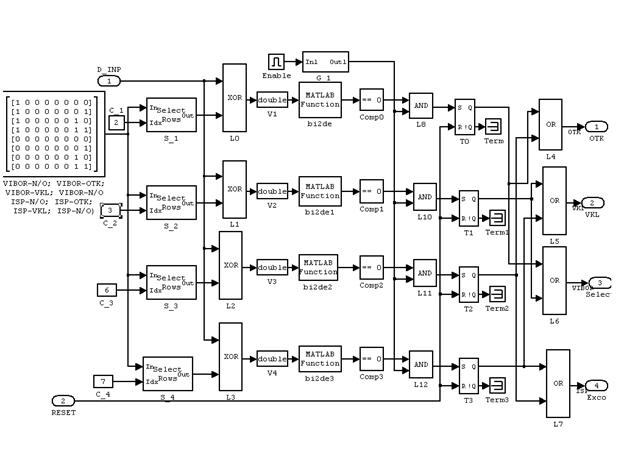

Декодирования команды осуществляется в элементе С. Схема работы элемента дана на рис.53. Декодирование производится следующим порядком. Входной байт, поступающий через порт D_INP, сравнивается с одним из ожидаемых шаблонов в логических схемах L0…L3. При совпадении с одним из шаблонов срабатывает соответствующий триггер T0…T3, фиксируя значение принятой команды. Схемы L4…L7 дешифрируют принятую команду и выдают на выходные порты.

Рис.53. Схема выделения команды из командного байта блока ASDU

Процессы пользователя

Процессы пользователя представляет собственно саму систему телемеханики, которая для передачи своих сообщений использует сервис связи. Сервис связи включает в себя три, рассмотренных выше уровня. Каждый процесс пользователя (иногда называют процесс или уровень приложения) состоит из первичной и вторичной функции. Для курсового проекта первичная функция исполняется на первичной станции пункта управления и инициируется действиями диспетчера, а вторичная - на вторичной станции КП и выполняется по запросу первичной функции.

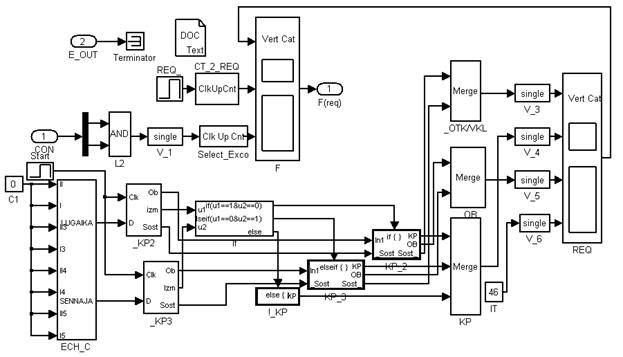

Первичная функция пользователя. Рассматривается процесс телеуправления. Этот процесс инициируется передающей станцией. Первичная функция этого процесса взаимодействует с оператором (энергодиспетчером) и прикладным уровнем передающей станции. Энергодиспетчер указывает объект на одном из контролируемых пунктов, и выбирает для него операцию, например, включить. Первичная функция процесса пользователя выбирает требуемые параметры и передает запрос на обслуживание прикладному уровню первичной станции через порт F(req) (см. рис. 54). Прикладной уровень выставляет сигнал готовности принять данные и квитанцию от вторичной функции пользовательского процесса. Квитанция поступает на входной порт CON, а сигнал готовности на порт E_OUT первичной функции. Модель первичной функции процесса пользователя для телеуправления представлена на рис. 55.

Первичная функция пользователя. Рассматривается процесс телеуправления. Этот процесс инициируется передающей станцией. Первичная функция этого процесса взаимодействует с оператором (энергодиспетчером) и прикладным уровнем передающей станции. Энергодиспетчер указывает объект на одном из контролируемых пунктов, и выбирает для него операцию, например, включить. Первичная функция процесса пользователя выбирает требуемые параметры и передает запрос на обслуживание прикладному уровню первичной станции через порт F(req) (см. рис. 54). Прикладной уровень выставляет сигнал готовности принять данные и квитанцию от вторичной функции пользовательского процесса. Квитанция поступает на входной порт CON, а сигнал готовности на порт E_OUT первичной функции. Модель первичной функции процесса пользователя для телеуправления представлена на рис. 55.

Рис. 55. Модель процесса пользователя первичной станции

Интерфейс управления объектами для диспетчера представлен блоком ECH_C. Результаты действий диспетчера выдаются в цифровой форме через выходные порты «LUGAIKA» и «SENNAJA». Для каждого контролируемого пункта предусмотрен блок обработки, задача которого определить номер выбранного объекта Ob, характер операции Sost и бит изменения состояния izm. Бит изменения состояния фиксирует ситуацию, когда диспетчер изменяет текущее состояние объекта. Результат действия диспетчера может принимать одно из трех значений: отключить – 1, включить – 2, отказ от операции - 3.

Для последующей обработки команде отключить присвоен номер 0, включить -1, а при отказе от операции выдается номер текущего состояния (0 или 1). Нумерация объектов осуществляется для каждого контролируемого пункта независимо от других КП.

Блок If позволяет дальнейшую обработку вести только для выбранного контролируемого пункта. Результаты обработки выставляют в виде вектора блоком формирования запроса REQ. Окончательно запрос формируется в блоке F, где добавляются данные об этапе приказа. Приказ подается за два этапа: предварительный (Select) и исполнение (Exco). Запрос на обслуживание каждого из этапов передается сервису связи через порт F(req). Сигнал REQ и счетчик CT_2_REQ обеспечивают нумерацию этапов, а счетчик Select_Exco контролирует выполнение первого этапа через порт CON. На этот порт поступает формируемое сервисом связи извещение (квитанция) о результатах доставки приказа вторичному процессу на контролируемом пункте.

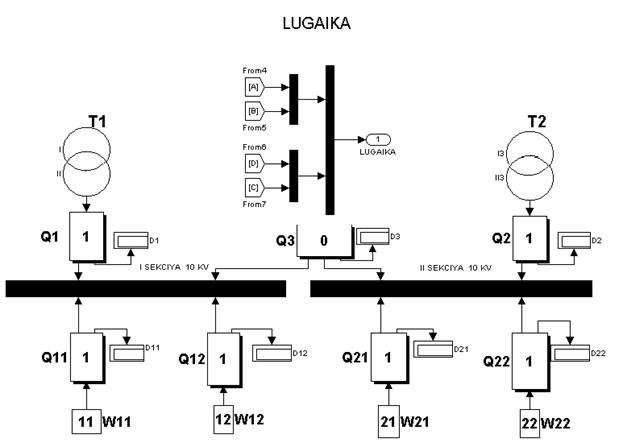

На рис. 56 приведена модель интерфейса управления контролируемым пунктом, получающим питание от двух источников.

Рис. 56. Модель интерфейса управления контролируемым пунктом