Методы Изоляции элементов друг от друга в микросхемах 1 страница

При отсутствии изоляции элементов биполярных микросхем все они окажутся электрически связанными между собой через подложку. Изоляцию осуществляют с использованием нескольких конструктивно–технологических вариантов.

^ Изоляция обратно–смещенными p–n переходами (см. рис. 1). Этот способ, будучи исторически первым, распространен и по сей день, так как обладает высокой технологичностью, операции создания изолирующей области (дополнительно одна операция фотолитографии и одна операция диффузии) естественным образом вливаются в технологический маршрут, не требуют ни дополнительного оборудования, ни использования новых материалов. Конструкция транзистора изолированного от других элементов микросхемы p–n переходом, показана на рис. 35, а. Недостатком этой конструкции является то, что площадь изолирующей области сравнима с площадью, отводимой под транзистор, и даже превышает ее. Попытка устранить хотя бы частично этот недостаток без изменения способа изоляции привела к созданию транзистора, изображенного на рис. 35, б, в котором изолирующая область сформирована диффузией примеси n–типа на всю глубину эпитаксиального слоя до соприкосновения со скрытым n –слоем и используется в качестве коллекторной области транзистора.

Изоляция элементов полупроводниковых микросхем с помощью обратно смещенного p–n перехода кроме указанного имеет и другие принципиально неустранимые недостатки. К ним относятся: большая паразитная емкость изолирующих p–n переходов и появление дополнительных паразитных элементов в структуре микросхемы; необходимость подачи на изолирующий p–n переход определенного по величине и знаку напряжения смещения; наличие четырехслойных структур n–p–n и p–n–pтипа, которые обладают положительной обратной связью по току, вследствие чего при воздействии на них ионизирующих факторов увеличение тока через эти структуры будет приводить к еще большему его возрастанию.

Указанные недостатки не позволяют добиться существенных успехов в росте быстродействия микросхем, увеличения степени их интеграции, радиационной стойкости и стабильности в интервале температур.

^ Изоляция диэлектриком. Конструкция интегрального транзистора, изолированного от соседних элементов микросхемы с помощью диэлектрика, показана на рис. 36. Пленка диэлектрика (SiO2) и непроводящая подложка устраняют кардинальным обрезом недостатки, присущие изоляции p–n переходами. Но для осуществления такого способа изоляции необходим довольно сложный технологический процесс, включающий в себя операции по размещению в диэлектрическом материале островков монокристаллического кремния и операции по формированию p–n переходов в этих островках (рис. 36, а). Труден подбор материала диэлектрической положки для этой конструкции, поскольку коэффициенты термического расширения подложки и монокристаллического кремния должны совпадать, иначе проведение операций, связанных с нагревом, станет невозможным из–за коробления структур и появления дефектов в кристаллической решетке кремния.

Структура, изображенная на рис. 36, а, носит название кремний в диэлектрике (КВД), а структура на рис. 36, б — кремний на диэлектрике (КНД).

Основными недостатками конструкций с диэлектрической изоляцией элементов являются: сложный технологический процесс и малый выход годных микросхем; плохой отвод тепла от элементов микросхемы в подложку, поскольку тепловое сопротивление диэлектрических материалов в десятки раз больше теплового сопротивления монокристаллического кремния; трудность создания разводки из–за сравнительно большого перепада высот рельефа поверхности в структурах КНД; высокая плотность дефектов структуры в изолированных островках кремния и низкая воспроизводимость параметров элементов микросхем.

^ Комбинированная изоляция сочетает технологичность изоляции p–n переходом и высокие качества диэлектрической изоляции: элементы микросхемы со стороны подложки изолированы обратно–смещенными p–n переходами, а с боковых сторон – диэлектриком (окислом, стеклом, керамикой, поликремнием и т.д.). Таким образом, изоляция p–n переходами заменяется изоляцией диэлектриком в наиболее уязвимом приповерхностном слое и с боковых сторон.

Наибольшее распространение сегодня получили такие варианты комбинированной изоляции, как локальное окисление (изопланарная технология) (рис. 37, а) и вертикальное анизотропное травление с последующем заполнением канавок поликристаллическим кремнием (полипланарная технология) (рис. 37, б).

В основе технологических процессов лежит локальное сквозное “прокисление” или протравление тонкого (2…3 мкм) эпитаксиального слоя кремния n–типа, в результате этот слой оказывается разделенным на островки, в которых формируются элементы микросхем.

Комбинированная изоляция позволяет уменьшить паразитные емкости изолированных областей на подложку за счет устранения боковых участков p–n переходов (см. рис. 35), устранить токи утечки в области выхода p–n переходов на поверхность и на боковых участках p–n переходов (см. рис. 35). В то же время при методе комбинированной изоляции удается обеспечить хорошие условия теплоотвода и увеличить степень интеграции элементов в микросхеме за счет сокращения площади, отводимой под изоляцию.

^

Структуры ИС на полупроводниках AIIIBV.

Приборы и интегральные схемы на полупроводниках AIIIBV, в частности GaAs служат элементной базой сверх–скоростной и СВЧ–электроники. Рабочая частота приборов на GaAs достигает более 40 ГГц.

Кроме обычных приборов получаемых на основе Ge ( биполярных, полевых транзисторов и т.д.) на основе арсенид галлия создают функциональные приборы использующие физические эффекты возникающие в этом материале. Ниже приведены некоторые структуры которые используются в ИС на основе GaAs.

^ Транзистор бегущей волны. Этот прибор представляет собой устройство с барьером Шотки. Барьер Шотки предназначен для стабилизации усилителя на междолинном переходе электронов. Структура этого прибора приведена на рис. 38. Такой транзистор работает в широком диапазоне частот с усилением 12 дБ и обратным затуханием ~ 32 дБ. Изменяя напряжение на затворе можно увеличить усиление до 35 дБ.

^ Полевые транзисторы с затвором Шотки. На рис. 39 показаны основные типы структур полевых транзисторов на основе GaAs. Полевые транзисторы могут быть выполнены с углублением по затвор или без него. В ряде случаев для уменьшения последовательного сопротивления истока и стока используют с помощью ионной имплантации создается n – область под омические контакты. Величина и форма углубления сильно влияет на значение напряжения пробоя сток–затвор. Напряжение пробоя можно значительно увеличить, если расстояние от стока до затвора сделать больше, чем размер стационарного домена сильного поля, который формируется на затворе со стороны стока.

^ Полевые транзисторы с селективным легированием. Полевые транзисторы на гетероструктурах с селективным легированием относятся к наиболее быстродействующим полупроводниковым приборам. Время переключен приборов на таких транзисторах составляет примерно 10 пс. На основе этих приборов создаются запоминающие устройства с произвольной выборкой емкостью до 4 К.

Полевой транзистор с селективным легированием представляет прибор на гетероструктурах, в которых используется высокое значение подвижности и дрейфовой скорости двумерного электронного газа, формирующегося у границы раздела двух полупроводниковых материалов (как правило, у сильнолигированного AlGaAs и нелигированного GaAs). На рис. 40 приведены конструкции полевого транзистора.

Используя данную структуру можно на одном кристалле получить комплементарные полевые транзисторы с селективным легированием. В этом случае используются транзисторы с изолированным затвором, на основе приборов p– и n–типа в гетероструктурах на AlGaAs–GaAs. Такая технология позволяет создавать быстродействующие логические устройства с малой рассеивающей мощностью для СБИС.

^ Биполярные транзистор. Для создания качественных транзисторов на основе GaAs используют гетероструктуры. Из–за большей ширины запрещенной зоны эмиттера инжекции заряда из базы в эмиттер подавляется, что обеспечивает высокий коэффициент инжекции, близкий к единицы. В биполярных транзисторах на основе перехода AlGaAs– GaAs коэффициент усиления по току составляет 3000. Помимо этого уровни легирования эмиттера и базы могут быть заданы независимо друг от друга: уменьшение уровня легирования эмиттера и увеличения его в базе приводит к меньшей величине сопротивления растекания базы и меньшей емкости база–эмиттер. Все перечисленные факторы вносят вклад в повышение скорости работы транзистора.

Цифровые схемы на основе таких транзисторов обладают однородностью пороговых напряжений и высокой нагрузочной способностью. Недостатком этой структуры является сложная технология получения.

На основе арсенид галлия можно создавать экзотические приборы:

- вертикальные баллистические транзисторы;

- транзисторы на горячих электронах;

- биполярные гетеротранзисторы;

- транзисторы с проницаемой базой;

- самосовмещенный двухсеточный транзистор с проницаемой базой;

- вертикальный полевой транзистор, а также

- функциональные приборы (приборы задания формы тока; приборы временного уплотнения импульсов и т.д.).

23. Требования к конструкции интегральных микросхем.(ГОСТ Р 500044-92)

- Изделия должны удовлетворять требованиям автоматизированной сборки аппаратуры без предварительной технологической подготовки (рихтовка, формовка, обрезка выводов и т.п.) и выдерживать технологические воздействия по стандарту на изделия автоматизированной сборки аппаратуры.

- Изделия должны иметь форму и качество поверхностей, позволяющих проводить захват и удерживание изделия вакуумным инструментом

http://standartgost.ru/g/%D0%93%D0%9E%D0%A1%D0%A2_%D0%A0_50044-92

Цель работы: изучение терминов, определений, классификации и системы условных обозначений, применяемых в микроэлектронике, а также конструктивно-технологических параметров интегральных микросхем (ИМС).

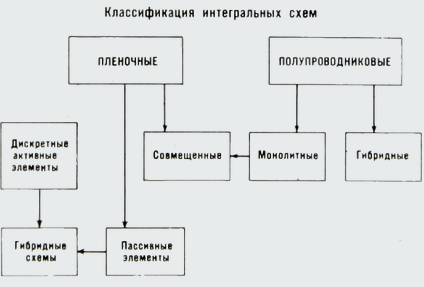

Различные виды интегральных микросхем являются основной элементной базой современной радиоэлектронной аппаратуры. По конструктивно-технологическим признакам ИМС подразделяются на тонкоплёночные, толстоплёночные и полупроводниковые. В зависимости от назначения производятся ИМС широкого применения, представляющие собой различные логические элементы, переключатели, линейные схемы и т.д., обладающие определённой универсальностью, и ИМС специального назначения, представляющие собой отдельные устройства РЭА и предназначенные для конкретных видов РЭА.

Термины и определения ИМС

Интегральная микросхема (ИМС) – микроэлектронное изделие, выполняющее определённую функцию преобразования и обработки сигнала и имеющее высокую плотность упаковки электрически соединённых элементов и компонентов, которое с точки зрения требований к испытаниям, приёмке, поставке и эксплуатации рассматривается как единое целое.

Плёночная ИМС – интегральная микросхема, все элементы и межэлементные соединения которой выполнены в виде

плёнок. Плёночные ИМС подразделяются на тонкоплёночные и толстоплёночные.

Гибридная ИМС – интегральная микросхема, содержащая кроме элементов компоненты и кристаллы.

Полупроводниковая ИМС – интегральная микросхема, все элементы и межэлементные соединения которой выполнены

в объёме и на поверхности полупроводника.

Элемент ИМС – часть интегральной микросхемы, реализующая функцию какого-либо электрорадиоэлемента, которая

выполнена нераздельно от кристалла или подложки и не может быть выделена как самостоятельное изделие с точки зрения

требований к испытаниям, приёмке, поставке и эксплуатации.

Подложка ИМС (подложка) – заготовка, предназначенная для нанесения на неё элементов гибридных и пленочных

интегральных микросхем, межэлементных и межкомпонентных соединений, а также контактных площадок.

Плата ИМС (плата) – часть подложки плёночной ИМС, на поверхности которой нанесены плёночные элементы

микросхемы, межэлементные и межкомпонентные соединения и контактные площадки.

Полупроводниковая пластина (пластина) – заготовка из полупроводникового материала, используемая для изготовления

полупроводниковых ИМС.

Кристалл ИМС (кристалл) – часть полупроводниковой пластины, в объёме и на поверхности которой сформированы

элементы полупроводниковой микросхемы, межэлементные соединения и контактные площадки.

Плотность упаковки ИМС – отношение числа элементов и компонентов интегральной микросхемы N к площади SM,

занимаемой ИМС

N

ω= .

SM

Степень интеграции ИМС Kи – показатель степени сложности микросхемы, характеризуемый числом содержащихся в

ней элементов и компонентов. Степень интеграции определяется формулой

Kи = lgN,

где N – число элементов и компонентов, входящих в ИМС. Коэффициент Kи округляется до ближайшего большего целого

числа.

Интегральная плотность элементов на подложке ω′ характеризуется числом элементов, приходящихся на единицу

площади подложки:

N 10 K и

ω′ = = ,

Sп Sп

где Sп – площадь подложки микросхемы.

Серия ИМС – совокупность типов интегральных микросхем, которые могут выполнять различные функции, имеют единое

конструктивно-технологическое исполнение и предназначены для совместного применения.

Классификация и система условных обозначений ИМС

По конструктивно-технологическому исполнению ИМС подразделяются на три группы, которым присвоены следующие обозначения:

• 1; 5; 7 – полупроводниковые;

• 2; 4; 6; 8 – гибридные;

• 3 – прочие (плёночные, вакуумные, керамические и т.д.).

По функциональному назначению ИМС подразделяются на подгруппы и виды. Например: подгруппа – логические

элементы, вид – элемент «И-ИЛИ»; подгруппа – триггеры, вид – типа j-K. Наиболее характерный признак подгруппы и вида

включается в условное обозначение ИМС.

Обозначение ИМС состоит из следующих элементов: первый элемент – цифра, обозначающая группу ИМС; второй

элемент – две цифры, обозначающие порядковый номер разработки серии ИМС (от 0 до 99); третий элемент – две буквы,

обозначающие подгруппу и вид ИМС; четвёртый элемент – порядковый номер разработки ИМС по функциональному

признаку в данной серии. Два первых элемента обозначают серию микро-схемы.

Например: полупроводниковая логическая ИМС «И-НЕ/ИЛИ-НЕ» с порядковым номером разработки серии – 21,

порядковым номером разработки данной схемы в серии по функциональному признаку – 1 имеет следующее условное

обозначение: 121ЛБ1, где 1 – группа (по конструктивно-технологическому исполнению); 21 – порядковый номер разработки

данной серии; 121 – серия; Л – подгруппа; В – вид (по функциональному назначению); 1 – порядковый номер разработки

микросхемы по функциональному признаку в данной серии.

Допускается после обозначения порядкового номера разработки серии ставить буквенные обозначения от А до Я

данного поддиапазона. Конечная буква может быть заменена цветной точкой. Значения электрических параметров

поддиапазона и цвет маркировочной точки указываются в технической документации на микросхему конкретного типа.

Для микросхем, используемых в устройствах широкого применения, в начале обозначения указывается буква «К».

Например: К121ЛБ1 – полупроводниковая ИМС серии 121, используемая в устройствах широкого применения.

Классификация питающих напряжений ИМС

Номинальные значения напряжений питания ИМС должны соответствовать следующему ряду: 1,2; 2,4; 3,0; 4,0; 5,0; 6,0;

9,0; 12,0; 15,0; 24,0; 30,0; 48,0; 100; 150; 200 B.

ИМС должны сохранять электрические параметры и пределах заданных норм при отклонениях питающих напряжений

от номинальных значений на величину, выбираемую из следующего ряда: ±10; ±20%.

Подложки микросхем

Подложки для плёночных микросхем должны удовлетворять следующим требованиям:

1. Высокая механическая прочность при малых толщинах.

2. Высокое объёмное и поверхностное удельное электрическое сопротивление и малый тангенс угла диэлектрических

потерь.

3. Температурные коэффициенты линейного расширения подложки и плёнки должны быть предельно согласованными.

4. Химическая инертность к осаждаемым веществам и травителям.

5. Физическая и химическая стойкости при нагреве до высоких температур порядка 800°С.

6. Незначительное газовыделение в вакууме.

7. Хорошая адгезия с осаждаемой плёнкой.

8. Высокий коэффициент теплопроводности.

9. Хорошая полируемость.

10. Низкая стоимость.

В полной мере перечисленным требованиям не удовлетворяет ни одна из применяемых подложек. Некоторые

требования находятся в противоречии друг к другу, например, низкая стоимость и чистота обработки поверхности подложки.

Поэтому выбор подложки основан на компромиссном решении.

Рекомендуемые размеры подложек для пленочных микросхем приведены в табл. 1.

1. Рекомендуемые размеры подложек для плёночных ИМС

Ширина в мм 30 24 20 16 16 16 12 12 10 10

Длина в мм 48 30 24 60 30 20 48 30 16 12

При изготовлении различных ИМС наиболее широко в качестве материалов для подложек и полупроводниковых

пластин используют:

• в тонкоплёночных ГИМС – ситалл, поликор, сапфир, керамику;

• в СВЧ ИМС – поликор;

• в толстоплёночных ГИМС – керамику;

• в полупроводниковых ИМС – кремний, кремний на сапфире и ситалле.

Ситалл – продукт кристаллизации стекла с мелкими (0,01 … 1 мм) кристаллитами. Получаемые при термообработке в

результате катализированной кристаллизации стекла ситаллы занимают промежуточное положение между стеклами и

керамикой.

В различные марки ситаллов входят окислы кремния (30 … 90%), остальное – окислы титана, магния, бора и др.

Поликор изготовляют из корундовой керамики, содержащей около 99,8% окиси алюминия. В поликоре удачно

сочетается относительно высокая диэлектрическая проницаемость с малыми диэлектрическими потерями на СВЧ. Кроме

того, поликор обладает хорошей полируемостью, что также снижает потери на СВЧ.

Керамические подложки сравнительно дешевы, имеют низкие потери, относительно высокую диэлектрическую

проницаемость и малые температурные изменения диэлектрических параметров. К недостаткам керамических подложек

следует отнести трудности, связанные с их полировкой (поверхность керамики после спекания всегда шероховатая), а также

относительно низкую механическую прочность. Наибольшее распространение получили две группы керамики,

отличающиеся содержанием окиси алюминия. В первую группу, для которой содержание окиси алюминия составляет 98 …

100%, входят такие керамики, как А-995, ГМ, сапфирит и др. Керамики первой группы применяются преимущественно для

подложек СВЧ микросхем.

Во вторую группу, для которой содержание окиси алюминия составляет 93 … 96%, входят такие керамики, как 22ХС,

22Х и др. Керамики второй группы применяются преимущественно для подложек толстоплёночных ИМС. Шероховатая

поверхность керамики способствует повышению адгезии при вжигании паст толстоплёночных микросхем.

Сапфир представляет собой монокристаллическую окись алюминия. Он обладает весьма малыми диэлектрическими

потерями на СВЧ, высокой теплопроводностью, механической прочностью, устойчивостью к действию высокой

температуры, влаги, излучений. На сапфире возможно гетероэпитаксиальное осаждение кремния, арсенида галлия и других

веществ, используемых для создания активных элементов и формирования на подложке микросхем типа «кремний на

сапфире». Широкое применение сапфировых подложек ограничивается трудностями его изготовления и высокой

стоимостью.

Пластины из кремния широко применяются для создания на их основе полупроводниковых микросхем. Активные и

пассивные элементы, сформированные в кремниевой пластине, изолируются друг от друга p-n переходами или

диэлектриком.

Корпуса микросхем

По форме проекции тела корпуса микросхемы на плоскость основания и расположению выводов корпуса делятся на типы,

указанные в табл. 2.

По габаритным и присоединительным размерам типы корпусов подразделяются на типоразмеры, каждому из которых

присваивают шифр, состоящий из индекса К (корпус), обозначения типа корпуса (цифра) и двузначного числа (01 … 99),

обозначающего номер типоразмера. Например: К301, К102 и т.п.

Условные обозначения корпусов состоят из:

− шифра типоразмера корпуса (без буквы К);

− цифрового индекса, определяющего количество выводов;

− порядкового регистрационного номера разработки.

2. Типы корпусов ИМС

Форма проекции тела

Расположение Расположение

корпуса на плоскость

Тип проекции выводов на выводов относительно

на плоскость

плоскость основания плоскости основания

основания

1 Прямоугольная В пределах проекции Перпендикулярное

тела корпуса

2 Прямоугольная За пределами Перпендикулярное

проекции тела

корпуса

3 Круглая В пределах проекции Перпендикулярное

тела корпуса по

окружности

4 Прямоугольная За пределами Параллельное

проекции тела

корпуса

Примечание. Корпуса, имеющие гибкие внешние выводы, которые

при необходимости могут отгибаться за пределы проекции, относятся к

корпусам двух типов одновременно.

Пример записи условного обозначения корпуса в конструкторской документации: корпус 201.14-2, где 201 – шифр

типоразмера; 14 – количество выводов; 2 – порядковый регистрационный номер.

Нумерация внешних выводов корпуса начинается от ключа и идёт против часовой стрелки, если смотреть на корпус со

стороны крышки.

По конструктивно-технологическому исполнению (конструкции) корпуса подразделяются на:

Металлостеклянные корпуса – корпуса, изготовленные из металлического основания с выводами, изолированными

стеклом. Герметизация выводов осуществляется стеклянными бусами или стеклотаблетками. Бусой изолируется каждый

вывод в отдельности, таблеткой – группа выводов.

Стеклянные – корпуса, основания которых изготовлены из стекла с впаянными в стекло выводами. Такой корпус может

иметь как стеклянные, так и металлические крышки. Для монтажа микросхем используются корпуса без металлической

площадки и с металлической площадкой.

Металлокерамические – корпуса, в которых керамическая подложка является основанием, герметизация выводов

производится припоем. Металлическая крышка корпуса припаивается к ободку, который в свою очередь припаян по

периметру керамического основания.

Керамические – корпуса, изготовленные из керамики с герметизацией выводов стеклоэмалью или стеклоприпоем.

Керамические и металлокерамические корпуса применяют преимущественно для толстоплёночных микросхем.

Пластмассовые – корпуса, изготовленные из пластмассы с выводами, впрессованными в процессе литья или

герметизации. Пластмассовые корпуса широко применяются для полупроводниковых микросхем при массовом

производстве.

Металлополимерные – корпуса, в которых для защиты ИМС используется металлическая крышка, выводы

герметизируются заливкой компаундом.

29. Конструкции интегральных микросхем и микропроцессоров: классификация интегральных микросхем по конструктивно-технологическим признакам. Требования к конструкции интегральных микросхем.

30. Принцип работы мультиплексоров, демультиплексоров и синтеза комбинационных схем на их основе.

31. Интегральные микросхемы Классификация по конструктивно-технологическим признакам., особенности применения, назначение, основные характеристики.

32. Требования к конструкции интегральных микросхем. Основные требования к конструкции, параметры, характеризующие конструктивные требования.

33.

http://www.studmed.ru/docs/document39063/%D1%80%D0%B5%D1%84%D0%B5%D1%80%D0%B0%D1%82-%D1%81%D1%82%D1%80%D1%83%D0%BA%D1%82%D1%83%D1%80%D1%8B-%D0%B8%D0%BD%D1%82%D0%B5%D0%B3%D1%80%D0%B0%D0%BB%D1%8C%D0%BD%D1%8B%D1%85-%D1%81%D1%85%D0%B5%D0%BC?page=2

СОДЕРЖАНИЕ

ЦИФРОВЫЕ ЭЛЕКТРОННЫЕ СХЕМЫ 2

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ 2

ТРАНЗИСТОРНО-ТРАНЗИСТОРНАЯ ЛОГИКА (ТТЛ) 4

ВЫХОДНОЙ КАСКАД С АКТИВНОЙ НАГРУЗКОЙ 7

МОНТАЖНАЯ ЛОГИКА 8

ВЫХОДНЫЕ СХЕМЫ С ТРЕМЯ СОСТОЯНИЯМИ 10

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ 12

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ НА КМОП-СТРУКТУРАХ 14

ЗАПОМИНАЮЩИЕ УСТРОЙСТВА 18

ОРГАНИЗАЦИЯ ЗУ С ПРОИЗВОЛЬНЫМ ДОСТУПОМ 18

ВНУТРЕННЯЯ ОРГАНИЗАЦИЯ ЗУ С ПРОИЗВОЛЬНЫМ 20

ДОСТУПОМ ДВУМЕРНАЯ АДРЕСАЦИЯ 21

ЗУ С ВНУТРЕННЕЙ ДВУНАПРАВЛЕННОЙ ШИНОЙ ДАННЫХ 23

ВЫБОРКА СТОЛБЦА С ПОМОЩЬЮ СЕЛЕКТОРА ДАННЫХ 24

ЭЛЕКТРОННЫЕ СХЕМЫ ОПЕРАТИВНОЙ ПАМЯТИ 25

ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ 33

КЛАССИФИКАЦИЯ PLD 34

ОСНОВНЫЕ СВОЙСТВА PLD 42

ВЫБОР АРХИТЕКТУРЫ PLD 47

МЕТОДИКА ПРОЕКТИРОВАНИЯ НА ОСНОВЕ PLD 49

ОБЛАСТИ ПРИМЕНЕНИЯ PLD 53

ОСНОВНЫЕ СТРУКТУРЫ CPLD 54

ПРОГРАММИРУЕМЫЕ ПОЛЬЗОВАТЕЛЕМ ВЕНТИЛЬНЫЕ 62

МАТРИЦЫ (FPGA)

Вентили диодно-транзисторной логики.

Вентили с резистивной и активной нагрузкой.

Монтажная логика.

Вентили с 3-мя состояниями.

Вентили И-НЕ и ИЛИ-НЕ на n-канальных МОП-транзисторах (структура «металл-оксид-полупроводник»).

КМОП-инвертор (комплементарная структура «металл-оксид-полупроводник»).

КМОП-вентили И-НЕ и ИЛИ-НЕ.

Вентили диодно-транзисторной логики. Вентили с резистивной и активной нагрузкой. Монтажная логика. Вентили с 3-мя состояниями. Вентили И-НЕ и ИЛИ-НЕ на n-канальных МОП-транзисторах (структура «металл-оксид-полупроводник»). КМОП-инвертор (комплементарная структура «металл-оксид-полупроводник»). КМОП-вентили И-НЕ и ИЛИ-НЕ.

1 ЦИФРОВЫЕ ЭЛЕКТРОННЫЕ СХЕМЫ

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Логический элемент, или вентиль,— это схема, реализующая одну из основных логических функций. В оставшейся части этой главы мы рассмотрим полупроводниковые логические элементы различных типов, уделив особое внимание тем, которые производятся в настоящее время в виде интегральных схем.

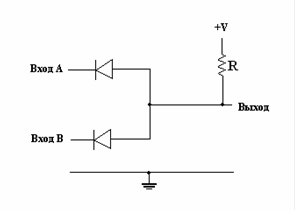

Чтобы проиллюстрировать некоторые основные понятия, характеризующие работу логических элементов, наверное, полезно будет начать с наиболее простых схем, а именно с диодных вентилей. Один из таких вентилей изображен на рис. 1. Он состоит из двух диодов и резистора. Эта схема должна представлять логический 0 и логическую 1 потенциалами соответственно 0 В и V В. У вентиля два входа А и В. Если на оба входа подается потенциал +V В, то на выходе также установится потенциал +V В, т. е. на обоих входах и на выходе мы имеем логическую 1. Однако если какой-либо из входов имеет нулевой потенциал (логический 0), то на выходе установится потенциал, близкий к нулю, поскольку диод на входе с нулевым потенциалом будет смещен вперед и через него потечет ток, причем падение напряжения на проводящем диоде мало ввиду его незначительного сопротивления. Поведение этой схемы соответствует логической функции И, поскольку логическая 1 наблюдается на выходе тогда и только тогда, когда па обоих входах логическая 1.

Рисунок 1 - Диодный вентиль.

Такой диодный вентиль оказывается полезным в некоторых применениях, но его широкому использованию в качестве логического элемента препятствуют два присущих ему недостатка. Первый недостаток заключается в том, что потенциал на выходе оказывается чувствительным к небольшим вариациям в уровне потенциала на входе. Особенно сильно этот недостаток проявляется, когда на одном из входов логический 0. В этом случае любое отклонение от идеального нулевого потенциала на входе приводит к такому же точно отклонению в величине выходного потенциала, вдобавок некоторое отклонение от нулевого напряжения на выходе обусловлено ненулевым падением напряжения на диоде, имеющим прямое смещение.

Подобная чувствительность к колебаниям входного сигнала может привести к серьезным нарушениям, если диодные вентили включены последовательно,— в этом случае отклонения будут накапливаться при прохождении сигнала от одного вентиля к другому.