Методы Изоляции элементов друг от друга в микросхемах 7 страница

Таким образом в устройствах семейства XC7300 (FB-блоки) применяются только D-триггеры; в семействах MACH1,2, XC7300 (FFB-блоки) и XC9500 - D или T триггеры; в остальных CPLD в качестве регистров могут использоваться D, T, JK или SR триггеры. Кроме того, в устройствах семейств XC7300 (FB-блоки), MACH2,3,4,5 и MAX5000 регистры могут работать в режиме прозрачной защелки (latchs).

В случае реализации комбинационной логики макроячейки всех CPLD допускают возможность программирования путей для обхода триггера сформированным сигналом. В устройствах семейства XC7300 (FB-блоки) для этого используется программный перевод триггера в режим прозрачной защелки.

Выбор типа триггера влияет на сложность логических функций, управляющих входами триггера. Путем выбора подходящего типа триггера в некоторых случаях удается упростить проект и “вложить” его в структуру CPLD с меньшими функциональными возможностями.

Сигналы управления триггеров делятся на глобальные, общие для всего устройства или PAL-блока, и локальные, формируемые непосредственно в макроячейке.

Глобальные сигналы управления регистрами обычно используются для общего управления всем проектом или его отдельными частями. Глобальные сигналы могут поступать со специальных входов по отдельным цепям, обеспечивающих минимальный “перекос” и большой коэффициент расширения по входам; формироваться с помощью генератора синхросигналов на основании внешних опорных синхросигналов (семейства MACH3,4) или формироваться на промежуточных шинах матрицы И.

Локальные сигналы служат для индивидуального управления триггером, а также для построения асинхронных и апериодических проектов. Локальные сигналы как правило, формируются на промежуточных шинах матрицы И, подсоединяемых к макроячейке.

С целью экономии общих ресурсов трассировки CPLD для управления триггерами следует стремиться максимально использовать выделенные входы и специальные цепи глобальных сигналов управления.

Триггеры рассматриваемых CPLD могут управляться следующими глобальными сигналами:

синхронизации GCLK;

сброса GCLR (кроме семейств MAX5000 и XC7300);

установки GPRN (кроме MAX-устройств и семейства XC7300); а также локальными сигналами:

синхронизации CLK (кроме устройств семейств MACH1,2);

сброса CLR (кроме устройств семейств MACH1,2);

установки PRN(кроме устройств семейств MACH1,2).

Триггеры CPLD семейств MAX7000 и FLEX 10K дополнительно могут управляться локальным сигналом разрешения синхронизации ENA.

Назначение внутренней логики внешним выводам

В идеальном CPLD любой сформированный внутренней логикой сигнал может быть назначен любому внешнему выводу. Это свойство дает целый ряд преимуществ:

можно параллельно выполнять разработку логики CPLD и конструкции печатной платы;

все внешние выводы общего назначения можно считать логически эквивалентными между собой, что значительно упрощает решение задач трассировки печатной платы будущего устройства;

исключительно просто вносятся изменения в проект, связанные с переназначением сигналов, и др.

Названное свойство выполняется только для сравнительно простых CPLD семейства XC9500. Это достигается благодаря снижению быстродействия (формируемые сигналы дважды проходят через матрицу переключений) и увеличению размеров матрицы переключений, что неизбежно связано с удорожанием всего устройства и также ведет к снижению быстродействия.

В устройствах со структурой на рис.34,а каждая макроячейка жестко связана с определенным внешним выводом. В общем случае возможно переназначение сигналов в пределах одного PAL-блока путем его перепрограммирования. Однако не все макроячейки одного PAL-блока эквивалентны между собой:

крайние макроячейки могут иметь различное число промежуточных шин, по сравнению с внутренними макроячейками;

цепи переноса и каскадирования могут не связывать крайние макроячейки и др.

Передача логического сигнала внешнему выводу, принадлежащему другому PAL- блоку, в устройствах со структурой на рис.34,а связана с необходимостью задействования ресурсов матрицы переключений и макроячейки другого PAL-блока.

В устройствах семейств MACH3,4 для упрощения назначения внутренних сигналов внешним выводам служит матрица переключения выходов, которая позволяет назначить в пределах одного и того же PAL-блока любой сформированный сигнал любому внешнему выводу. Однако введение в структуру PAL-блока дополнительной матрицы переключений снижает общее быстродействие устройства.

В устройствах семейства MACH5 (рис.34,б) назначение сигналов PAL-блоков внешним выводам в пределах одного и того же сегмента упрощается благодаря наличию локальной матрицы переключений. Однако назначение сигнала внешнему выводу из другого сегмента будет требовать задействования ресурсов глобальной матрицы переключений, локальных матриц данного и другого сегментов, а также макроячейки PAL-блока другого сегмента.

В устройствах семейств MAX9000 и FLEX-логики со структурой на рис.34,в нет жесткой зависимости между формируемыми сигналами и внешними выводами. Здесь назначение внутренней логики конкретному выводу полностью определяется ресурсами каналов трассировки. В некоторых случаях, когда каналы трассировки заняты, передача сигналов может осуществляться путем задействования свободных логических элементов LAB-модулей.

Управление входными и выходными сигналами

Обрабатываемые с помощью CPLD входные сигналы и формируемые выходные сигналы поступают в устройство и выводятся из него, как правило, с помощью двунаправленных выводов общего назначения. В некоторых CPLD в качестве входов могут также использоваться специальные (dedicated) входы.

Большинство CPLD имеют традиционные для PLD комбинационные парафазные входы. Однако устройства семейств MAX9000 и FLEX-логики допускают буферизацию входных сигналов в регистрах, а семейств MACH4 и XC7300 в регистрах или защелках.

Для большинства CPLD выходной буфер не выполняет никаких логических преобразований сигналов, а служит лишь для согласования с внешними схемотехническими требованиями: приведению сигналов к необходимым уровням

напряжений, увеличения мощности и др.

Выходные буферы всех CPLD позволяют управлять третьим высокоипедансным состоянием для отключения от внешней шины. Сигналы разрешения выходов могут быть как глобальными GOE (MAX7000, MAX9000, MACH1,2, FLEX-логика), так и локальными OE (MAX5000, MAX9000, MACH3,4, FLEX-логика). В случае локального управления выходным буфером вывод в один момент времени может быть входом, а в другой - выходом. Данное свойство может, например, использоваться при построении сдвиговых регистров.

Выходные буферы устройств семейств MAX5000, MAX7000, MACH1,2,3, XC7300 и XC9500 комбинационные, а семейств MAX9000, MACH4,5 и FLEX-логики содержат регистр. Регистры выходных буферов устройств семейства MAX9000 и FLEX-логики могут синхронизироваться глобальными или локальными сигналами синхронизации. Кроме того, для семейств MAX9000 и FLEX 10K допускается локальный сигнал разрешения синхронизации ENA.

Выходные буферы некоторых CPLD допускают программное управление:

открытым стоком (open-drain) для FLASH и FLEX 10K;

скоростью нарастания/спада сигнала (slew-rate) для MAX7000, MAX9000, FLEX-логики и XC9500;

подсоединением неиспользуемых выводов к “земле” для уменьшения системного “шума” (XC9500);

градацией соотношения скорость/мощность (MACH5) и др.

Кроме того, выходные буферы последних поколений CPLD удовлетворяют ряду схемотехнических стандартов таких, как PCI (подсоединения периферийных компонент), BST (тестирования граничным сканированием), ISP (программирования в системе), ICR (перенастройки в системе) и др.

ПРОГРАММИРУЕМЫЕ ПОЛЬЗОВАТЕЛЕМ ВЕНТИЛЬНЫЕ МАТРИЦЫ (FPGA)

Общее описание

Программируемые пользователем вентильные матрицы (Field Programmable Gate Arrays - FPGA) впервые были разработаны фирмой Xilinx в 1985 году. Фирма Xilinx свои FPGA иногда называет матрицами логических ячеек (МЛЯ - Logic Cell Array - LCA). В отличие от вентильных матриц, программируемых с помощью масок во время изготовления, FPGA программируются пользователем. Настраиваемыми элементами в FPGA являются программируемые мультиплексоры. Настройка FPGA на заданное функционирование выполняется всякий раз перед началом ее работы. Необходимая для этого программа настройки предварительно записывается в ПЗУ (ОЗУ). Сразу после включения питания выполняется загрузка информации из ПЗУ и осуществляется автоматическая инициализация FPGA (для этого FPGA содержит необходимые логические схемы). Допускается также выполнение настройки FPGA под управлением микропроцессора или микроконтроллера.

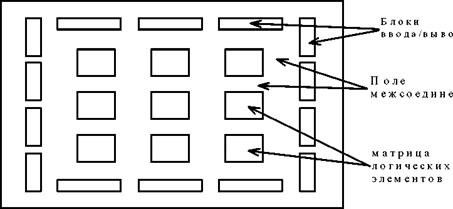

Рисунок 35 - Обобщенная структура FPGA XC2000, XC3000, XC4000

FPGA имеет типичную структуру вентильной матрицы (рис.35). В центре FPGA находится матрица настраиваемых логических блоков (Configurable Logic Blocks - CLBs), пространство между которыми заполнено программируемыми межсоединениями (Programmable Interconnects-PIs), состоящими из горизонтальных и вертикальных каналов. По краям кристалла для согласования уровней внутренних сигналов FPGA с внешними выводами расположены блоки ввода-вывода (БВВ) (Input/Output Blocks-IOBs).

Блоки ввода-вывода

Блоки ввода-вывода (БВВ) необходимы для согласования внутренних и внешних уровней логических сигналов, усиления сигналов до необходимой нагрузочной способности, защиты внутренних цепей FPGA от электрических повреждений и др. В рассматриваемых FPGA блоки ввода-вывода могут программироваться для согласования либо с ТТЛ, либо с CMOS уровнями сигналов.

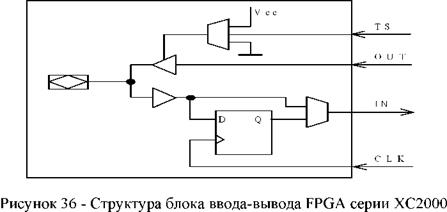

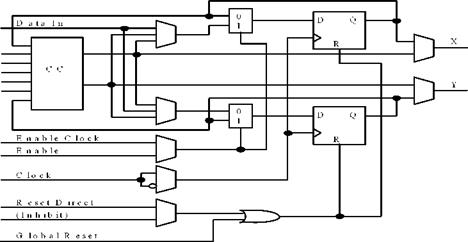

Структура БВВ серии XC2000 показана на рис.36. Он содержит цепи для согласования уровней сигналов, два программируемых мультиплексора, D-триггер и цепи управления. Путем программирования входной сигнал IN с внешнего вывода во внутренние цепи FPGA может поступать либо непосредственно, либо через D-триггер. В свою очередь выход OUT может быть отключен от блока ввода-вывода (OFF), постоянно включен (ON), либо его третье состояние может управляться сигналом TS, формируемом во внутренних цепях FPGA. Выход и вход блока ввода-вывода связаны цепью обратной связи. Поэтому если вывод не используется, то соответствующий ему блок ввода-вывода можно задействовать в реализуемой FPGA схеме в качестве элемента памяти или буфера внутренних сигналов.

Цепи согласования уровней сигналов обеспечивают на внешнем выводе силу тока до 4 mA. D-триггеры всех блоков ввода-вывода синхронизируются общим сигналом CLK. Сброс триггеров осуществляется во время инициализации при включении питания, а также во время функционирования низким уровнем общего входа RESET.

Рисунок 37 - Структура блока ввода-вывода FPGA серии XC3000

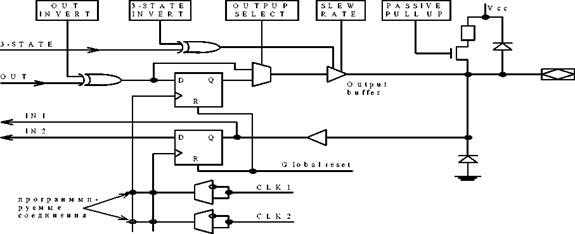

Блок ввода-вывода FPGA серии XC3000 (рис.37) организован аналогично. Дополнительно он содержит D-триггер для выходного буфера, причем входные и выходные триггера синхронизируются разными сигналами: CK1 и CK2 . Во внутренние цепи FPGA из блока ввода-вывода поступают одновременно два входных сигнала: прямой IN1 и буферизированный IN2 . Предусмотрена возможность программировать полярность выходного сигнала (OUT INVERT) и сигнала, управляющего третьим состоянием (3- STATE INVERT), возможен также обход сигналом OUT выходного буфера (OUTPUT SELECT). Режим SLEW RATE позволяет несколько снизить скорость передачи выходных сигналов, что уменьшает амплитуду пиков и системных шумов. Добавлена также возможность включать нагрузочное сопротивление для неиспользуемых "плавающих" выводов (PASSIVE PULL UP) с целью уменьшения шумов.

| S | LEW |

| R | ATE |

О

о

S3

O U T

о

С]

С]

I N 1

I N 2

к

о

CLK

| D Q | ||||||||

| O u tp u t | ||||||||

| > | b u ffe r | Input | ||||||

| b u ffe r | ||||||||

| P A | S | S | I V | E | ||||

| P U | L | L | U | P / | ||||

| PUL | L | D | O | W N | ||||

V cc

Q

о

DELAY

Рисунок 38 - Блок ввода-вывода FPGA серии XC4000

Блок ввода-вывода FPGA серии XC4000 показан на рис.38. В нем добавлена возможность прохождения входного сигнала через элемент задержки на несколько наносекунд для согласования с сигналом синхронизации (последний перед тем, как попасть в БВВ, должен пройти через глобальный буфер). Каждый из двух сигналов IN1 и IN2 может либо непосредственно поступать во внутренние цепи FPGA, либо проходить через буфер. Кроме того, добавлена возможность инвертировать сигнал синхронизации выходного регистра. Сила тока на внешнем выводе может достигать 12 mA, а на двух выводах, соединенным монтажным И - 24 mA. Неиспользуемые ("плавающие") выводы

могут подсоединяться как к цепи питания VCC (PASSIVE PULL UP), так и к "земле" (PASSIVE PULL DOWN).

Настраиваемые логические блоки

Настраиваемые логические блоки (CLB) предназначены для реализации логических функций, определяемых пользователем. Настройка каждого CLB определяется программированием функциональной таблицы (Look-Up Table). В общем случае CLB включает программируемую комбинационную схему (КС), элементы памяти и цепи управления. Сброс элементов памяти всех настраиваемых логических блоков может выполняется либо во время инициализации, либо в процессе функционирования подачей сигнала низкого уровня на вход RESET.

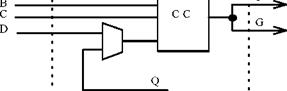

Структура настраиваемого логического блока серии XC2000 показана на рис.39. CLB имеет четыре логических входа общего назначения A, B, C и D, синхровход K и два выхода X и Y. КС может настраиваться на три конфигурации: для реализации любой булевой функции четырех переменных (рис.40); двух функций трех переменных (рис.41) динамически выбираемых двух функций трех переменных (рис.42). Последняя конфигурация является специальным случаем формы двух функций, в которой вход B динамически выбирается между двумя таблицами функций. Этот динамический выбор позволяет реализовать некоторые функции пяти переменных.

G

A

B

C

C C

S

F

D

D Q

D

D

Л

K

CC - функциональный преобразователь

Рисунок 39 - Структура универсального логического блока FPGA серии XC2000

A

F

Рисунок 40 - Конфигурация комбинационной схемы FPGA серии XC2000 для реализации

любой функции четырех переменных

Рисунок 41 - Конфигурация комбинационной схемы FPGA серии XC2000 для реализации

любых двух функций трех переменных

Рисунок 42 - Конфигурация комбинационной схемы FPGA серии XC2000 для реализации

выбора двух функций трех переменных

В качестве переменных всех реализуемых логических функций могут выступать сигналы A, B, C и D, а также выход Q элемента памяти. Элемент памяти может управляться либо асинхронно сигналами установки S и сброса R, либо синхронно. В случае синхронного управления тактирующие импульсы могут поступать со входа общей синхронизации K или с выхода комбинационной схемы G. Выходы X и Y являются полностью взаимозаменяемыми, что может использоваться для оптимизации трассировки.

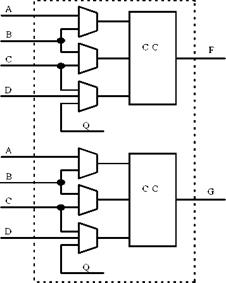

Настраиваемый логический блок для FPGA серии XC3000 (рис.43) включает два элемента памяти (на каждый выход) и соответственно две цепи обратной связи. Число логических входов общего назначения в нем увеличено до пяти, что позволяет в первой конфигурации реализовать любую функцию пяти переменных, во второй конфигурации - любые две функции четырех переменных и в третьей конфигурации - некоторые функции семи переменных.

A

B

C

D

E

E C

“ 1 ”

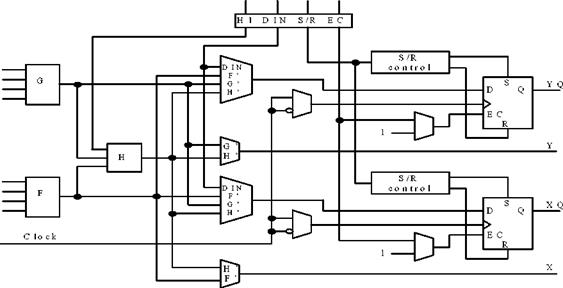

Рисунок 43 - Структура универсального логического бока FPGA серии XC3000

K

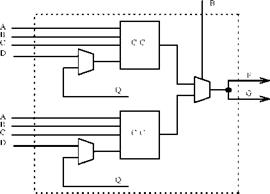

Каждый настраиваемый логический блок FPGA серии XC4000 (рис.44) содержит пару D-триггеров и два независимых 4-входовых функциональных генератора F и G , которые могут формировать на своих выходах F' и G' любые булевы функции переменных F1,...,F4 и G1,...,G4 соответственно. Третий функциональный генератор H реализует любую функцию трех переменных F', G' и внешней переменной H1 . Всего CLB FPGA серии XC4000 содержит 13 входов и 4 выхода.

C 1 C 2 C3 C 4

G 4 G 3 G 2 G 1

F 4 F 3 F 2 F 1

Рисунок 44 - Структура универсального логического бока FPGA серии XC4000

K

Сигналы от функциональных генераторов на выход CLB могут поступать двумя путями: F' и H' могут подсоединяться к выходу X, а G' и H' - к выходу Y. Таким образом CLB FPGA серии XC4000 может реализовать:

две независимых функции четырех переменных;

любую одну функцию пяти переменных;

любую функцию четырех переменных вместе с некоторой функцией пяти переменных;

некоторые функции девяти переменных.

Элементы памяти CLB управляются общим входом синхронизации K и входом разрешения синхронизации EC. Третий управляющий вход S/R может программироваться для асинхронной установки или сброса независимо для каждого триггера. На вход триггеров могут поступать значения сигналов F', G' и H' или значение сигнала DIN с прямого входа CLB.

G 4 G 3

G 2

C IN 1 C IN 2

F 4 F 3 B 0 F 2 A 0 F 1

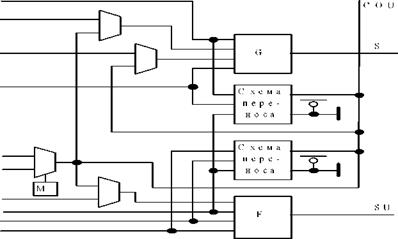

Рисунок 45 - Схема быстрого переноса XC4000

1 G 1

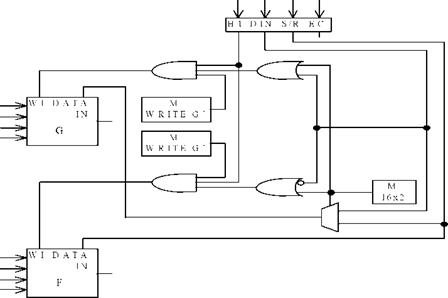

Программируемые мультиплексоры CLB управляются четырьмя внешними сигналами C1,...,C4, которые могут произвольным образом коммутироваться с внутренними сигналами H1, DIN, C/R и EC. Дополнительно функциональные генераторы FPGA серии XC4000 содержат специальную логику для быстрого формирования сигналов арифметического переноса (рис.45). Кроме того, функциональные генераторы можно использовать как быстрое ОЗУ 16x2 или 32x2 (рис.46). Линии F1-F4 и G1-G4 в этом случае являются адресными входами, линии DIN и S/R - линиями данных, а линия H1 - линией разрешения чтения/записи. Если конфигурируется ОЗУ 32x2, линия D1 становится пятым адресным входом, а линия D0 - входом данных. Время чтения ОЗУ составляет 5 ns, а записи - 6 ns.

G 4 G 3 G 2

G 4

G 3 G 2 G 1

F 4 F 3 F 2 F 1

Рисунок 46 - Использование таблиц истинности функциональных преобразователей в

качестве ОЗУ

G1

Использование CLB в качестве ОЗУ представляет новые возможности для проектирования на основе FPGA таких устройств, как регистровые матрицы, регистры состояний, индексные регистры, контроллеры DMA, сдвиговые регистры, буферы очередей, буферы стеков и др.

Программируемые межсоединения

Программируемые межсоединения (Programmable Interconnect) включают три типа коммуникаций:

основные межсоединения (General Purpose Interconnect);

длинные линии (Long Lines);

непосредственные соединения (Direct Interconnect).

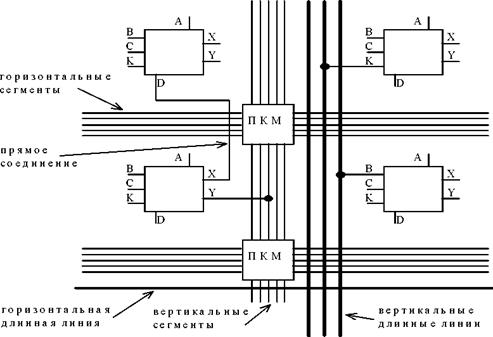

Основные соединения состоят из вертикальных и горизонтальных коммуникационных каналов (КК), образуемых металлическими проводниками, называемыми сегментами. В местах пересечения каналов располагаются программируемые коммутационные матрицы (ПКМ) (Programmable Switching Matrix), которые могут выполнять соединения любого вертикального сегмента с горизонтальным и наоборот. В FPGA серии XC2000 вертикальные коммуникационные каналы содержат пять сегментов, а горизонтальные - четыре. В FPGA серии XC3000 и вертикальные, и горизонтальные каналы содержат по пять сегментов. К любому сегменту некоторого коммуникационного канала могут подключаться любые выводы смежных с этим каналом настраиваемых логических блоков, а также блоков ввода-вывода.

Для обеспечения передачи сигналов на большие расстояния (в пределах FPGA) каждый вертикальный канал содержит три, а горизонтальный - две (для серии FPGA XC2000 - одну), длинных линии. Длинные линии не проходят через коммутационные матрицы, и длинные линии также могут присоединяться к выводам смежных с ними блоков.

Прямые соединения обеспечивают объединение выводов соседних логических блоков, при этом ресурсы коммуникационных каналов не используются. Для FPGA серии XC2000 накладываются некоторые ограничения на непосредственные соединения. Так, выход X может быть подсоединен только ко входам C или D логического блока, расположенного выше, и ко входам A или B нижнего блока. Выход Y можно подсоединить только ко входу B логического блока, расположенного справа. Фрагмент коммуникационного поля FPGA серии XC2000 показан на рис.47.

Рисунок 47 - Фрагмент программируемых межсоединений МЛЯ серии XC2000

Для обеспечения синхронной работы с малыми временными разбежками FPGA содержит специальные буферы, подсоединяемые к длинным линиям. В левом верхнем углу FPGA находится буфер, управляющий глобальной цепью, которая доступна всем входам синхронизации настраиваемых логических блоков и блоков ввода-вывода. В правом нижнем углу FPGA находится буфер, который может управлять альтернативной цепью синхронизации. В FPGA серии XC4000 горизонтальные и вертикальные длинные линии могут разрываться посередине, образуя две независимые цепи.

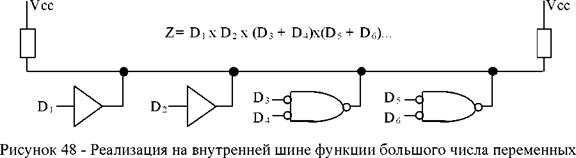

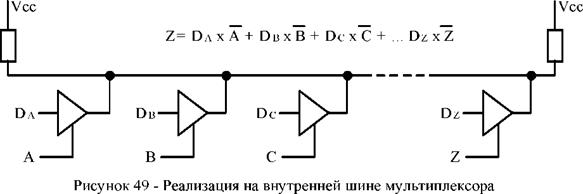

Начиная с серии XC3000 дополнительно сверху и снизу каждого ряда настраиваемых логических блоков располагаются по одной внутренней шине (Internal Busses), которые позволяют реализовать логические функции большого числа переменных. Для управления внутренними шинами каждый смежный CLB имеет пару буферов с тремя состояниями. Благодаря постоянной "подпитке" на внутренней шине можно реализовать функцию И большого числа переменных (рис.48) или мультиплексор (рис.49).

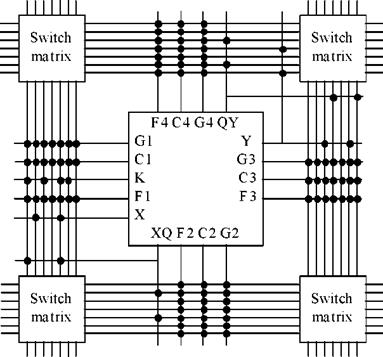

В FPGA серии XC4000 входы и выходы CLB расположены со всех четырех сторон, что предоставляет больше возможностей для трассировки (рис.50). Основные межсоединения FPGA серии XC4000 состоят из линий одинарной длины и линий двойной длины. Линии одинарной длины аналогичны основным межсоединениям предыдущих серий FPGA. Линии двойной длины предназначены для уменьшения задержек сигналов в коммуникационных матрицах. С этой целью в линиях двойной длины коммуникационные матрицы устанавливаются через два ряда CLB (рис.51).

Рисунок 50 - Типичное подсоединение универсального логического блока FPGA

серии XC4000

Ж

Ж

{Ь

-о

-о

CLB

CLB

О-

о-

о

О

о

| C L B | C L B | |||||

| Т |

о

О

f

Рисунок 51 - Линии двойной длинны FPGA серии XC4000

Тема 18 ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

1 Виды запоминающих устройств.

2 Запоминающие устройства на биполярных транзисторах.

3 Запоминающие устройства на полевых транзисторах.

1 Виды запоминающих устройств

Запоминающее устройство (ЗУ), или память,— это устройства, с помощью которого информация существует во времени, точнее, передается от одного момента к другому.

Направление передачи, совпадает с направлением движения реального времени: с движением вперед. Следовательно, ЗУ - это канал, который позволяет передать в будущее информацию, сгенерированную в настоящем. Все последовательностные схемы и компьютеры в том числе, обладают свойством запоминания, и это позволяет их выходам в данный момент зависеть от входов в предыдущие моменты. Этим свойством схемы обязаны запоминающим элементам, например триггерам. В центре нашего внимания будут структуры запоминающих устройств, состоящих из большого числа запоминающих элементов с некоторой регулярной структурой.

Организация запоминающего устройства определяет способы передачи информации в устройство и из него. Обычно информация передается порциями, состоящими из фиксированного числа битов и называемыми словами. ЗУ можно представлять себе в виде некоторого пространства, состоящего из множества идентифицируемых позиций для размещения слов.

В некоторых ЗУ на каждую такую позицию отводятся свои фиксированные запоминающие элементы. В этом случае местоположение запоминающих элементов однозначно определяет позицию слова, называемую ячейкой. В других ЗУ слова перемещаются относительна множества запоминающих элементов, сохраняя упорядоченность относительно друг друга. В этом случае позиция слова идентифицируется как временем, так и местоположением запоминающих элементов.

Во всех случаях, когда слово информации передается в ЗУ, оно помещается в некоторую конкретную позицию. Этот процесс называется записью в память. С другой стороны, когда информация передается из памяти, она также выбирается из некоторой конкретной позиции, (обычно информация в этой позиции сохраняется). Этот процесс называется считыванием из памяти.

Существуют различные способы выбора той позиции, для которой производится операция записи или чтения. Средства выбора позиции, и передачи информации в позицию или из нее образуют средства доступа (или выборки).

ЗУ делятся на два главных типа:

1 ЗУ с произвольным доступом и

2 ЗУ с последовательным доступом.

К первому типу относят ЗУ, в которых доступ к любой позиции требует примерно одного и того же времени. Другими словами, мы можем наугад выбрать позицию, и это не отразится на времени, которое затрачивается на чтение или запись.

Ко второму типу относят ЗУ, доступ к которым возможен лишь в определенном порядке. В последующих разделах мы рассмотрим ЗУ обоих названных типов.

Организация ЗУ с произвольным доступом

Память с произвольным доступом — это такое ЗУ, в котором элемент данных, запомненный в ячейке, может быть непосредственно считан. Время, необходимое для выборки данной ячейки, оказывается примерно тем же, что и для любой другой ячейки. Каждая ячейка содержит фиксированное число запоминающих элементов и имеет свой идентифицирующий номер. Идентифицирующий номер, состоящий из фиксированного числа битов, называется адресом ячейки. Наличие адресов позволяет различать ячейки при обращении к ним для выполнения операций записи и чтения.

В общем случае ЗУ с произвольным доступом состоит из нескольких блоков, или модулей. Для полупроводниковой памяти модули обычно реализуются в виде отдельных интегральных схем. Состав и функции внешних сигнальных линий выбираются с таким расчетом, чтобы облегчить работу в системе с шинной организацией связей. В число таких линий входят линии для задания адреса слова, к которому производится обращение, линии, по которым передаются данные в модуль или из модуля, и несколько управляющих линий, позволяющих задать нужную операцию (запись или чтение).

Существует довольно много разновидностей модулей с набором внешних сигналов, соответствующих различным типам шин, однако большинство модулей можно отнести к одной из двух основных моделей, показанных на рис. 1.