Моделирование делителя частоты

Делитель частоты на триггерах широко используется в цифровых синтезаторах частот для получения сетки частот от высокостабильного источника (например, кварцевого генератора). Последовательным включением триггеров осуществляется увеличение длительности выходного импульса, что равносильно уменьшению частоты. В нижеследующем примере рассматривается один из вариантов делителя частоты, выполненный на JK-триггерах.

Задание 2

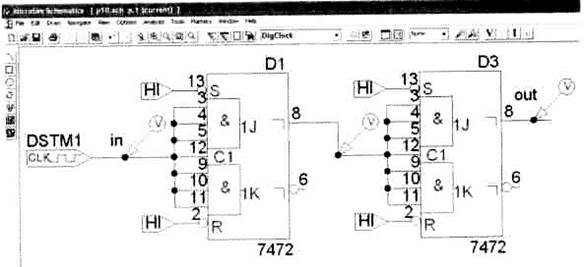

1. Выполните графический ввод схемы делителя частоты в соответствии с приведенным рисунком 2-22 и таблицей 2-4. Для выбора JK-триггера нажмите кнопку выбора компонентов и в раскрывшемся окне Part Browser Basic нажмите кнопку Libraries (библиотеки), в поле Library выберите библиотеку EVAL.slb, в поле Part — компонент 7472, после чего нажмите кнопки ОК, затем Place & Close (ввести компонент и закрыть диалоговое окно). Подайте на инверсные входы предустановки в единичное состояние (S) и сброса в нулевое состояние (R) уровень логической единицы для устранения неопределенности. Для этого нажмите кнопку выбора компонентов и в раскрывшемся окне Part Browser Basic нажмите кнопку Libraries (библиотеки), в поле Library выберите библиотеку PORT.slb, а в поле Part — компонент HI (уровень логической единицы), после чего нажмите кнопки ОК, затем Place & Close.

Рис. 2-22. Схема делителя частоты на JK- триггерах

В качестве источника сигнала используйте компонент DigClock, параметры которого также установите в соответствии с любым вариантом из таблицы. Соедините все входы триггера, включив режим рисования проводников, с источником сигнала.

Табл. 2-4.

Табл. 2-4.

Варианты заданий для моделирования делителя частоты

| Вариант | К-т деления частоты | Атрибуты источника сигнала DigClock | ||

| DELAY | ONTIME | OFFTIME | ||

| 1u | 0,5u | 0,5u | ||

| 0,2u | 1u | 1u | ||

| 0,8u | l,5u | l,5u | ||

| 0,3u | 0,9u | 0,9u | ||

| 0,5u | 2u | 2u |

2. Расположите на входе и выходе схемы (прямой выход) маркеры для измерения сигналов, используя команду Markers/Mark Voltage.

3. Сохраните схему. Задайте необходимые параметры директивы моделирования переходных процессов (Analysis Setup/Transient): конечное время анализа (Final Time = 10u), временной шаг расчета характеристик (Step Ceiling = 50n) и интервал между точками отсчета при выводе результатов моделирования (Print Step = 50n).

4. В окне Analysis Setup нажмите кнопку Digital Setup и в раскрывшемся окне в поле Flip-flop Initialization (установка начального состояния триггеров) активизируйте опцию All 0 (все в нулевое состояние). Закрыв окно Analysis Setup, запустите режим моделирования командой Analysis/Simulate или нажатием клавиши F11.

5. В окне программы Probe по графикам входного и выходного сигналов определите коэффициент деления частоты (увеличения длительности импульсов).

6. Добавьте в схему еще один JK-триггер, выполните необходимые соединения и осуществите моделирование схемы. Убедитесь в увеличении длительности импульсов на выходе последнего триггера.