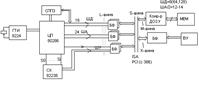

Орг эвм типа ibm pc at

L-шина обладает пониженным напряж питания(напр пит ЦП)

S-шина нормальная магистраль 5В. Первое поколение- ISA шины следующее PCI. Как вариант PCI была шина VESA.

М-шина (шина подкл памяти)

Х-шина обращения к ВУ.

ША/2-потому что динамич память (адр строки, адр столбца)

Базовый магистральный кристалл VL82C100- контроллер ВУ (84 конт, 2 контр ПДП 82237, 2 контр прерываний, таймер)

VL82C101-сист контр(генератор тактовык импульсов 8224, сист контр 88238,СППЗ 80287) с пониженным питанмем.

VL82C102-контроллер ДОЗУ

Протокол обмена по системной шине ISA (такой же как у про-цессора 1810ВМ86) каждый обмен выполн за 4 такта. 1 такт состояния 2 такт-командный.

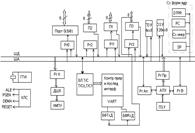

Любая ЭВМ содержит: ЦП, ГТИ, модули ПЗУ, модули ОЗУ, таймер, контролер прерыв(м/б и ПДП), устр упр вв/выв (ППИ), устр последов вв/выв.

Если все эти устр-ва установить на одном кристалле то получится однокристальная ЭВМ (транспьютер).

Однокристальн ЭВМ

Микроконтроллеры 4 разр. Их прямое назначение:

1)Калькуляторы 2)Пульты ДУ 3)ИК интерфейс.

Intel MCS51

Это контроллер клавиатуры, таймер видеомагнитофонов. 8051 n-МОП технология где 0 вид ПЗУ, 0-ПЗУ масочного изг с фиксированной прошивкой. 3-ПЗУ однопрограммируемое ПЗУ(8351) 7-ПЗУ сУльтрафиол стиранием(30-50раз) 9-Flash память (1000-10000 перепрогр).

8х31- где 31-внутреннего ПЗУ нет, есть возможность подкл внешн ПЗУ.

8хС51 где С – КМОП технология »20мА.

Наиболее популярна МС89С51.

Контроллер имеет 4 || универсальных 8-разр порта, каждый из которых имеет альтернативную функцию. Кристалл гарвардского типа: память команд и данных раздельна. При обращении к данным использ Рг DTPR встроенное ОЗУ-128b ПЗУ-4kb. Имеется возм подкл внешнего ПЗУ 64kb и ОЗУ 64kb. Проц имеет 111 команд включая команды * и /. Есть возможность побитной установки и обработки разрядов портов и флагов. В проце содерж 32 РОНа. Они делятся на 4 банка и карта адреса выглядит след образом: в спец Рг задается какой банк РОНов работает.

RS0-RS1 указывает на номер банка.

RS0-RS1 указывает на номер банка.

80Н-порт 0

equ-порт 0=80Н обращение к ячейке 80Н

89Н ТМОD – установка режима таймера.

Блок таймеров содержит 2 16-ти разр многофукц таймера (0-3 режима). ГТИ: 12MHz за 12 тактов 1 команда в режиме таймера.

Контр прерыв и послед инткрф обр 5 разл прерываний (2 внешних, 2тиаймера и послед интерф). Посл интерф работает в полудуплексном реж-ме и поддерж стандарт протоколы обмена типа RS. Порт 0 исп-ся для ввода вывода байта(как обычный Рг +ШФ), в альтернативном реж-ме порт 0 обеспечивает формирование младшего байта адр и прием данных пр подкл внешн ОЗУ и ПЗУ. Порт 2 то же самое сто и порт 0 но при подкл внешн ОЗУ и ПЗУ формир старш байт адр. Порт 1 вв/выв 8 сигналов, альтернатив нет. Порт 3 каждый бит имеет альтернативную функцию. Dip40- 40 ножек. Альтернативные функции: TxD,RxD –сигнал послед-го интерфейса. T/C0,T/C1-сигналы таймера, сч-ка; RD,WR –чтение/запись при обращении к внеш. памяти данных или внеш. ОЗУ; INT0, INT1- прерыв. по внеш событиям; ALE-строб адреса, по сигналу ALE происходит защелкивание адреса (порта 0) во внешний Рг при обращении в внешн памяти прогр или данных. PSEN- сигнал чтения из внешн памяти прогр. DEMA- 0-блокировка внутр ПЗУ,работа в внешт ПЗУ, 1-наоборот.