Вопрос 27.Векторный процессор.

Векторный процессор— это процессор, в котором операндами некоторых команд могут выступать упорядоченные массивы данных — векторы. Векторный процессор может быть реализован в двух вариантах. В первом он представляет собой дополнительный блок к универсальной вычислительной машине (системе). Во втором — векторный процессор — это основа самостоятельной ВС.

Рассмотрим возможные подходы к архитектуре средств векторной обработки. Наиболее распространенные из них сводятся к трем группам:

• конвейерное АЛУ;

• массив АЛУ;

• массив процессорных элементов.

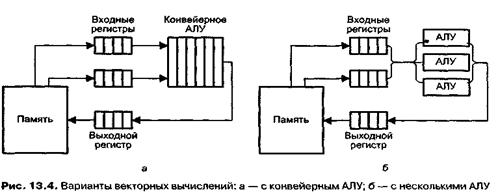

Последний вариант — один из случаев многопроцессорной системы, известной как матричная ВС. Понятие векторного процессора имеет отношение к двум первым группам, причем, как правило, к первой. Эти две категории иллюстрирует рис. 8.4

Рис.8.4.Варианты векторных вычислений: а – с конвейерным АЛУ; б – с несколькими АЛУ

В варианте с конвейерным АЛУ (рис. 8.4, а) обработка элементов векторов производится конвейерным АЛУ для чисел с плавающей запятой (ПЗ).

Структура векторного процессора

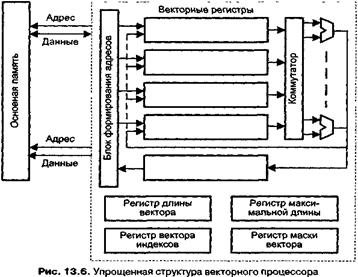

Обобщенная структура векторного процессора приведена на рис. 8.6. На схеме показаны основные узлы процессора, без детализации некоторых связей между ними.

Рис.8.6. Упрощенная структура векторного процессора

Обработка всех п компонентов векторов-операндов задается одной векторной командой. Общепринято, что элементы векторов представляются числами в форме с плавающей запятой (ПЗ). АЛУ векторного процессора может быть реализовано в виде единого конвейерного устройства, способного выполнять все предусмотренные операции над числами с ПЗ. Более распространена, однако, иная структура, — в ней АЛУ состоит из отдельных блоков сложения и умножения,а иногда и блока для вычисления обратной величины.

Вопрос 28.Фронтальные ВМ.

Фронтальная ВМ (ФВМ) соединяет матричную SIMD-систему с внешним миром, используя для этого какой-либо из сетевых интерфейсов, напримерEthernet, как это имеет место в системе MasPar MP-1. Фронтальная ВМ работает под управлением операционной системы, чаще всего UNIX-подобной. На ФВМ пользователи подготавливают, компилируют и отлаживают свои программы. Перед выполнением программы сначала загружаются из фронтальной ВМ в контроллер массива процессорных элементов, который исполняет последовательную часть программы и распределяет распараллеленные команды и данные по процессорным элементам массива. В некоторых ВС при создании, компиляции и отладке программ КМП и фронтальная ВМ используются совместно.

На роль ФВМ подходят различные вычислительные машины. Так, в системе CM-2 в этом качестве выступает рабочая станция SUN-4, а в системе MasPar — DECstation 3000.

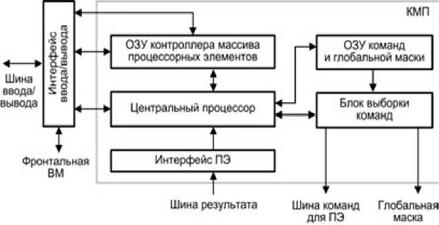

Контроллер массива процессорных элементов выполняет последовательный программный код, реализует команды ветвления программы, транслирует команды и сигналы управления в процессорные элементы. Рисунок 8.11 иллюстрирует одну из возможных реализаций КМП, в частности принятую в устройстве управления матричной вычислительной системы PASM.

Рис. 8.11. Модель контроллера массива процессорных элементов

При загрузке из ФВМ программа через интерфейс ввода/вывода заносится в оперативное запоминающее устройство контроллера массива процессорных элементов (ОЗУ КМП). Команды для процессорных элементов и глобальная маска, формируемая на этапе компиляции, также через интерфейс ввода/вывода загружаются в ОЗУ команд и глобальной маски (ОЗУ КГМ). Затем контроллер начинает выполнять программу, извлекая либо одну скалярную команду из ОЗУ КМП, либо множественные команды из ОЗУ КГМ. Скалярные команды — команды, осуществляющие операции над хранящимися в КМП скалярными данными, выполняются центральным процессором (ЦП) контроллера. В свою очередь, команды, оперирующие параллельными переменными, хранящимися в каждом ПЭ, преобразуются в блоке выборки команд в более простые единицы выполнения — нано команды. Нано команды совместно с маской пересылаются через шину команд для ПЭ на исполнение в массив процессорных элементов. Например, команда сложения 32разрядных слов в КМП системы MPP преобразуется в 32 нано команды одноразрядного сложения, которые каждым ПЭ обрабатываются последовательно.

В большинстве алгоритмов дальнейший порядок вычислений зависит от результатов и/или флагов предшествующих операций. Для обеспечения такого режима в матричных системах статусная информация, хранящаяся в процессорных элементах, должна быть собрана в единое слово и передана в КМП для выработки решения о ветвлении программы. Например, в предложении IF ALL (условие A) THEN DO B оператор В будет выполнен, если условие А справедливо во всех ПЭ. Для корректного включения/отключения процессорных элементов КМП должен знать результат проверки условия А во всех ПЭ. Такая информация передается в КМП по однонаправленной шине результата. В системе CM-2 эта шина названа GLOBAL. В системе MPP для той же цели организована структура, называемая деревом SUM-OR. Каждый ПЭ помещает содержимое своего одноразрядного регистра признака на входы дерева, которое с помощью операции логического сложения комбинирует эту информацию и формирует слово результата, используемое в КМП для принятия решения.