Сумматоры с последовательным переносом

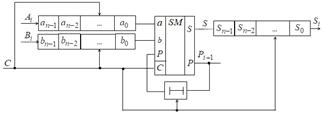

Многоразрядный комбинационный сумматор последовательного действия (рисунок 14.7) представляет собой структуру, состоящую из двух сдвигающих регистров  ,

,  , одноразрядного сумматора и схем управления.

, одноразрядного сумматора и схем управления.

Рисунок 14.7 – Многоразрядный комбинационный

Сумматор последовательного действия

Порядок функционирования последовательного сумматора следующий. Перед началом суммирования сдвигающие регистры  ,

,  , и триггер устанавливаются в нулевое состояние. Затем производится запись чисел

, и триггер устанавливаются в нулевое состояние. Затем производится запись чисел  и

и  в регистры

в регистры  ,

,  соответственно. После этого производится суммирование чисел

соответственно. После этого производится суммирование чисел  и

и  поразрядно, начиная с младшего разряда. В первом такте суммирования на один вход сумматора поступает цифра

поразрядно, начиная с младшего разряда. В первом такте суммирования на один вход сумматора поступает цифра  , а на другие два входа – цифры

, а на другие два входа – цифры  и

и  с выходов регистров. На выходе сумматора формируется цифра младшего разряда суммы

с выходов регистров. На выходе сумматора формируется цифра младшего разряда суммы  и цифра переноса

и цифра переноса  . Цифра переноса подается на вход триггера для задержки на один такт, а цифра

. Цифра переноса подается на вход триггера для задержки на один такт, а цифра  поступает через схему "ИЛИ" на вход старшего разряда

поступает через схему "ИЛИ" на вход старшего разряда  . После окончания действия первого импульса цифра переноса

. После окончания действия первого импульса цифра переноса  появляется на выходе триггера, одновременно происходит сдвиг содержимого регистров на один разряд вправо и в освободившийся старший разряд

появляется на выходе триггера, одновременно происходит сдвиг содержимого регистров на один разряд вправо и в освободившийся старший разряд  записывается

записывается  . На втором такте на вход сумматора будут поступать цифры

. На втором такте на вход сумматора будут поступать цифры  , а на его выходе будут образовываться цифры

, а на его выходе будут образовываться цифры  . Далее обработка информации будет производиться так же, как в первом цикле.

. Далее обработка информации будет производиться так же, как в первом цикле.

Таким образом, весь цикл суммирования занимает  тактов, результат суммирования записывается в

тактов, результат суммирования записывается в  .Результат сложения будет верным, если число разрядов суммы не превышает разрядность регистра

.Результат сложения будет верным, если число разрядов суммы не превышает разрядность регистра  . Если же указанное условие не выполняется, то будет иметь место искажения результата, вызванного переполнением разрядной сетки.

. Если же указанное условие не выполняется, то будет иметь место искажения результата, вызванного переполнением разрядной сетки.

Результат сложения

(14.6)

(14.6)

может быть записан в специальный регистр суммы.

Быстродействие последовательного сумматора определяется временем сложения

, (14.7)

, (14.7)

где  – число разрядов в регистрах;

– число разрядов в регистрах;

– время сдвига кода в регистрах;

– время сдвига кода в регистрах;

– время образования суммы в сумматоре.

– время образования суммы в сумматоре.

Сумматоры с ускоренным переносом

3.1. Сумматоры с ускоренным переносом

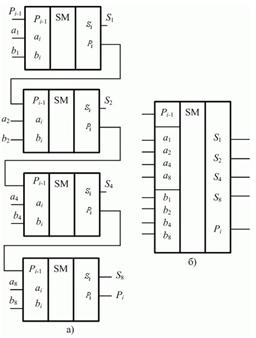

Полные одноразрядные сумматоры являются основой, из которых получают различные схемы многоразрядных сумматоров.

Сумматор параллельного действия содержит одноразрядные сумматоры, число которых равно разрядности суммируемых двоичных слов.

Для того чтобы получить многоразрядный сумматор из полученного выше одноразрядного сумматора, достаточно соединить входы и выходы переносов соответствующих двоичных разрядов.

Для сложения многоразрядных двоичных чисел необходимо последовательно соединить нужное количество сумматоров так, как показано на рисунке 14.8. Здесь  и

и  – 4-разрядные слагаемые,

– 4-разрядные слагаемые,  – 4-разрядная сумма.

– 4-разрядная сумма.

Рисунок 14.8 – Четырехразрядный сумматор: