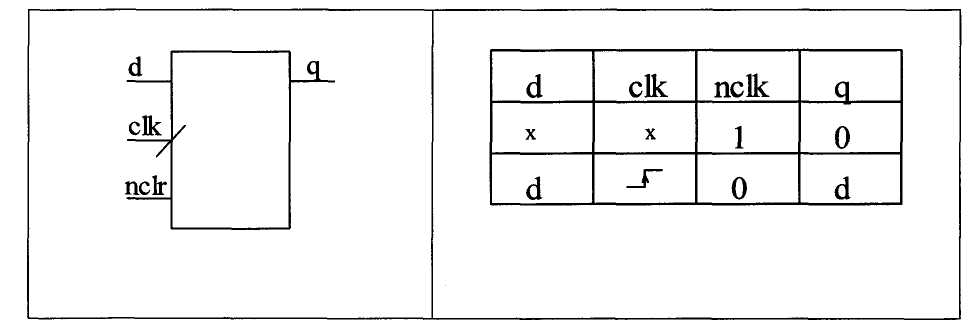

D-триггер с асинхронным сбросом

Library ieee;

Use ieee.std_logic_l164.all;

Entity tr is

Port (d, clk, nclr: in std_logic;

q: out std_logic); end tr;

architecture beh of tr is

Begin

Process (nclr, clk)

Begin

If nclr='0' then q<='0';

elsif clk=' 1' and clk'event --(номожноитак:elsif clk='1' and not clk'stable)

then q<=d;

End if;

End process;

End beh;

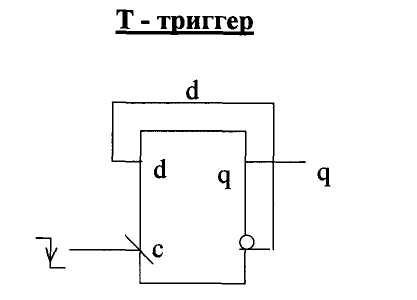

Т-триггер - это счетный триггер. Он срабатывает по отрицательному фронту тактового импульса. Его описание приведено ниже:

Libraryieee;

Useieee.std_logic_l164.all;

Entity T is

Port ( c: in std_logic;

q: out std_logic); end T;

architecture beh of T is

Signal d: std_logic :='0';

Begin

Process(c)

Begin

if c='0' and с'event then

d <= not d; q <= d;

End if;

Endprocess;

Endbeh;

Основные операции в VHDL. Приоритеты операций.

В языке VHDL имеются операции следующих категорий:

1. Логические операции

2. Операции отношений

3. Операции сложения/вычитания

4. Операции умножения/деления

5. Прочие

Приоритет операций возрастает от категории 1 к категории 5. Операции одной категории имеют одинаковый приоритет и выполняются в последовательности: слева направо. Скобки используются для изменения последовательности исполнения.

Операции логические

Существует шесть логических операций: and, or, nand, nor, xor, not.

Операции применимы к типам BIT, BOOLEAN, к одноразмерным массивам BIT и BOOLEAN. При выполнении битовые значения ‘0’ и ‘1’ интерпретируются как булевские FALSE и TRUE. Результат имеет тот же тип, что и операнды. Операция not – унарная операция, она имеет приоритет категории 5.

Операции отношений

В языке VHDL имеются следующие операции отношений:

=, /=, <, <=, >, >=

Результатом выполнения любой операции отношений является булевское выражение BOOLEAN. Операции равенства ( = ) и неравенства ( /= ) допустимы со всеми типами, за исключением типа “файл”. Остальные четыре операции допустимы над скалярными типами (целочисленными, перечислимыми) или над массивами дискретного типа. Когда операндами являются массивы, то сравнение выполняется слева направо по одному элементу

Операции суммирования, вычитания, конкатенации

Операции имеют обозначения:

+, -, &.

Операнды, участвующие в операциях сложения ( + ) и вычитания ( - ) должны быть одного числового типа, результат оказывается того же типа. Операндами в конкатенации ( & ) могут быть или отдельные элементы или одномерные массивы. Результат выдается в виде массива, например при выполнении конкатенации:

‘0’ & ‘1’

образуется массив символов “01”, или еще пример:

‘C’ & ‘A’ & ‘T’

дает “CAT”.

Операции умножения, деления

К этой группе оператций относятся: *, /, mod, rem.

Операнды умножения ( * ) и деления ( / ) должны быть одновременно либо целочисленного типа (integer) либо типа с плавающей запятой (floating point). Результат всегда того типа, что и операнды. Операция умножения может иметь один операнд физического типа, а другой – либо целочисленного, либо натурального типа. Результат выдается в виде физического типа.

В операции деления допустимо делить объект физического типа на целочисленный или натуральный. Результат - всегда физического типа. Деление физического типа на физический дает целочисленный результат.

Операции остатка ( rem ) и “деления по модулю” ( mod ) в качестве операндов могут иметь целочисленные типы и результат - целочисленного типа. Результат rem имеет знак первого операнда и определяется следующим образом:

A rem B = A - ( A / B ) * B

Результат mod имеет знак второго операнда и определяется следующим образом:

A mod B = A – B * N,

где N – некоторое целое.

Прочие операции

К их числу следует отнести: Abs, ** и другие. Операция выделения абсолютного значения ( abs ) совместима с любым числовым типом операнда. Операция возведения в степень ( ** ) операндом слева имеет целое или тип с плавающей точкой, а в качестве правого операнда (степень) - только целое.

61. Типы std_ulogic и std_logic.

Каждый тип данных в VHDL имеет определенный набор принимаемых значений и набор допустимых операций.

1. STD_LOGIC(битовый) - представляет один бит данных . Объекты

данного типа могут принимать 9 состояний. Данный тип определён

стандартом IEEE1164 для замены типа BIT.

( BIT (битовый) - содержит значение 0 или1)

2. STD_ULOGIC(только для одного источника), то же, что и STD_LOGIC, только в нем не определена функция разрешения, используемая для определения значения сигнала, имеющего

несколько источников (драйверов).