Вибір елементної бази і складання функціональної схеми

Структурна схема пристрою управління цифрового автомата

При проектуванні пристрою управління може бути використаний принцип схемою (жорсткій) або програмованої логіки.

Т.к. проектований пристрій призначений для вирішення вузької спеціалізованої задачі і об'їм виконуваних команд малий доцільно застосувати принцип схемної логіки.

Рисунок 1 – Структурна схема пристрою управління

Структурна схема, зображена на малюнку 1 пояснює принцип побудови цифрового автомата за принципом жорсткої логіки.

Стан цифрового автомата зберігається в перебігу такту. Тому управляючий пристрій повинен мати в своєму складі елементи запам'ятовують пристроїв, представлених у вигляді паралельного регістра стану (рисунок 1). Код мікрокоманди характеризуючий стан цифрового автомата в перебігу одного такту зберігається в пристрої, що запам'ятовує. Як пристрою, що запам'ятовує, використовується паралельний регістр. Код першої команди записується в регістр автоматично під час запуску автомата, а перехід до наступних команд здійснюється за допомогою сигналів зворотного зв'язку. Сигнали зворотного зв'язку формуються за допомогою дешифратора команд (дешифратор стану ТАК — рисунок 1).

1.2 Розробка дешифратора станів

1.2 Розробка дешифратора станів

Запишемо коди стану пристрою управління і переведемо їх в двійковий код.

NMK1=910= 10012

NMK2=1110=10112

NMK3=1310=11012

NMK4=1510=11112

MK1=108;

MK2=109;

MK3=119;

MK4=219.

Вхідними сигналами для дешифраторів є прямий або інверсний вихід тригерів регістра (залежно від того, на якому з них в даному стані повинен з'явитися сигнал логічної «1»). Слід зазначити, що в кодах змінюються 4 розряди, відповідності зі своїми 4-ма розрядами кодів станів дешифратори реалізують следуючі логічні функції:

DC1 =

DC2 =

DC3 =

DC4 =

Таблиця 1 — Таблиця переходів

| № стану | Код стану | Прехід | Адреса подачі сигналів зворотнього зв’язку | |

| DEC | BIN | |||

| 0 ®9 | Вх: S0 S3 | |||

| 9®11 | DC1: J1 | |||

| 11®13 | DC2: J2, K1 | |||

| 13®15 | DC3: K2 | |||

| 15 ®0 | DC4: R1 |

По даній таблиці складаємо схему подачі сигналів зворотного зв'язку.

1.3 Розробка шифратора

Управляючі сигнали формуються комбінаційним пристроєм (перетворювач n - разрядного коду МК в m - разрядный код).

Складаємо таблицю роботи шифратора. В якості вхідних сигналів використовуються виходи розрядів регістра станів Q0 – Q4, вихідними є сигнали на вихідних шинах (Y1 – У7).

Таким чином, отримано табличне значення логічних функцій У0 - У7. Для їх реалізації представимо функції у алгебраїчній формі і по можливості мінімізуємо їх за допомогою карт Карно.

Таблиця 2 - таблиця роботи шифратора

| Код стану регистру | Q3 | Q2 | Q1 | Q0 | Код управл. сигналом | Y7 | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0 |

Прості функції:

Y =

Y =

Y =

Y =

Мінімізуємо складні функції.

Мінімізуємо складні функції.

| ~ | ~ | ~ | ||

| ~ | ~ | ~ | ~ | |

| ~ | ~ | |||

| ~ | ~ |

Y5 =

| ~ | ~ | ~ | ||

| ~ | ~ | ~ | ~ | |

| ~ | ~ | |||

| ~ | ~ |

Y3 =

| ~ | ~ | ~ | ||

| ~ | ~ | ~ | ~ | |

| ~ | ~ | |||

| ~ | ~ |

Y2 =

| ~ | ~ | ~ | ||

| ~ | ~ | ~ | ~ | |

| ~ | ~ | |||

| ~ | ~ |

Y1 =

| ~ | ~ | ~ | ||

| ~ | ~ | ~ | ~ | |

| ~ | ~ | |||

| ~ | ~ |

Y5 =

По отриманих виразах будується схема шифратора на елементах І-НЕ, відповідно до завдання.

1.4 Розрахунок генератора тактових імпульсів

1.4 Розрахунок генератора тактових імпульсів

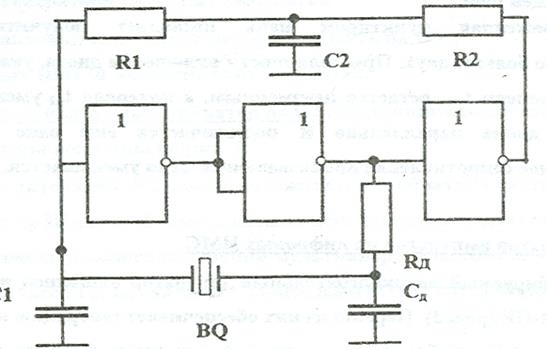

Рисунок 2 – Схема генератора імпульсів на кварцовому резонаторі

1.5 Вибір елементної бази і складання функціональної схеми

R1C2R2- образують коло зворотнього зв’язку по постійному струмі та виконують роботу в режимі м’якого самовозбуждения.C1-дозволяє підстроювати в невеликих пределах частоту генератора.Сд та Rд – перешкоджають самовозбуждение генератора на частотах більших ніж резонансна частота кварцового резонатора.

R1 та R2 не повинні перевищувати велечину,обєспєчівающую роботу першого елемента в лінійному режимі.

Un1=1.5 B

U03=0.3 B

I0BX1=1.6 mB

R1+R2=750 B

R1 = R2 = 330 Ом

C2>>T/R де Т період повторення імпульсів

Т=Р+Г=2+1=3мкс

Задоємося С2=10 нФ тоді :

10*10-9=(3*10-6)/R

Звідки R=(3*10-6)/(10*10-9)=300 Ом

Вибір елементної бази і складання функціональної схеми

Наведена схема в графічній частині курсового проекту побудована на елементах І-НЕ, відповідно до завдання.

Таблица – Элементы схемы графической части

| Наименование | Количество |

| JKC - тригер | |

| Чотирьохвходовий | |

| Двохвходовий |

До складу управляючого пристрою входить генератор тактових імпульсів і дешифратори станів, що забезпечують послідовне виконання всіх мікрокоманд.

Стан пристрою управління (код мікрокоманди) фіксується і зберігається в 5-х розрядному паралельному регістрі, побудованому на JК-трігерах. Для перекладу трігера в новий стан використовуються інформаційні входи. Інформаційний вхід Jслужить для перекладу трігера в стан «1» (`Q = 0, Q = 1), вхід K - для установки трігера в «0» (Q = 0,`Q = 1). Спрацьовування трігера, за наявності сигналів на входах J і K відбувається тільки при подачі синхронізуючого імпульсу на вхід С. Асинхронні входи R і S є  настановними, тобто використовуються для однократної установки трігера в початковий стан «1» (по входу S) або скидання в «О» (по входу R). Установка проводиться в будь-які моменти часу.

настановними, тобто використовуються для однократної установки трігера в початковий стан «1» (по входу S) або скидання в «О» (по входу R). Установка проводиться в будь-які моменти часу.

Початковий стан регістра визначається кодом першої мікрокоманди і фіксується шляхом установки в «1» або в «0» відповідних розрядів регістра. При цьому на виході дешифратора першого стану DС1 формується сигнал зворотного зв'язку для перекладу регістра в наступний стан, відповідний другій мікрокоманді (МК2). Сигнал з виходу DС1 подається на інформаційні входи K і J трігерів відповідно, помінявши їх стани. Перехід регістра в новий  стан відбувається з приходом чергового синхроімпульса. Після чого формується сигнал на виході дешифратора DС2 і т.д. Сигнал з виходу дешифратора DС4 скидає всі трігери в стан «0» по входах K.

стан відбувається з приходом чергового синхроімпульса. Після чого формується сигнал на виході дешифратора DС2 і т.д. Сигнал з виходу дешифратора DС4 скидає всі трігери в стан «0» по входах K.

|

Висновки:

Висновки:

Курсова робота приведена і розрахована вище складається з 2-х частин. Перша частина присвячена розробці цифрового автомата або пристрою управління. Друга частина присвячена програмуванню мікропроцесора на мові асемблера.

Проведена робота допомогла з'ясувати матеріал по курсу «Основи цифрової і мікропроцесорної техніки». Крім того, другу частину курсового проекту вдалося здійснити практично на установці «Мікролаб».

При рішенні задач курсового проекту, а також при оформленні його використовувалися програма Microsoft Word, яка використовувалася для оформлення текстової частини курсової роботи.

Нормативно-технічна література та документація

Нормативно-технічна література та документація

| Номер документа і рік видання | Назва документа |

| ГОСТ 2.743 - 72 | ЕСКД. Обозначения условные графические в интегральных микросхемах |

| ГОСТ 2.104 – 68 | ЕСКД. Основные надписи |

| ГОСТ 2.105 – 79 | ЕСКД. Общие требования к текстовым документам |

| ГОСТ 2.109 – 73 | ЕСКД. Основные требования к чертежам |

| ГОСТ 2.702 – 75 | ЕСКД. Обозначения условные и графические схемы |

| ДСТУ 2397-94 | Мікропроцесори .Терміни та визначення . |

|

Список літератури

1. Гонтаренко Г.М., Крыжановская Н.Г. Формирование и измерение сигналов в импульсной технике. - М.:Изд-во Стандартов, 1992.

2. Гонтаренко Г.М., Крыжановская Н.Г. Основы цифровой и микропроцессорной техники. Конспект лекций. Часть 1. - Одесса: РИО, Колледж, 1993.

3. Гонтаренко Г.М., Крыжановская Н.Г. Основы цифровой и микропроцессорной техники. Конспект лекций. Часть 2. - Одесса: РИО, Колледж, 1993.

4. Цифровые и аналоговые интегральные микросхемы: Справочник / Под ред. С.В. Якубовского. - М.: Радио и связь, 1990.