Вывод по данной лабораторной работе

АРХИТЕКТУРА ЭВМ И СИСТЕМ

ИССЛЕДОВАНИЕ РАЗЛИЧНЫХ ВИДОВ ТРИГГЕРОВ

Выполнил студент

10-БАС

Дмитриев Р.Э..

Преподаватель:

ст. преп.

Филиппов Р.А.

Брянск 2012

СОДЕРЖАНИЕ

| 1. Цель работы | |

| 2. Теоретическая часть | |

| 2.1. Понятие триггера и его основные свойства | |

| 3. Порядок выполнения работы | |

| 4. Вывод по данной лабораторной работе | |

Цель работы

Используя программу Or CAD, выполнить программное моделирование указанной схемы RS-, JK-, D-триггера и исследовать его работу с помощью полученных временных диаграмм, подав предварительно на входы триггеров сигналы.\

Теоретическая часть

Понятие триггера и его основные свойства

Простейшим логическим элементом с памятью является триггер.

Триггер (flip-flop) — это устройство с двумя устойчивыми состояниями, одно из которых — логический ноль, а другое — логическая единица. Синоним триггера — двухстабильная схема (bistable circuit).

Триггер представляет собой электронную схему, содержащую активные элементы, которая способна сохранять в течение длительного времени одно из двух устойчивых состояний: логический ноль или логическую единицу.

Существует множество вариантов схем триггеров, но все их объединяет наличие двух важных свойств.

1. Триггер является двухстабильным элементом. При отсутствии сигналов на входах любой триггер пребывает в одном из двух состояний и остается в нем сколь угодно долго. Таким образом, триггер является элементарной ячейкой памяти емкостью 1 бит.

2. Триггер имеет два выхода, сигналы на которых всегда взаимно инверсные. Принято обозначать эти выходы как Q и  .

.

Триггеры, в отличие от комбинационных схем, относятся к другому виду цифровых устройств — цифровым автоматам. В цифровых автоматах набор выходных сигналов зависит не только от входных сигналов, но также от внутреннего состояния самого элемента.

Триггеры, в отличие от комбинационных схем, относятся к другому виду цифровых устройств — цифровым автоматам. В цифровых автоматах набор выходных сигналов зависит не только от входных сигналов, но также от внутреннего состояния самого элемента.

Различают несколько разновидностей триггеров: RS-триггер, D-триггер, JK-триггер.

Порядок выполнения работы

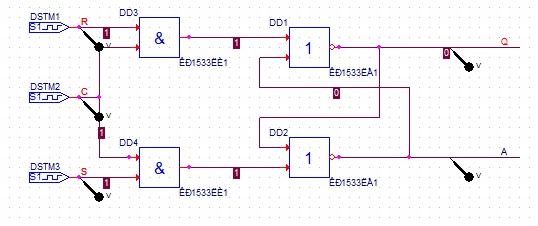

Рассмотрим порядок выполнения работы на примере выполнения следующего задания. Необходимо смоделировать с помощью программы Or CAD Capture 9.2 электронно-логическую схему синхронного RS-триггера на основе логических элементов ИЛИ-НЕ, проанализировать его работу, построив временные диаграммы для заданной комбинации сигналов, подаваемых на входы логических элементов, приведенной в табл. 1.

Таблица 1.

| вход. сигнал | t1 | t2 | t3 | t4 | t5 | t6 |

| R | ||||||

| S |

Ход работы:

1. Открыть программу OrСAD.

2. Создать новый проект.

3. Создать схему синхронного RS-триггера на основе логических элементов ИЛИ-НЕ.

3.1. Соединить элементы, используя команду (Place->Wire);

3.2. Подать на входы и выходы питание (Place->Part-> Source->Stim1);

3.3. Получить электронно-логическую схему, изображенную на рис.1;

Рис. 1.

4. Подать на входы сигналы.

4.1. Щелкнуть два раза левой клавишей мыши на источник питания;

4.2. Подать указанную комбинацию сигналов на входы схемы синхронного RS-триггера, составленного из логических элементов ИЛИ-НЕ.

4.3. Установить время работы схемы равное 10 секундам (PSpice>New Simulation Profile >Run to time=10s).

5. Получить временные диаграммы работы синхронного RS-триггера (PSpice>Run) (рис.2).

Рис. 2. Временные диаграммы работы синхронного RS-триггера на основе логического элемента ИЛИ-НЕ.

6. Проанализировать работу синхронного RS-триггера, составленного из логических элементов ИЛИ-НЕ.

Вывод по данной лабораторной работе

Используя программу Or CAD, выполнить программное моделирование указанной схемы RS-триггера и исследовал его работу с помощью полученных временных диаграмм, подав предварительно на входы триггера сигналы.