ВОЛОГОДСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

Кафедра «Управляющие и вычислительные системы»

Организация ЭВМ и систем.

Методические указания по курсовому проектированию

Факультет – электроэнергетический

Направление 230100 «Информатика и вычислительная техника»

Вологда

УДК 681.3(075)

Организация ЭВМ и систем: Методические указания по курсовому проектированию. – Вологда: ВоГТУ, 2010. – 26 c.

В методических указаниях приведены примеры заданий на курсовое проектирование дисциплине «Организация ЭВМ и систем» для студентов направления 230100 «Информатика и вычислительная техника». Также в них излагаются общие сведения о проектировании электрических принципиальных схем вычислительных систем и приводятся требования к содержанию и оформлению расчетно-пояснительной записки к курсовому проекту.

Утверждено редакционно-издательским советом ВоГТУ

Составитель: Машкин А. В., канд. техн. наук, доцент каф. УВС ВоГТУ

Рецензент: Анкудинов В. Б., канд. техн. наук, доцент каф. АВТ ВоГТУ

ВВЕДЕНИЕ

Современные вычислительные машины (ВМ) и вычислительные системы (ВС) являются одним из самых значительных достижений научной и инженерной мысли, влияние которого на прогресс во всех областях человеческой деятельности трудно переоценить.

Несмотря на различия современных ВМ в них можно обнаружить много общего и соответственно дать определение ВМ. Так согласно ГОСТ 15971-90 электронной вычислительной машиной (ЭВМ) называется совокупность технических средств создающих, возможность проведения обработки информации и получение результата в необходимой форме с необходимым программным обеспечением, основные функциональные устройства которой выполнены на электронных компонентах.

Эффект, достигаемый за счет применения вычислительной техники, возрастает при увеличении масштабов обработки данных, т. е. концентрации по возможности больших объемов данных и процессов их обработки в рамках одной технической системы. Крупномасштабные системы обработки данных можно создавать, повышая производительность ЭВМ или объединяя многие ЭВМ в вычислительные комплексы и сети.

Методы проектирования и эксплуатации вычислительных комплексов, систем и сетей разрабатываются в рамках теории вычислительных систем. При этом считается, что термин «вычислительная система» охватывает и вычислительные, и управляющие, и информационно-измерительные системы, построенные на основе ЭВМ, многомашинных и многопроцессорных комплексов и вычислительных сетей.

Вычислительные, управляющие и информационно-измерительные системы, центральным обрабатывающим элементом которых служит микропроцессор (МП) относятся к числу микропроцессорных систем (МПС). МП называется построенная на базе одной интегральной микросхемы программно-управляемое устройство, осуществляющие процесс обработки информации и управления им. Отличия МП от обычных микросхем заключаются в том, что в своем составе он содержит управляющие элементы, позволяющие его настроить на выполнение практически любых функций, т.е. на реализацию практически любых зависимостей между последовательностями входных и выходных электрических сигналов. Очевидно, что если эти электрические сигналы будут являться носителями информации, то на основании любого МП можно реализовать систему обработки информации.

Совокупность интегральных микросхем, пригодных для совместного применения с каким-либо типом МП называют микропроцессорным комплектом (МПК). Понятие МПК задает номенклатуру микросхем с точки зрения возможностей их совместного применения (совместимость по архитектуре, электрическим параметрам, конструктивным признакам и др.) В состав МПК могут входить микросхемы различных серий и схемотехнологических типов при условии их совместимости.

1. ТЕХНИЧЕСКОЕ ЗАДАНИЕ

В курсовом проекте студентам предлагается разработать вычислительную систему (решающую ограниченное число функций) на базе МП КР580ВМ80А (аналог процессора i8080) и соответствующего ему МПК. Несмотря на достаточно многолетний возраст этого МП его применение при курсовом проектировании оправдано следующими причинами:

1) Имеющаяся на этот МП и МПК, соответствующий ему достаточно подробная техническая документация [1, 2] и др.;

2) Большинство из входящих в МПК КР580 микросхем это аналоги микросхем, установленных на системной плате первой модели IBM PC (персонального компьютера с процессором Intel семейства x86; например, таймер КР580ВИ53 это аналог микросхемы i8253 и т.д.) [3]. Благодаря открытому описанию этих функциональных узлов, они приобрели надежный статус «неприкосновенности», гарантированный большим количеством программ и программных продуктов, использующих их. Со временем элементная база системной платы радикально изменилась, все функции отдельных контроллеров взял на себя чипсет, но программная модель этих узлов сохранилась. Поэтому в процессе выполнения курсового проекта студенты также получают знания и об этих функциональных узлах.

3) Современные ВМ и ВС выполняют гораздо больший объем функций чем устройства которые требуется реализовать в рамках курсового проектирования. Однако, для их проектирования потребовался бы гораздо больший объем знаний (в том числе и других дисциплин, изучение которых происходит позже курса «Организации ЭВМ и систем»). Из-за ограниченного объема времени отводимого на изучение дисциплины спроектировать такие системы не представляется возможным. В то же время принципы построения таких ВМ и ВС совпадают с принципами построения устройств, разрабатываемых в рамках данного курсового проекта.

4) Естественно, что предложенные для проектирования устройства, с экономической точки зрения целесообразней было бы создать на базе одного из современных микроконтроллеров. Достигнутая степень интеграции современных микросхем, позволила разместить в одном корпусе фактически весь МПК КР580. В то же время одной из целью курсового проектирования является как раз задача научить подключать студентов к МП внешние устройства и организовывать их взаимодействие.

Примеры заданий на курсовое проектирование приведены ниже.

1. Генератор псевдослучайных чисел.

2. Просмотр и возможность изменения ячеек оперативного запоминающего устройства (ОЗУ).

3. Просмотр и возможность изменения содержимого регистров МП.

4. Реализация устройства поблочного контроля четности.

5. Реализация устройства контроля переданной информации с модифицированным кодом Хемминга.

6. Устройство, имитирующие работу кодового замка.

7. Калькулятор с алгебраической логикой.

8. Калькулятор с обратной бесскобочной логикой.

10. Устройство, имитирующие работу системы управления светофором.

11. Устройство перекодирования информации.

12. Система для организации взаимодействия МП и внешних устройств при помощи контроллера прерываний.

Ввод информации в разрабатываемую систему может осуществляться как по опросу, так и по прерыванию. Варианты заданий приведены в самом общем виде, конкретное техническое задание на проектирование выдается преподавателем в начале семестра. Конченым итогом курсового проектирования должна стать разработка электрической принципиальной схемы ВС на основе МП КР580 и программы для нее.

2. ЭТАПЫ РАЗРАБОТКИ ЭЛЕКТРИЧЕСКОЙ ПРИНЦИПИАЛЬНОЙ СХЕМЫ

Схема – это графический конструкторский документ, на котором показаны в виде условных обозначений или изображений составные части изделия и связи между ними. Схемы входят в комплект конструкторской документации и содержат вместе с другими документами необходимые данные для проектирования, изготовления, сборки, регулировки, эксплуатации изделий.

Схемы предназначаются:

на этапе проектирования – для выявления структуры будущего изделия при дальнейшей конструкторской проработке;

на этапе производства – для ознакомления с конструкцией изделия, разработки технологических процессов изготовления и контроля деталей;

на этапе эксплуатации – для выявления неисправностей и использования при техническом обслуживании.

На начальном этапе студентам известны входные воздействия, подаваемые на проектируемый объект, а также функции, которые он должен выполнять. Исходя из анализа этих данных студент должен в начале спроектировать структурную схему технического устройства, которая отображает принцип работы изделия в самом общем виде. На схеме изображают все основные функциональные части изделия (элементы, устройства, функциональные группы), а также основные взаимосвязи между ними. Действительное расположение составных частей изделия не учитывают и способ связи между ними (проводная, индуктивная, количество проводов и т.п.) не раскрывают. Построение схемы должно давать наглядное представление о последовательности взаимодействий функциональных частей в изделии. Направление хода процессов, происходящих в изделии, обозначают стрелками на линиях взаимосвязи.

Функциональные части на схеме изображают в виде прямоугольников или условных графических обозначений (УГО). При обозначении функциональных частей в виде прямоугольников их наименование, типы и обозначения вписывают внутрь прямоугольников.

При большом количестве функциональных частей вместо наименований, типов и обозначений допускается проставлять порядковые номера, которые наносят справа от изображения или над ним, как правило, сверху вниз в направлении слева направо. В этом случае наименования, типы и обозначения указывают на поле схемы. При использовании цифровых обозначений вместо наименований функциональных частей наглядность схемы ухудшается, так как роль каждой функциональной части выясняется не только по изображению, но и с помощью перечня. На схеме допускается указывать технические характеристики функциональных частей, поясняющие надписи и диаграммы, определяющие последовательность процессов во времени, а также параметры в характерных точках.

Пусть, например, согласно техническому заданию следует спроектировать калькулятор с алгебраической логикой вычислений. В этом случае в проектируемой ВС должна присутствовать клавиатура для ввода информации в микропроцессорную систему (МПС), устройство индикации, позволяющие контролировать ввод исходной информации и просматривать результат вычислений. Поскольку обработка информации в МПС ведется в двоичном коде, то в проектируемой ВС должны быть блоки осуществляющие преобразования нажатий клавиш в двоичный код, а также блоки преобразующие двоичный код в код для управления устройствами индикации. Таким образом, структурная схема проектируемой ВС примет вид, изображенный на рис. 1.

1 – устройство преобразования нажатия клавиши в двоичный код;

2 – устройство преобразования двоичного кода в код для управления индикатором.

Рис. 1. Структурная схема калькулятора

Одновременно с разработкой структурной схемы ВС необходимо начать разрабатывать и алгоритм функционирования проектируемого устройства. Здесь студенту требуется проанализировать организацию интерфейса проектируемой ВС, определить ее реакцию на различные входные воздействия (как корректные, так и некорректные). Естественно, на данном этапе проектирования этот алгоритм может быть представлен только в самом общем виде.

Далее следует приступить к синтезу электрической принципиальной схемы. Принципиальная электрическая схема является наиболее полной электрической схемой изделия, на которой изображают все электрические элементы и устройства, необходимые для осуществления и контроля в изделии заданных электрических процессов, все связи между ними, а также элементы подключения (разъемы, зажимы), которыми заканчиваются входные и выходные цепи. На схеме могут быть изображены соединительные и монтажные элементы, устанавливаемые в изделии по конструктивным соображениям. Элементы на схеме изображают УГО, начертания и размеры которых устанавливаются в стандартах единой конструкторской технической документации (ЕСКД). Элементы, используемые в изделии частично, допускается изображать не полностью, а только используемые части.

Этап разработки электрической принципиальной схемы следует начать детализации алгоритма функционирования проектируемой ВС, касаемо ввода и вывода информации. Например, для проектируемого калькулятора, преобразование нажатия клавиши в двоичный код можно осуществлять аппаратно (с помощью контроллера клавиатуры, шифратора и т.д.), либо осуществлять это преобразование программным путем в МПС. Здесь же следует распределить адресное пространство МПС между микросхемами постоянных запоминающих устройств (ПЗУ) и оперативных запоминающих устройств (ОЗУ).

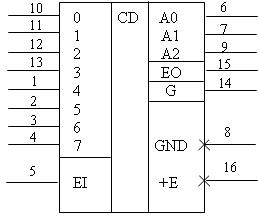

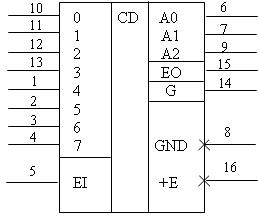

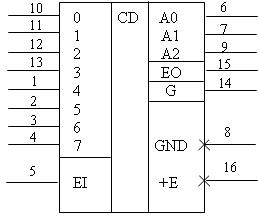

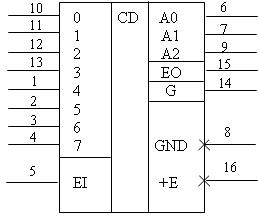

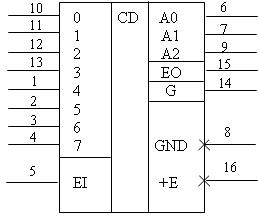

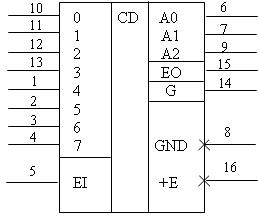

После уточнения этих деталей следует приступить к выбору элементной базы, при помощи которой ВС сможет осуществить решение требуемых от нее задач. При этом в расчетно-пояснительной записки к курсовому проекту следует приводить УГО выбранной микросхемы, таблицы описывающие назначение выводов выбранной микросхемы и режимы её работы. Для примера, на рис.2 приведено УГО микросхемы приоритетного шифратора К555ИВ2, который преобразует унитарный код поступающий на его входы в выходной двоичный код. В таблицах 1 и 2 представлено описание назначение выводов данной микросхемы и режимов ее работы. В таблице 2 применены следующие общепринятые обозначения: Х – безразличное состояние (все равно что будет на входе логическая 1 или 0); Z – высокоомное состояние. Также в справочной литературе логическая единица может обозначаться как H (от английского high – высокий), а логический ноль как L (от английского low – низкий).

Рис. 2. УГО микросхемы шифратора К555ИВ2

Таблица 1

Назначение выводов микросхемы К555ИВ2

| Вывод микросхемы | Функциональное назначение |

| 0, 1, 2, 3, 4, 5, 6, 7 | Информационные входы шифратора |

| EI | Вход разрешения работы шифратора |

| EO | Выход наращивания разрядности шифратора |

| G | Выход для фиксации сигнала на одном из информационных входов |

| GND | Общий |

| +E | Напряжение питания +5 В |

Таблица 2

Режимы работы микросхемы К555ИВ2

| EI | | | | | | | | | А2 | А1 | А0 | G | EO |

| | X | X | X | X | X | X | X | X | Z | Z | Z | | |

| | | | | | | | | | Z | Z | Z | | |

| | X | X | X | X | X | X | X | | | | | | |

| | X | X | X | X | X | X | | | | | | | |

| | X | X | X | X | X | | | | | | | | |

| | X | X | X | X | | | | | | | | | |

| | X | X | X | | | | | | | | | | |

| | X | X | | | | | | | | | | | |

| | X | | | | | | | | | | | | |

| | | | | | | | | | | | | | |

Как видно из приведенного УГО шифратора и таблицы 2 он реализует преобразование 8х3. Поскольку в калькулятор следует вводить десять цифр, а также кодировать нажатие клавиш выполнения, например, арифметических действий, то требуется произвести наращивание разрядности шифратора. Это наращивание разрядности можно выполнить в соответствии со схемой, приведенной на рис. 3. Четырехразрядный двоичный код нажатой клавиши (разряды D3-D0) формируется в отрицательной логике (уровню логической 1 соответствует низкое значение сигнала; уровню логического 0 – высокое значение сигнала). Поскольку выходы микросхемы шифратора можно переводить в третье состояние (высокоомное состояние), то для наращивания разрядности шифратора используется схема монтажного ИЛИ. В этом случае выходы микросхем DD1 и DD2 просто соединяются друг с другом. Однако, если выходы микросхемы не могут быть переведены в третье состояние. То схему монтажного ИЛИ применять нельзя и для наращивания разрядности шифратора следует использовать дополнительные логические элементы. Если на всех информационных входах DD1 присутствует логическая 1, то на выходе EO DD1 будет логический 0, на выходе G – логическая 1, а выходы A2-A0 будут переведены в высокоомное состояние. Выход ЕО DD1 соединен со входом EI DD2. Таким образом, при нажатии клавиши подключенной к DD1 на разрядах D2-D0 будет присутствовать двоичный код, соответствующий возбужденному входу микросхемы DD1, а при нажатии клавиши, подключенной к DD2 на этих разрядах присутствует двоичный код, соответствующий возбужденному входу DD2. Для формирования старшего четвертого разряда двоичного кода инвертируется сигнал с выхода G микросхемы DD1. Поскольку микропроцессорный комплект КР580 работает в положительной логике, то полученный двоичный код следует инвертировать, а кроме того следует также сформировать сигнал, извещающий микропроцессор о нажатии клавиши (на рис. 3 эти цепи не показаны).

Рис.3. Схема наращивания разрядности шифратора К555ИВ2

При выборе микросхем, включаемых в состав проектируемой ВС и не входящих в микропроцессорный комплект КР580, студенту следует быть внимательным. Поскольку микропроцессорный комплект КР580 обеспечивает совместимость с ТТЛ уровнями сигналов, то следует выбирать микросхемы либо ТТЛ серий, либо обеспечивающих совместимость с уровнями ТТЛ.

После преобразования нажатия клавиши в двоичный код возникает задача ввода этого кода в микропроцессорную систему. Эту задачу можно решить, например, при помощи микросхемы параллельного программируемого интерфейса (ППИ) КР580ВВ55А (в схеме на рис. 1 он входит в блок микропроцессорная система). УГО ППИ изображено на рис. 4.

| SR IOP BA7 WR BA6 BA5 RD BA4 BA3 CS BA2 A1 BA1 A0 BA0 GND BB7 Ucc BB6 BB5 BB4 D7 BB3 D6 BB2 D5 BB1 D4 BB0 D3 D2 BC7 D1 BC6 D0 BC5 BC4 BC3 BC2 BC1 BC0 | |

Рис. 4. УГО микросхемы ППИ КР580ВВ55А

Назначение выводов микросхемы КР580ВВ55А приведено в таблице 3, а режимы ее работы в таблице 4. Как правило, микросхемы входящие в состав микропроцессорных комплектах могут настраиваться для работы в различных режимах. Так КР580ВВ55А может настраиваться на работу в одном из трех режимов (режим 0, режим1, режим3). В режиме 0 обеспечивается возможность синхронной программно управляемой передачи данных через два независимых 8-разрядных канала ВА и ВВ и два 4-разрядных канала ВС. В режиме 1 обеспечивается возможность ввода или вывода информации в/или из периферийного устройства через два независимых 8-разрядных канала ВА и BB по сигналам квитирования. При этом линии канала ВС используются для приема и выдачи сигналов управления обменом. В режиме 2 обеспечивается возможность обмена информации с периферийным устройствами через двунаправленный 8-разрядный канал ВА по сигналам квитирования. Для передачи и приема сигналов управления обменом используются 5 линий канала ВС. Выбор соответствующего канала и направление передачи информации через него определяются сигналами А0, А1 и сигналами RD, WR, CS в соответствии с таблицей 4.

Таблица 3

Назначение выводов микросхемы КР580ВВ55А

| Вывод микросхемы | Тип вывода | Функциональное назначение |

| ВА7-ВА0 | Входы/выходы | Информационный канал А |

| ВВ7-ВВ0 | Входы/выходы | Информационный канал В |

| ВС7-ВС0 | Входы/выходы | Информационный канал С |

| А1, А0 | Вход | Разряды адреса |

RD RD | Вход | Чтение информации |

CS CS | Вход | Выбор микросхемы |

WR WR | Вход | Запись информации |

| SR | Вход | Установка в исходное состояние |

| D7-D0 | Входы/выходы | Канал данных |

| Ucc | - | Напряжение питания +5 В±5% |

| GND | - | Общий |

Таблица 4

Режимы работы микросхемы КР580ВВ55А

| Сигналы на входах | Направление передачи информации |

| А1 | А0 |  RD RD |  WR WR |  CS CS |

| Операция ввода (чтение) |

| | | | | | ВА→канал данных |

| | | | | | ВВ→канал данных |

| | | | | | ВС→канал данных |

| Операция вывода (запись) |

| | | | | | Канал данных→ВА |

| | | | | | Канал данных→ВВ |

| | | | | | Канал данных→ВС |

| | | | | | Канал данных→РУС |

| Операции блокировки |

| Х | Х | Х | Х | | Канал данных→третье состояние |

| | | | | | Запрещенная комбинация |

Режим работы каждого из каналов ВА, ВВ и ВС определяется содержимым регистра управляющего слова (РУС). Произведя запись управляющего слова (УС) в РУС, можно перевести микросхему в один из трех режимов работы: режим 0 – простой ввод/вывод; режим 1- стробируемый ввод/вывод; режим 2 – двунаправленный канал.

При подаче сигнала SR РУС устанавливается в состояние, при котором все каналы настраиваются на работу в режиме 0 для ввода информации. Режим работы каналов можно изменять как в начале, так и в процессе выполнения программы, что позволяет обслуживать различные периферийные устройства в определенном порядке одной микросхемой. Разрядность УС для программирования КР580ВВ55А составляет 8 бит. Назначение бит УС приведено в таблице 5.

Таблица 5

Формат УС КР580ВВ55А

| Разряд УС | Значение разряда УС | Задаваемый режим работы |

| D7 | | - |

| D6D5 | | Режим 0 для канала ВА и 4-7 разрядов канала ВС |

| | Режим 1 для канала ВА и 4-7 разрядов канала ВС |

| 1X | Режим 2 для канала ВА и 4-7 разрядов канала ВС |

| D4 | | Вывод из канала ВА |

| | Ввод в канал ВА |

| D3 | | Вывод из 4-7 разрядов канала ВС |

| | Ввод в 4-7 разряд канала ВС |

| D2 | | Режим 0 для канала ВВ и 0-3 разрядов канала ВС |

| | Режим 1 для канала ВВ и 0-3 разрядов канала ВС |

| D1 | | Вывод из канала ВВ |

| | Ввод в канал ВВ |

| D0 | | Вывод из 0-3 разрядов канала ВС |

| | Ввод в 0-3 разряды канала ВС |

В курсовом проекте студенту следует выбрать режим работы микросхемы и составить для него УС. Пусть, например, для всех трех каналов выбран режим 0 и каналы ВА и ВВ работают на вывод, а канал ВС на ввод. Тогда УС необходимое для программирования такого режима будет следующим – 10001001. Точно также необходимо рассмотреть режимы работы и для других микросхем из микропроцессорного комплекта КР580, включаемых в состав проектируемой ВС, проанализировать режимы их работы и выбрать подходящий. После чего следует в расчетно-пояснительной записки к курсовому проекту привести форматы УС выбранных микросхем и составить УС, в соответствии с выбранным режимом работы микросхемы. Подробную справочную информацию о микропроцессорном комплекте КР580 можно получить в [1].

Программирование периферийных микросхем осуществляется путем посылки УС в РУС (или их аналоги). Программирование периферийных микросхем может осуществляться через адресное пространство порто ввода/вывода. В этом случае обращение к регистрам периферийных микросхем должно происходить через адреса портов. Для этого необходимо в проектируемой ВС предусмотреть схему выборки, т.е. присвоить определенным регистрам периферийных микросхем определенные адреса. В микропроцессоре КР580ВМ80А адресное пространство портов ввода/вывода составляет 256 адресов. Чтение из порта осуществляется командой IN микропроцессора, вывод в порт командой OUT. В этих командах следует указать номер порта в который происходит ввод или вывод. При выполнении этих команд на младших 8 разрядах шины адреса (ША) микропроцессорной системы появляется номер порта. Эти сигналы, присутствующие на младших 8 разрядах ША и следует использовать в схеме выборки.

Например, если бы в составе проектируемой ВС присутствовала бы только одна микросхема ППИ, то можно было бы ее вход CS заземлить, а входы А1 и А0 с разрядами А1 и А0 микропроцессорной системы. В этом случае обращаться бы к каналу ВА ППИ можно было бы по номерам портов, в которых два младших двоичных разряда были бы равны 00, к каналу ВВ ППИ можно было бы по номерам портов, в которых два младших двоичных разряда были бы равны 01, к каналу ВС ППИ можно было бы по номерам портов, в которых два младших двоичных разряда были бы равны 10 и к РУС по номерам портов, в которых два младших двоичных разряда были бы равны 11. Например, канал ВА ППИ может соответствовать порту с номером 0h, канал ВВ – 1h, BC – 2h, РУС – 3h. Однако, если в составе проектируемой ВС будут присутствовать несколько периферийных микросхем, то необходимо будет организовывать более сложную схему выборку. Если число периферийных микросхем в составе проектируемой ВС относительно невелико, то для выборки можно использовать сигналы со старших линий ША. Например, если в составе проектируемой ВС имеется две микросхемы КР580ВВ55А, то их можно подключить как показано на рис. 5.

Рис. 5. Схема выборки двух ППИ КР580ВВ55А

На рис. 5 при 0 сигнале на линии А3 будет выбрана микросхема DD1, а при 1 микросхема DD2. Поэтому к каналам ВА, ВВ, ВС и РУС микросхемы DD1 можно обращаться, например, по таким номерам портов – 0h, 1h, 2h, 3h соответственно, а каналам ВА, ВВ, ВС и РУС микросхемы DD2 можно обращаться по таким номерам портов – 4h, 5h, 6h, 7h соответственно. При большем количестве периферийных микросхем схема выборки усложняется и становится целесообразным реализовывать ее не на логических элементах, а на микросхемах средней степени интеграции, например, дешифраторах [4].

Также в состав проектируемой ВС необходимо включить микросхему памяти. Микросхемы ПЗУ обязательно должны присутствовать в составе ВС, поскольку в них хранится программа и данные, которые не стираются при снятии с микросхемы питания. После включения микропроцессор начинает последовательно исполнять программу команду за командой в соответствии с изменением содержимого регистра счетчика команд микропроцессора. Физически это означает, что сразу же после включения на шине адреса формируется нулевой адрес. Поэтому необходимо чтобы адресное пространство, начиная с нулевого адреса, было занято микросхемой ПЗУ, в которой бы хранилась программа, необходимая для нормального функционирования ВС. Схему выборки микросхем памяти можно организовать наподобие схем выборки периферийных устройств. Если разрядность хранимых данных в выбранной микросхемы памяти будет меньше 8 бит, то для повышения разрядности достаточно будет объединить адресные входы выбранных микросхем. Например, для однократно программируемой микросхемы ПЗУ КР556РТ4 (УГО изображено на рис.6, а назначение выводов представлено в таблице 6) разрядность хранимых слов составляет 4 бита.

| |

| |  |

Рис. 6. УГО ПЗУ КР556РТ4

Таблица 6

Назначение выводов микросхемы КР556РТ4

| Вывод микросхемы | Назначение вывода |

| А7, А6, А5, А4, А3, А2,А1, А0 | Разряды адреса |

| D3, D2, D1, D0 | Разряды данных |

| CS0, CS1 | Выборка микросхемы |

| GND | Общий |

| +E | Напряжение питания +5 В |

Для наращивания разрядности по данным до 8 бит эти микросхемы ПЗУ могут быть соединены так, как показано на рис. 7. Поскольку для считывания информации из микросхемы КР556РТ4 необходимо, чтобы на ее входы СS0 B CS1 подавался логический 0, то эти входы заземляются.

Рис. 7. Схема наращивания разрядности данных ПЗУ КР556РТ4

Микросхемы ОЗУ применяются для хранения данных, которые могут быть изменены в любой момент времени при исполнении текущей программы. Студент должен сам решить вопрос о целесообразности применения микросхем ОЗУ в составе проектируемой ВС. Если для хранения промежуточных данных, в соответствии с алгоритмом решаемой задачи будет достаточно регистров микропроцессора, то микросхемы ОЗУ можно не применять. Но следует, учитывать, что при использовании подпрограмм, применение ОЗУ является обязательным, поскольку в этом случае при вызове подпрограммы в стеке запоминается адрес возврата, а при завершении работы подпрограммы по команде ret, этот адрес считывается из стека и помещается в регистр счетчика команд микропроцессора. На рис. 8 приведено УГО микросхемы статического ОЗУ К132РУ8, а в таблицах 7 и 8 приведена информация о назначении ее выводов и режимах работы, соответственно. В статических ОЗУ в качестве запоминающих элементов используются триггеры, которые хранят записанную в них информацию до тех пор, пока на микросхему подано напряжение питания или не произошло смены управляющих сигналов. Поэтому в отличии от микросхем динамической памяти, для микросхем статических ОЗУ не требуются внешние цепи регенерации данных [3,4,5].

| |

| |  |

Рис. 8. УГО микросхемы статического ОЗУ К132РУ8

Таблица 7

Назначение выводов микросхемы К132РУ8

| Вывод микросхемы | Назначение вывода |

| А9, А8, А7, А6, А5, А4, А3, А2,А1, А0 | Разряды адреса |

| D3, D2, D1, D0 | Разряды данных |

| CE | Выборка микросхемы |

W/ R W/ R | Сигнал записи/ чтения |

| GND | Общий |

| +E | Напряжение питания +5 В |

Таблица 8

Режимы работы микросхемы К132РУ8

| СE |  W/ R W/ R | Аi | Di | Режим работы |

| | Х | Х | ∞ | хранение |

| | | A | | запись 0 |

| | | A | | запись 1 |

| | | А | данные в прямом коде | считывание |

RD

RD  CS

CS  WR

WR  RD

RD  WR

WR  CS

CS

W/ R

W/ R  W/ R

W/ R