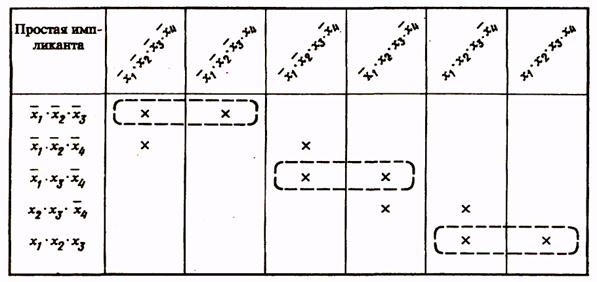

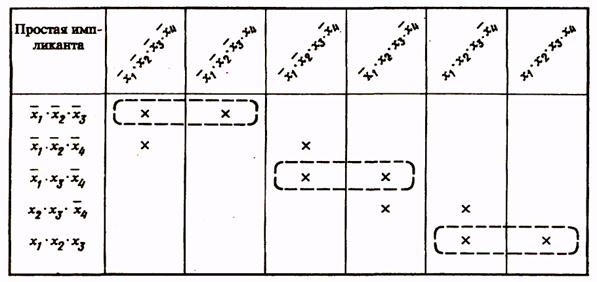

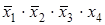

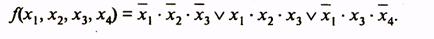

Выражение (4) представляет собой сокращенную форму логического выражения заданной функции, а члены его являются простыми импликантами функции. Переход от сокращенной формы к минимальной осуществляется с помощью импликантной матрицы, приведенной в табл. 3.

Таблица 3

В столбцы импликантной матрицы вписываются члены СДНФ заданной функции, в строки - простые импликанты функции, т.е. члены сокращенной формы логического выражения функции. Отмечаются (например, крестиками) столбцы членов СДНФ, поглощаемых отдельными простыми импликантами. В табл. 3 простая импликанта  поглощает члены

поглощает члены  ,

,  (в первом и во втором столбцах первой строки поставлены крестики).

(в первом и во втором столбцах первой строки поставлены крестики).

Вторая импликанта поглощает 1-й и 3-й члены СДНФ (крестики поставлены в первом и третьем столбцах второй строки) и т.д. Импликанты, которые не могут быть лишними и, следовательно, не могут быть исключены из сокращенной формы, составляют ядро.Входящие в ядро импликанты легко определяются по импликантной матрице. Для каждой из них имеется хотя бы один столбец, перекрываемый только данной импликантой.

В рассматриваемом примере ядро составляют импликанты  и

и  (только ими перекрываются второй и шестой столбцы матрицы). Исключение из сокращенной формы одновременно всех импликант, не входящих в ядро, невозможно, так как исключение одной из импликант может превратить другую уже в нелишний член.

(только ими перекрываются второй и шестой столбцы матрицы). Исключение из сокращенной формы одновременно всех импликант, не входящих в ядро, невозможно, так как исключение одной из импликант может превратить другую уже в нелишний член.

Для получения минимальной формы достаточно выбрать из импликант, не входящих в ядро, такое минимальное их число с минимальным количеством букв в каждой из этих импликант, которое обеспечит перекрытие всех столбцов, не перекрытых членами ядра. В рассматриваемом примере необходимо импликантами, не входящими в ядро, перекрыть третий и четвертый столбцы матрицы. Это может быть достигнуто различными способами, но, так как необходимо выбирать минимальное число импликант, то, очевидно, для перекрытия этих столбцов следует выбрать импликанту

.

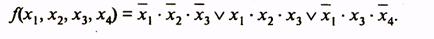

Минимальная дизъюнктивная нормальная форма (МДНФ) заданной функции

(5)

(5)

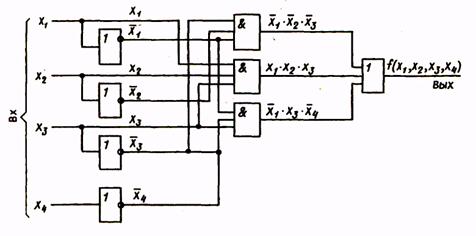

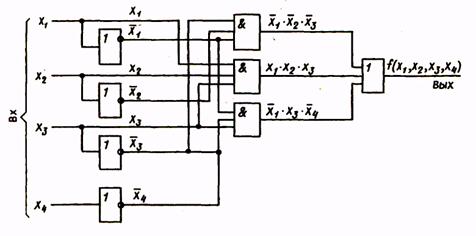

Структурная схема, соответствующая этому выражению, приведена на рис.2.

Рис. 2

До сих пор рассматривалось получение минимальной ДНФ. При использовании метода Квайна для получения минимальной конъюнктивной нормальной формы (МКНФ) логической функции имеются следующие особенности:

- исходной для минимизации формой логического выражения заданной функции является СКНФ;

- пары склеиваемых членов имеют вид w v д: и wv x;

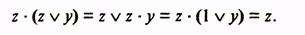

- операция поглощения проводится в соответствии с выражением

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

25. RS триггер

Триггеры широко используются для создания различных счетчиков и делителей частоты. На них строятся элементы памяти, такие как ОЗУ или регистры. Именно поэтому трудно найти работу выпускнику, который не освоил работу с триггерами. Изучение работы триггеров начнем с простейшего триггера, который называется RS триггер.

RS триггер получил название по названию своих входов. Вход S (Set — установить англ.) позволяет устанавливать выход триггера Q в единичное состояние (записывать единицу). Вход R (Reset — сбросить англ.) позволяет сбрасывать выход триггера Q (Quit — выход англ.) в нулевое состояние (записывать ноль).

Для реализации RS триггера воспользуемся логическими элементами "2И-НЕ". Его принципиальная схема приведена на рисунке 1.

Рисунок 1. Схема простейшего rs триггера на схемах "2И-НЕ". Входы R и S инверсные (активный уровень'0')

Рассмотрим принцип работы RS триггера, выполненный по изображенной на рисунке 1 схеме подробнее. Пусть на входы R и S подаются единичные потенциалы. Если на выходе верхнего логического элемента "2И-НЕ" Q присутствует логический ноль, то на выходе нижнего логического элемента "2И-НЕ" появится логическая единица. Эта единица подтвердит логический ноль на выходе Q. Если на выходе верхнего логического элемента "2И-НЕ" Q первоначально присутствует логическая единица, то на выходе нижнего логического элемента "2И-НЕ" появится логический ноль. Этот ноль подтвердит логическую единицу на выходе Q. То есть при единичных входных уровнях схема RS триггера работает точно так же как и схема на инверторах.

Подадим на вход S нулевой потенциал. Согласно таблице истинности логического элемента "И-НЕ" на выходе Q появится единичный потенциал. Это приведёт к появлению на инверсном выходе триггера нулевого потенциала. Теперь, даже если снять нулевой потенциал с входа S, на выходе триггера останется единичный потенциал. То есть мы записали в триггер логическую единицу.

Точно так же можно записать в RS-триггер и логический ноль. Для этого следует воспользоваться входом R. Так как активный уровень на входах оказался нулевым, то эти входы — инверсные. Составим таблицу истинности RS триггера. Входы R и S в этой таблице будем использовать прямые, то есть и запись нуля, и запись единицы будут осуществляться единичными потенциалами (таблица 1).

Таблица 1. Таблица истинности RS триггера.

| R | S | Q(t) | Q(t+1) | Пояснения |

| | | | | Режим хранения информации R=S=0 |

| | | | |

| | | | | Режим установки единицы S=1 |

| | | | |

| | | | | Режим записи нуля R=1 |

| | | | |

| | | | * | R=S=1 запрещенная комбинация |

| | | | * |

RS триггер можно построить и на логических элементах "ИЛИ". Его схема приведена на рисунке 2. Принцип работы RS триггера, собранный на логических элементах "ИЛИ" будет точно таким же, как и рассмотренный ранее. Единственное отличие в работе этой схемы по сравнению с предыдущей схемой RS триггера будет заключаться в том, что сброс и установка триггера будет производиться единичными логическими уровнями. Эти особенности связаны с принципами работы инверсной логики, которые рассматривались ранее.

Рисунок 2. Схема простейшего RS триггера на схемах "ИЛИ". Входы R и S прямые (активный уровень '1')

Так как RS триггер при реализации его на логических элементах "И" и "ИЛИ" работает одинаково (его принцип работы от схемы не зависит), то и условно-графическое изображение на принципиальных схемах тоже одинаково. Условно-графическое изображение RS триггера на принципиальных схемах приведено на рисунке 3.

Рисунок 3. Условно-графическое обозначение RS триггера

Синхронный RS триггер

Схема RS триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется "опасные гонки"), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены.

Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Для того чтобы отличать от них рассмотренные ранее варианты (RS триггер и триггер Шмитта) этитриггеры получили название асинхронных.

Формировать синхронизирующие сигналы с различной частотой и скважностью при помощи генераторов и одновибраторов мы уже научились в предыдущих главах. Теперь научимся записывать в триггеры входные логические сигналы только при наличии разрешающего сигнала.

Для этого нам потребуется схема, пропускающая входные сигналы только при наличии синхронизирующего сигнала. Такую схему мы уже использовали при построении схем мультиплексоров и демультиплексоров. Это логический элемент "2И". Триггеры, записывающие сигналы только при наличии синхронизирующего сигнала называются синхронными. Принципиальная схема синхронного RS-триггера приведена на рисунке 4.

Рисунок 4. Схема синхронного RS триггера, построенного на элементах "И-НЕ"

В таблице 2 приведена таблица истинности синхронного RS триггера. Принцип работы RS триггера не изменился, добавилось дополнительное условие: синхронизация момента срабатывания схемы. В этой таблице символ 'x' означает, что значения логических уровней на данном входе не важны. Они не влияют на работу триггера.

Таблица 2. Таблица истинности синхронного RS триггера.

| С | R | S | Q(t) | Q(t+1) | Пояснения |

| | x | x | | | Режим хранения информации |

| | x | x | | |

| | | | | | Режим хранения информации |

| | | | | |

| | | | | | Режим установки единицы S=1 |

| | | | | |

| | | | | | Режим записи нуля R=1 |

| | | | | |

| | | | | * | R=S=1 запрещенная комбинация |

| | | | | * |

Как мы уже показали выше, RS триггеры могут быть реализованы на различных логических элементах. При этом их логика работы не изменяется. В то же самое время триггеры часто выпускаются в виде готовых микросхем (или реализуются внутри БИС в виде готовых модулей), поэтому на принципиальных схемах синхронные RS триггеры обычно изображаются в виде условно-графических обозначений. Условно-графическое обозначение синхронного RS триггера приведено на рисунке 5.

Рисунок 5. Условно-графическое обозначение синхронного RS триггера

| Синякина Г.Е. МММММММММММММММммухамедшиной. |

26. Регистр. Классификация регистров

Регистром называется последовательное или параллельное соединение триггеров. Они обычно строятся на основе D триггеров. При этом для построения регистров могут использоваться как динамические (flip-flop), так и статическиеD-триггеры (защелки — lath).

Параллельные регистры

Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного) слова. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырёхразрядного параллельного регистра приведена на рисунке 1, а его условно-графическое обозначение — на рисунке 2.

Рисунок 1. Схема параллельного регистра

В условно-графическом обозначении возле каждого входа D указывается степень двоичного разряда, который должен быть запомнен в этом разряде. Точно таким же образом обозначаются и выходы регистра. То, что микросхема является регистром, указывается в центральном поле условно-графического обозначения символами RG.

В приведённом на рисунке 2 условно-графическом обозначении параллельного регистра инверсные выходы триггеров не показаны. В промышленно выпускающихся микросхемах параллельных регистров инверсные выходы триггеров часто не выводятся наружу для экономии количества выводов корпуса.

Рисунок 2. Условно-графическое обозначение параллельного регистра

При записи информации в параллельный регистр все биты (двоичные разряды) должны быть записаны одновременно. Поэтому все тактовые входы триггеров, входящих в состав регистра, объединяются параллельно. Для уменьшения входного тока вывода синхронизации C на этом входе в качестве усилителя часто ставится инвертор.

Следует помнить, что назначение разрядов является условным. Если по каким либо причинам (например, с точки зрения разводки печатной платы) удобно изменить нумерацию разрядов, то это можно свободно сделать. При перенумерации входов регистров нужно не забывать, точно таким же образом, изменить номера выходов.

Для реализации параллельного регистра можно использовать как триггеры с статическим, так и с динамическим входом синхронизации. В переводной литературе при использовании для построения параллельного регистра триггеров-защелок этот регистр, в свою очередь, называют регистром-защелкой.

При использовании регистров со статическим входом тактирования следует соблюдать осторожность, так как при единичном потенциале на входе синхронизации C. сигналы с входов регистра будут свободно проходить на его выходы. В таких случаях обычно используется двухтактная синхронизация, подобная рассмотренной в главе, посвященной использованию одновибраторов.

Промышленностью выпускаются четырёхразрядные и восьмиразрядные микросхемы параллельных регистров. Для построения восьмиразрядных микросхем обычно используются регистры со статическим входом синхронизации. В качестве примера можно назвать микросхемы К580ИР22 и 1533ИР33 (иностранный аналог 74ACT573).

При решении практических задач часто требуется разрядность параллельных регистров большая восьми. В таком случае можно увеличивать их разрядность параллельным соединением готовых микросхем. Принципиальная схема параллельного соединения четырёх регистров приведена на рисунке 3.

Рисунок 3. Увеличение разрядности параллельного регистра

В настоящее время параллельные регистры обычно являются частью более сложных цифровых устройств, таких как цифровые фильтры, ОЗУ, синтезаторы частот или схемы прямого цифрового синтеза DDS. Подобные схемы не реализуются на микросхемах средней интеграции, а являются частью больших интегральных микросхем (БИС), таких как микропроцессоры, ASIC или FPGA.

поглощает члены

поглощает члены  ,

,  (в первом и во втором столбцах первой строки поставлены крестики).

(в первом и во втором столбцах первой строки поставлены крестики). и

и  (только ими перекрываются второй и шестой столбцы матрицы). Исключение из сокращенной формы одновременно всех импликант, не входящих в ядро, невозможно, так как исключение одной из импликант может превратить другую уже в нелишний член.

(только ими перекрываются второй и шестой столбцы матрицы). Исключение из сокращенной формы одновременно всех импликант, не входящих в ядро, невозможно, так как исключение одной из импликант может превратить другую уже в нелишний член. .

. (5)

(5)