Процессоры семейства dsp56000

ОБЗОР АРХИТЕКТУРЫ И ШИННОЙ ОРГАНИЗАЦИИ DSP56000

Общая характеристика

Высокая производительность процессоров DSP позволяет использовать их в области коммуникаций, высокоскоростного управления, обработке данных, компьютерных приложениях и аудиоприложениях. Приложения цифровой обработки сигналов эффективны в любой области электроники, поскольку любое приложение для аналоговой электронной схемы может быть разработано с использованием DSP.

Ниже приведены типичные задачи цифровой обработки сигналов, для решения которых успешно используется DSP:

• телекоммуникации (голосовая почта, телеконференции, секретные телефоны);

• коммуникации;

• радиокоммуникации;

• компьютерное оборудование (матричные процессоры, рабочие станции,

графические акселераторы);

• обработка изображений;

• графика;

• инструментарий (спектральный анализ, волновая генерация);

• обработка речи;

• обработка аудиосигналов;

• высокоскоростное управление;

• медицинская электроника;

• цифровое видео;

• радары и сонары (навигация, океанография, поиск);

• сейсмография.

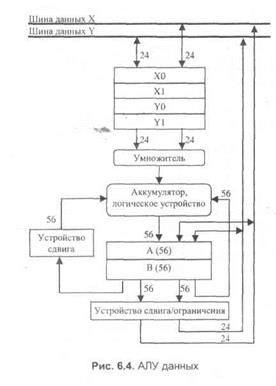

Как было показано ранее, MAC - основная операция, используемая в процессорах DSP. Структура DSP содержит необходимые блоки, обеспечивающие эффективную реализацию операции MAC. Два операнда непосредственно участвуют в операции умножения, и результат суммируется. Этот процесс происходит внутри DSP56000 с использованием двух отдельных модулей памяти за один цикл. Благодаря наличию двух модулей памяти и независимого суммирующего умножителя, можно объединить две пересылки, умножение и сложение в одну операцию.

Основу процессора составляют три параллельно работающих устройства: арифметико-логическое устройство (ALU), устройство генерации адреса (AGU) и программируемый контроллер (PC).

DSP имеет периферийные устройства на кристалле в стиле микроконтроллеров, программируемую цамять, память данных и порты расширения памяти. Программная модель и система инструкций ориентированы на разработку эффективных и компактных программ.

Основные характеристики DSP перечислены ниже:

• Скорость - до 30 и более миллионов операций в секунду.

• Точность -24-разрядные данные, обеспечивающие обработку в динамическом

диапазоне 144 децибел, промежуточные результаты хранятся в 56-разрядном

аккумуляторе, что обеспечивает диапазон в 336 децибел.

• Параллелизм - каждое из операционных устройств на кристалле, память

периферийные операции независимы и работают параллельно благодаря развитой

системе шин.

• Интеграция - в дополнение к трем независимым операционным устройствам DSP

имеет шесть видов памяти на кристалле, три периферийных устройства

(последовательный коммуникационный интерфейс (SCI), синхронный

последовательный интерфейс (SSI), host-интерфейс, генератор тактовой частоты и

семь шин (три адресных и четыре шины данных); при этом система является

компактной и достаточно дешевой, а также обладает низким энергопотреблением.

•Невидимый конвейер - трехступенчатый конвейер инструкций прозрачен для

программиста.

•Система инструкций - 62 инструкции, мнемоники которых совпадают с

инструкциями микроконтроллеров и упрощают трансляцию программ для DSP.

Дополнительные инструкции DSP служат для управления параллельными

операционными устройствами.

• Совместимость программного кода для всех представителей семейства.

• Низкое энергопотребление - за счет использования КМОП-технологии, а также

следующих дополнительных возможностей управления энергопотреблением:

инструкция WAIT; инструкция STOP, останавливающая внутренний генератор

тактовой частоты; уменьшение потребления энергии за счет уменьшения частоты.

Архитектура DSP, как это следует из приведенных выше характеристик, разработана специально для приложений цифровой обработки сигналов.

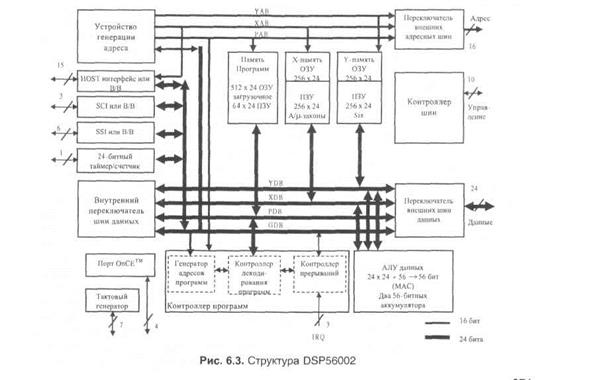

Структура DSP56002, который является базовым для семейства, представлена на рис. 6.3. Модули, входящие в состав других процессоров семейства, рассматриваются в отдельных параграфах настоящей главы.

Основные компоненты DSP:

• шины данных;

• шины адреса;

• арифметико-логическое устройство данных;

• устройство генерации адреса;

• память данных X;

• память данных Y;

• контроллер программ;

• память программ;

• устройства ввода/вывода: расширение памяти (порт А); порты ввода/вывода (В и С);

host-интерфейс; последовательные интерфейсы; таймеры.

Структура шин

Шины данных. DSP организован на регистрах центрального процессора, составляющих три независимых операционных устройства. Передача данных на кристалле осуществляется по четырем двунаправленным 24-разрядным шинам: шине данных X (XDB), шине данных Y (YDB), шине данных программ (PDB), глобальной шине данных (GDB). Шины данных X и Y могут объединяться в 48-разрядную шину для передачи инструкций. Шины XDB и YDB сделаны локальными для увеличения скорости и уменьшения потребления мощности. Все другие передачи данных происходят по шине GDB. Структура шин поддерживает передачу данных типов «регистр - регистр», «регистр - память», «память -регистр». Размер передаваемых данных изменяется от 24- до 56-битных слов в одном командном цикле. Переходы между шинами осуществляются с помощью специального переключателя.

Шины адреса. Адреса внутренней памяти данных X и Y передаются по двум однонаправленным 16-битным шинам - адресной шине X (ХАВ) и адресной шине Y (YAB). Адреса памяти программ передаются по двунаправленной шине адресов программ (РАВ).

Пространство внешней памяти адресуется с помощью однонаправленной 16-битной шины с тремя состояниями выходов, которую можно переключить на ХАВ, YAB или РАВ. В одном командном цикле может быть произведен только один доступ к внешней памяти.

Переход между шинами осуществляется с помощью переключателя внутренних шин. Он представляет собой программируемую матрицу ключей, позволяющую соединять две любые внутренние шины без задержек.

Устройство манипуляций с битами физически расположено в блоке переключателя

|

шин, так как переключатель обеспечивает доступ к любому адресному пространству. Устройство манипуляций с битами выполняет соответствующие операции в памяти, адресных регистрах, регистрах управления и регистрах данных через шины XDB, YDB и GDB.