Пример автоматизированного проектирования

ЦИФРОВОГО УСТРОЙСТВА С ИСПОЛЬЗОВАНИЕМ ЯЗЫКОВ

ОПИСАНИЯ АППАРАТУРЫ

Современные методы и средства проектирования рассмотрим на примере разработки микропроцессорной системы, являющейся модернизацией более ранней разработки устройства на базе микроконтроллера МСS-51 (с целью сокращения объёма примера описание будет упрощено относительно реальных условий). Переход на новую элементную базу в данном проекте прежде всего ограничивается естественным желанием проектировщика максимальным образом использовать ранее разработанные и проверенные решения, в основном это касается фрагментов программного обеспечения. В состав системы должен входить двухканальный 10-разрядный аналого-цифровой преобразователь, записывающий по запросу параллельный код в буферное ОЗУ емкостью 256 десятиразрядных слов, 8 входов и 28 выходов для дискретных сигналов. Использование схем класса СИС и МИС должно быть в модернизированном варианте минимизировано за счет использования схем программируемой логики. для определенности, кроме специально оговоренных случаев, будем ориентироваться на микросхемы программируемой логики фирмы "Altera", а вследствие этого и на САПР этой же фирмы МАХ + PLUSII.

ВАРИАНТЫ РЕАЛИЗАЦИИ И ВЫБОР ЭЛЕМЕНТНОЙ БАЗЫ

Реализация проекта возможна в различных альтернативных вариантах. Сохранение задела по программному обеспечению заставляет обратиться к вариантам, имеющим в качестве МП-ядра тот или иной вариант контроллера МСS-51.

К основным вариантам можно отнести следующие:

1) с использованием БИС класса SОРС geneгiс фирмы "Altera" и мегафункции (на пример, CAST) для реализации МП-ядра;

2) с использованием БИС класса SОРС фирмы "Triscend" семейства ТЕ5, содержащей в качестве МП-ядра встроенный микроконтроллер 8052 и конфигурируемую логику типа FPGA;

3) с использованием микроконтроллера, совместимого по системе команд с МСS-51 со встроенными средствами аналого-цифровой обработки (например, БИС АDuС812 фирмы "Analog Devices" и с реализацией недостающих дискретных элементов в БИС ПЛ фирмы "Altera".

4) с использованием обычного контроллера семейства МСS-51 автономных средств аналого-цифровой обработки и размещением всей дискретной части проекта в БИС ПЛ фирмы "Altera".

Рассмотрим эти варианты более подробно.

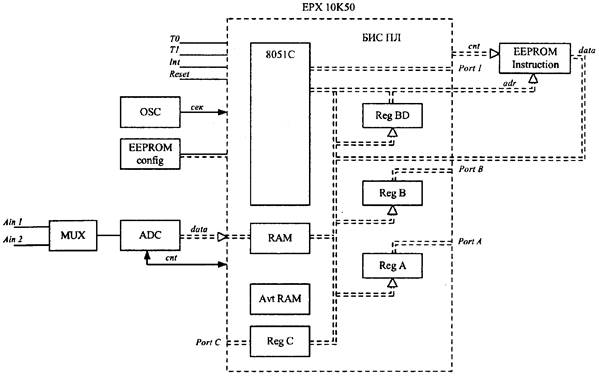

1-й вариант реализации имеет укрупненную функциональную схему, соответствующую приведенной на рис. 8.12. Основу проекта составляет БИС класса SОРС generic, конфигурация которой включает МП-ядро (на базе стандартной мегафункции) и требуемую дополни- тельную логику: регистры выходные (Reg_A, Reg_B, Reg_BD), входной регистр (Reg_С), буферное ОЗУ (RAM) и автомат, управляющий работой ОЗУ (АvtRАМ). Помимо БИС ПЛ схема содержит дополнительные элементы: ИС время задающего генератора (OSC), ИС ПЗУ конфигурации (EEPROM Config), ИС ПЗУ команд (EEPROM Instuction), ИС аналогового коммутатора (MUX) и ИС АЦ преобразователя (ADC). Поскольку мегафункция микроконтроллера в этом варианте реализации требует (в зависимости от скоростных требований) от 2400 до 2860 логических ячеек, то проект потребует для своей реализации БИС ПЛ класса не ниже 10К50. Стоимость таких БИС превышает 80 дол. США, поэтому вариант вряд ли экономически оправдан даже для выпуска ОПЫТНОЙ партии устройств.

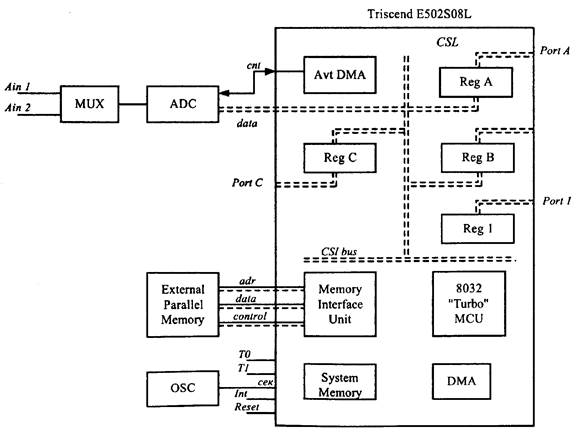

2-й вариант (рис. 8.13), опирающийся на продукцию фирмы "Triscend", потребует для своей реализации помимо БИС семейства ТЕ5 четырех схем СИС (Организация БИС семейства ТЕ5 позволяет объединить в одной БИС ПЗУ Память команд МК и память конфигурации БИС ПЛ — EEPROM). В силу специфики организации БИС семейства ТЕ5 буферизацию данных от АЦ-преобразователя необходимо ВЫПОЛНЯТЬ непосредственно в памяти данных МК и ориентироваться при этом на встроенный контроллер прямого доступа к памяти. Эта специфика приводит к необходимости модернизации Программного обеспечения процессорного ядра. Блоки, реализуемые конфигурируемой системной ЛОГИКИ (С31.) кристалла ТЕ5, функционально совпадают с блоками, размещенными в ВИС ПЛ предыдущего варианта. С экономической точки зрения, основные затраты, по-видимому, будут касаться не столько стоимости кристаллов (стоимость БИС семейства в зависимости от тактовой частоты и числа конфигурируемых ячеек системной логики может колебаться от 18 до 100 дол. США), сколько стоимости покупки лицензии на САПР и загрузочного оборудования, которое может достигать суммы порядка 650 дол. США (минимальные затраты около 170 дол. США).

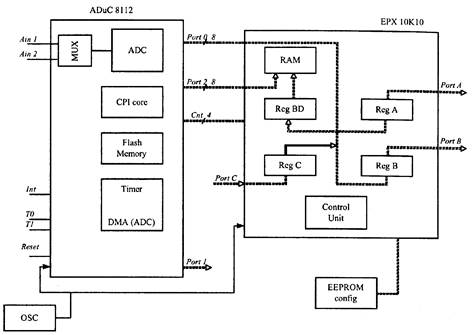

3-й вариант реализации (рис. 8.14) является самым экономичным по числу требуемых для реализации числа микросхем. Основу схемы образуют две БИС (БИС АduC812 фирмы "Analog Devices"и БИС ПЛ ЕРХ10K10 фирмы "Altera". БИС АduC812 фирмы "Anolog Devices" разработчики отнесли к классу микропреобразователей, поскольку БИС содержит на одном кристалле микроконтроллер, память, АЦП и ЦАП. Для реализации устройства дополнительно потребуется одна БИС конфигурационного ПЗУ (EPROM) и одна ИС времязадающего генератора (ОSС). Структура устройства, конфигурируемого в БИС ПЛ, сохраняет элементы предыдущих вариантов. Как и для предыдущего варианта реализации, использование прямого доступа к памяти потребует модернизации программного обеспечения МК. Стоимость БИС AduC812 фирмы"Anolog Devices" не превышает 12 дол.

США, но и стоимость БИС ЕРХ10K10 фирмы "Altera" близка к 20 дол. США. Приобретение средств, сопровождающих разработку, может потребовать затрат, не превышающих 100 дол. США. Вариант имеет предопределенные характеристики по скорости работы АЦП и экономически проигрывает следующему варианту.

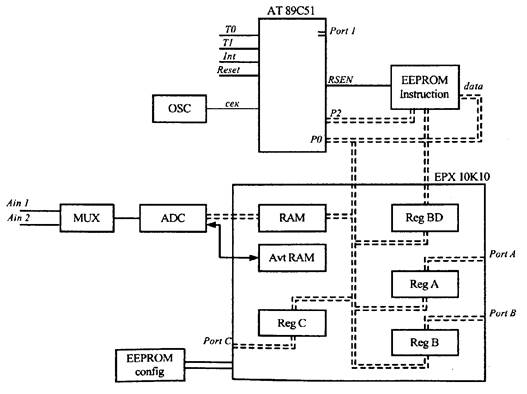

4-й вариант реализации (рис. 8.15) предполагает использование в качестве МП-ядра классической микросхемы МCS-51 (в примере БИС АТ89С51 фирмы "Atmel" и применения БИС ПЛ ЕРХ10K10 для реализации недостающих дискретных компонентов. Основным достоинством варианта является возможность без каких-либо переделок использовать старое программное обеспечение. Именно это и позволяет остановиться для дальнейшей работы на этом варианте. Выбор для реализации 2-го или 3-го вариантов целесообразен только в том случае, если разработчик готов потратить время и деньги на модернизацию программного обеспечения. В связи с наличием целого ряда особенностей при проектировании устройства на базе БИС класса SОРС после подробного рассмотрения процедуры проектирования для выбранного варианта реализации приведем наиболее существенные отличия в проектной последовательности для реализации проекта на базе БИС фирмы "Triscend".

После выбора варианта реализации устройства в целом можно переходить к детализации технического задания на проектирование БИС ПЛ.

Рис. 8.12. Вариант реализации проекта на БИС ПЛ класса SОРС generic

Рис.8.13. Вариант реализации проекта на БИС ПЛ класса SОРС ТЕ5

Рис.8.14. Вариант реализации проекта на БИС АDuC812 и БИС ПЛ ЕРХ10K10

Рис.8.15. Вариант реализаци. и проекта на БИС АТ89С51 и БИС ПЛ ЕРX10K10

ПРОЕКТИРОВАНИЕ БИС ПЛ

Этап 1. Формирование требований на проектирование БИС ПЛ

К основным требованиям следует отнести:

• объем буферного ОЗУ 256 десятиразрядных слов;

• запись в ОЗУ осуществляется блоками (с чередованием данных от различных каналов) по запускающему сигналу RequstADC ,формируемому внешней средой;

• после завершении записи блока оцифрованных данных во внутренний буфер ПЛ информирует МК об этом, выставляя сигнал ReadyData;

• сигнал ReadyData является источником прерывания для МК;

• чтение данных из буферного ОЗУ ПЛ осуществляется по инициативе МК путем последовательного считывания сначала восьми, а затем двух битов данных;

• помимо работы с буферным ОЗУ БИС ПЛ должно поддерживать формирование адреса для внешнего ПЗУ команд МК (Reg_C);

• БИС ПЛ реализует функции двух выходных 8-разрядных портов (Reg_A и Reg_B) и одного входного 8-разрядного порта (Reg_C);

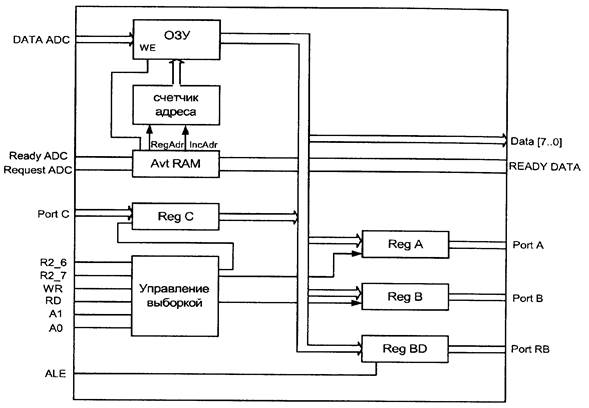

Перечисленные выше пункты ТЗ предопределяют основные блоки проектируемой БИС и их взаимодействие. Блочная схема устройства приведена на рис. 8.16. Функциональное назначение блоков следует из их названий. Схема укрупненно отображает следующие процессы:

запись данных от МК (Data[7..0] по сигналу ALE в регистр адреса ПЗУ команд;

запись данных от МК по сигналу WR (при установленных в "1" 6-го и 7-го разрядов порта Р2 МК) в зависимости от адреса А0 А1 в порт РА или РВ;

чтение данных в МК по сигналу RD (при установленных в "1" 6-го и 7-го разрядов порта Р2 МК) при адресе не А0 и А1 из порта РС;

запись блока данных от аналого-цифрового преобразователя в буферное ОЗУ; считывание данных из буферного ОЗУ в МК;

готовность ПЛ к передаче данных индицируется сигналом ReadyData.

Этап 2. Разработка общей структуры операционного блока

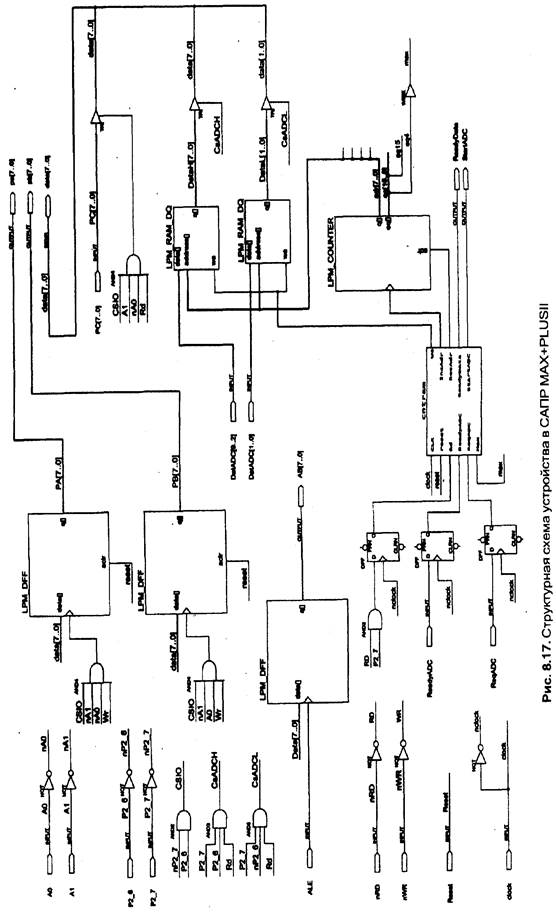

Нетрудно видеть, что для реализации рассматриваемого устройства из состава библиотеки выбранной САПР можно использовать следующий набор библиотечных параметризируемых модулей (LРМ):

• два блока ОЗУ (LРМ_RAM_DQ) с организацией 25б х 8 и 256 х 2;

• 8-разрядный счетчик адреса ОЗУ (LРМ_COUNTER);

• три модуля триггеров типа D (LРМ_DFF), организованных в 8-разрядные регистры.

Понятие параметризированных модулей соответствует возможности настроить выбранный библиотечный элемент на определенный режим функционирования, на определенную разрядность данных, их полярность и т. д. В качестве 8-разрядных регистров можно использовать и специально разработанные блоки на базе примеров, описанных выше.

Структурная схема устройства, включающая эти операционные блоки и автомат, управляющий считыванием и записью кода из ОЗУ, может приобрести вид, приведенный на рис. 8.17. Кроме указанных выше базовых блоков в схеме присутствует ряд дополнительных элементов. Условные обозначения всех элементов схемы соответствуют стандарту, принятому в САПР МАХ + РLUS II. Необходимость введения дополнительных элементов (инверторов, D-триггеров и схем И) диктуется требованиями временной или аппаратной совместимости отдельных блоков схемы. Более подробные пояснения будут приведены в следующем разделе, поскольку этапы разработки операционной части и устройства управления операционными элементами тесно связаны и обычно выполняются итерационно.

Рис. 8.16. Блок-схема устройства, принятого в качестве примера для проектирования средствами САПР

Этап 3. Описание работы управляющего автомата

При разработке поведения управляющего автомата необходимо учесть, что функционирование устройства определяется сигналом СLОСК и происходит асинхронно относительно внешнего устройства, управляющего чтением и записью в ОЗУ и относительно другого внешнего устройства, запрашивающего и принимающего информацию в последовательной форме.

При выборе из библиотеки САПР в качестве ОЗУ-модулей типа LPM_RAM_DQ (т. е. с раздельными шинами чтения и записи данных) и при его настройке на асинхронный режим работы исчезает целый ряд проблем. Во-первых, нет необходимости введения элементов, разделяющих данные для записи и считывания. Во-вторых, существенно упрощается организация синхронизации работы управляющего автомата при записи данных в ОЗУ с асинхронно работающим АЦП.

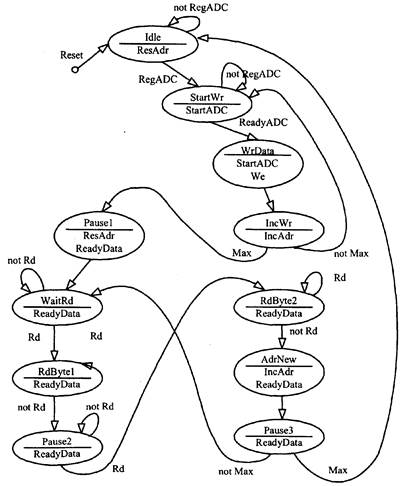

Возможный алгоритм работы устройства управления разрабатываемого устройства, отвечающий сформулированным выше требованиям, может приобрести вид соответствующий граф-схеме переходов автомата, приведенной на рис. 8.18. Граф-схема переходов при помощи графического редактора программы StateCAD Version 3.2 пакета Workview Office фирмы "Viewlogic" была занесена в соответствующий диаграммный файл, что, как будет показано далее, существенно упрощает не только отладку и возможные корректировки алгоритма, но и создание соответствующих программных текстов.

Перейдем к анализу автомата CntRAM управляющего записью и считыванием данных в буферное ОЗУ и поддерживающего для этих обменов требуемое взаимодействие квитирующими сигналами.

Основу алгоритма составляют два последовательно выполняемых блока.

Первый блок по сигналу запроса на преобразование ReqADC от внешнего устройства обеспечивает циклическое выполнение следующей последовательности действий. В со стоянии автомата (StartWr) выставляется сигнал запуска преобразователя (StartADC), дождавшись сигнала готовности данных от АЦП (ReadyADC), считывает 10 бит данных и записывает их (в состоянии WrData) в память (формируя сигнал WE).Об окончании приема данных АЦП узнает благодаря сбросу запроса на преобразование, затем автомат наращивает адрес ОЗУ (формируя в состоянии IncWr сигнал IncAdr). Признаком завершения приема блока данных является сигнал Мах, формируемый на основании анализа состояния счетчика адреса ОЗУ.

По завершении записи блока данных автомат в состоянии Pause1 выставляет сигнал заполнении ОЗУ данными ReadyData и сбрасывает счетчик адреса ОЗУ (сигнал ResAdr),

подготавливая его тем самым к циклу считывания данных в МК. Этот цикл и составляет основу второго блока выполняемых автоматом действий. Поскольку формирование сигналов открытия выходных буферов CsADCH и CsADCL выполняется внешними относительно автомата цепями, основной задачей блока является выполнение последовательности действий, которая, обнаружив два последовательно выставленных внешних сигнала автомата Rd, формирует сигнал IncAdr, обеспечивающий переход к следующему адресу. Число требуемых итераций цикла, как и в первом блоке, подсчитывает счетчик адреса. Следует обратить внимание на петли ожидания в состояниях WaitRd, RdByte1, Pause2, RdByte2 наличие которых обеспечивает требуемую синхронизацию.

Для правильной работы автомата асинхронные сигналы ReqADC, ReadyADC и Rd требуют их предварительного запоминания в дополнительно введенных в схему D-триггерах. Тактирование D-триггеров сигналами nClock т. е. задним фронтом сигнала (при условии, что автомат тактируется передним фронтом сигнала Clock),гарантирует четкую работу автомата. Для устранения паразитных врезок у выходного сигнала автомата ReadyData (которые могут вызывать ошибочные действия системы прерываний микроконтроллера) также используется D-триггер, тактируемый сигналом nClock.

Дадим некоторые пояснения к синтаксису VHDL-программы устройства управления.

Для автомата приведенного примера с помощью программы StateCAD Version 3.2 пакета Workview Office была выполнена трансляция диаграммы (для разных вариантов языкового описания). Был создан вариант, ориентированный на возможности языка описания аппаратуры на языке высокого уровня VHDL (листинг 1).

Рис. 8.18. Граф-схема переходов автомата управления

При компиляции из графической формы в текстовую программа StateCAD учитывает, для компилятора какой фирмы предполагается использовать описание автомата (соответствующим образом выбирая используемые синтаксические конструкции). Аналогичные соображения должны приниматься во внимание и при ручном написании программ. Это ограничение возникает из-за того, что набор допустимых синтаксических конструкции языка для различных фирм существенно отличается от стандартного. Для примера выбрана ориентация на САПР Synopsys (как имеющую меньшие ограничения).

Листинг 1

— VHDL code created by Visual Solution's StateCAD Version 3.2

—This VHDL code (for use with Synopsys) was generated using:-enumerated state assignment with structured code format.

— Minimization is enabled,implied else is enabled,

—and outputs are manually optimized.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY synopsys;

USE synopsys.attributes.all;

ENTITY CntRAM IS

РОRТ (CLK,Max,Rd,ReadyADC,Reset:IN std_logic;

IncAdr,ReadyData.ResAdr,StartADC,We:OUT std_logic);

END;

ARCHITECTURE BEHAVIOR OF CntRAM IS

ТYРЕ type_sreg IS(AdrNew,EndLoop,Idle,IncWr,Pause1, Pause2, Pause3,RdByte1,

RdByte2,StartWr,WaitWr,WrData);

SIGNAL sreg,next_sreg:type_sreg;

BEGIN

PROCESS (CLK)

BEGIN

IF CLK='1' AND CLK'event THEN

IF (Reset='1') THEN

sreg<=idle;

ELSE

sreg<=next_sreg;

END IF;

END IF;

END PROCESS;

PROCESS(sreg,Max,Rd,ReadyADC,ReqADC,Reset)

BEGIN

IncAdr<="0";ReadyData<="0";ResAdr<="0";

StartAdc<="0";We<="0";

next_sreg<=AdrNew;

IF(Reset='1') THEN

next_sreg<=Idle;

IncAdr<='0';ReadyData<='0';StartADC<='0';

We<='0';ResAdr<='1';

ELSE

CASE sreg IS

WHEN AdrNew=>

ResAdr<='0';StartADC<='0';

We<='0';

IncAdr<='1';ReadyData<='1';

next_sreg<=Pause3;

WHEN Idle=>

IncAdr<='0';ReadyData<='0';

StartADC<='0';

We<='0';ResAdr<='1';

IF (ReqADC='1') THEN

next_sreg<=StartWr;

END IF;

WHEN IncWr=>

ReadyData<='0';ResAdr<='0';

StartADC<='0';

We<='0';IncAdr<='0';

IF (Max='0') THEN

next_sreg<=StartWr;

END IF;

IF (Max='1') THEN

next_sreg<=Pause1;

END IF;

WHEN Pause1=>

IncAdr<='0';StartADC<='0';

We<='0';

ResAdr<='1';ReadyData<='1';

next_sreg<=WaitRd;

WHEN Pause2=>

IncAdr<='0';ResAdr<='0';

StartADC<='0';

We<='0';ReadyData<='1';

IF (Rd='0') THEN

next_sreg<=Pause2;

END IF;

F(RD='1') THEN

next_sreg<=RdByte2;

END IF;

WHEN Pause3=>

IncAdr<='0';ResAdr<='0';

StartADC<='0';

We<='0';ReadyData<='1';

IF (Max='1') THEN

next_sreg<=Idle;

END IF;

IF (Max='0') THEN

next_sreg<=WaitRd;

END IF;

WHEN RdByte1=>

IncAdr<='0';ResAdr<='0';

StartADC<='0';

We<='0';ReadyData<='1';

IF (Rd='0') THEN

next_sreg<=Pause2;

END IF;

IF (Rd='1') THEN

next_sreg<=RdByte1;

END IF;

WHEN RdByte2=>

IncAdr<='0';ResAdr<='0';

StartADC<='0';

We<='0';ReadyData<='1';

IF (Rd='0') THEN

next_sreg<=AdrNew;

END IF;

IF (Rd='1') THEN

next_sreg<=RdByte2;

END IF;

WHEN StartWr=>

IncAdr<='0';ResAdr<='0';

StartADC<='1';

We<='0';ReadyData<='0';

IF (ReadyADC='1') THEN

next_sreg<=WrData;

END IF;

IF (ReadyADC='0') THEN

next_sreg<=StartWr;

END IF;

WHEN WaitRd=>

IncAdr<='0';ResAdr<='0';

StartADC<='0';

We<='0';ReadyData<='1';

IF (Rd='1') THEN

next_sreg<=RdByte1;

END IF;

IF (Rd='0') THEN

next_sreg<=WaitRd;

END IF;

WHEN WrData=>

IncAdr<='0';ResAdr<='0';

StartADC<='0';

We<='1';ReadyData<='0';

next_sreg<=IncWr;

WHEN OTHERS=>

END CASE;

END IF;

END PROCESS;

END BEHAVIOR;

Разделы проектного модуля типичны для языка VHDL. В самом начале перечисляются используемые в проекте библиотеки (IEEE и Synopsys). В заголовочном разделе ENТIТY перечислены имена и типы всех сигналов: входных внешних управляющих сигналов — тактового сигнала (CLK), сигнала окончания блока данных (Мах), запросов на чтение и запись блока данных (Rd и ReqADC) соответственно, флага готовности АЦП (ReadyADC) и, наконец, начального сброса(Reset) и выходных управляющих сигналов сигнала запуска АЦП (StartADC),сигналов управления счетчиком адреса (IncAdr,ResAdr), сигнала управления режимом записи буферного ОЗУ (We) и внешним выходным сигналом (ReadyData).

Следующий раздел —ARCHITECTURA — представляет собой описание архитектуры или поведения (в нашем случае поведения) блока, интерфейс которого был описан в ENTITY.

Как и в обычных языках, в начале раздела дается описание типов и объявление переменных, используемых при описании действий, выполняемых в разделе ARCHITECTURA.

В данном автомате определен перечислительный тип данных type_sreg со всем списком допустимых значений (они, естественно, совпадают с именами, введенными в граф схеме переходов). Далее в тексте объявлены два сигнала — sreg и next_sreg введенного типа tуре_sreg . Введение двух сигналов связано с необходимостью определения текущего и следующего состояний автомата при переходе от одного состояния к другому.

Главная часть архитектурного тела содержит два оператора параллельного типа (процесса). Первый процесс запускается на исполнение каждый раз, когда происходит изменение сигнала CLK. Однако его основное действие назначение автомату нового состояния — происходит только по переднему фронту сигнала CLK. Использование для тактирования автомата переднего фронта синхронизирующего сигнала (предложение IF CLK='1' AND CLK'event THEN sreg<=next_sreg;END IF;) служит для синхронизации выбранных библиотечных операционных узлов и обеспечит стабильность входных управляющих сигналов в моменты тактирования. При составлении программы автомата учитывалась необходимость его установки в исходное состояние при подаче сигнала сброса (выражение IF(Reset='1') THEN sreg<=Idle;).

Поведение управляющего автомата в тексте программы задано вторым процессом.

Второй процесс запускается каждый раз, когда изменяется состояние автомата (sreg) или изменяется какой-либо входной сигнал. Содержимое этого процесса и определяет поведение управляющего автомата. Конечные автоматы в языке VHDL удобно описывать посредством оператора выбора "CASE", используя в качестве ключа выбора варианта переменную состояния автомата в текущий момент времени. Внутри каждого варианта определяется состояние перехода и значения выходных сигналов, формируемых в соответствии с входными условиями. Состояние перехода из текущего состояния в следующее осуществляется с помощью оператора назначения переменной next_sreg нового значения. В тех случаях, когда переход из текущего состояния зависит от внешних сигналов, этот оператор назначения входит в состав условного оператора, логическое выражение которого совпадает с последовательностью условий, встречающихся на соответствующих путях переходов на схеме алгоритма. Аналогично определяются и выходные сигналы, вырабатываемые на переходах и задающие исполняемые в других блоках операции.

Этап 4. Компиляция проекта и основные параметры устройства

После создания всех фрагментов проекта и схемы проекта в целом выполняется его компиляция. Необходимость иметь буферное ОЗУ и требуемый объем ОЗУ (реализация ОЗУ в форме совокупности отдельных D-триггеров потребовала бы значительных логических затрат) предопределила целесообразность выбора в качестве основы реализации БИС ПЛ семейства FLEX 10K (с организацией памяти конфигурации в форме SRAM). Ориентация памяти конфигурации на память типа 8 заставила ввести в состав устройства специальную БИС ПЗУ, хранящую загружаемую при выключении питания память конфигурации. После успешной компиляции был получен файл отчета (*.грt), показавший, что данный проект далеко не полностью использует возможности, предлагаемые самым младшим представителем семейства 10К БИС EPF10K10TC44. Общие затраты БИС (по числу логических ячеек) на реализацию проекта компилятор определил всего как 17%. Правда, на реализацию модуля ОЗУ компилятор использовал 66% имеющихся у БИС ресурсов. Число задействованных контактов ввода/вывода составляет 62, что не позволило остановиться на предыдущем типоразмере корпуса БИС.

Этап 5. Тестирование проекта

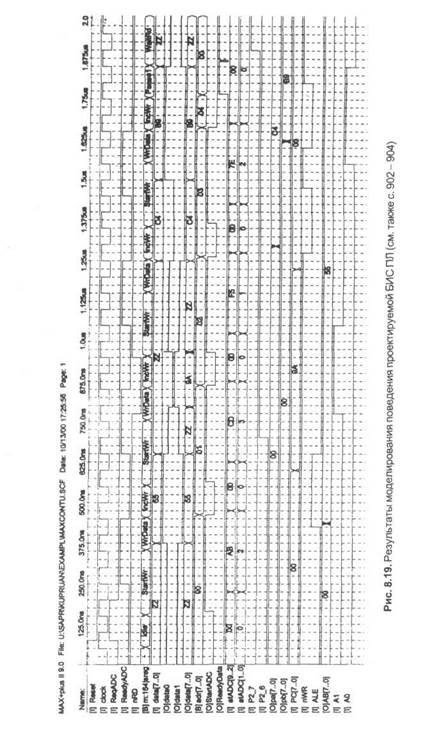

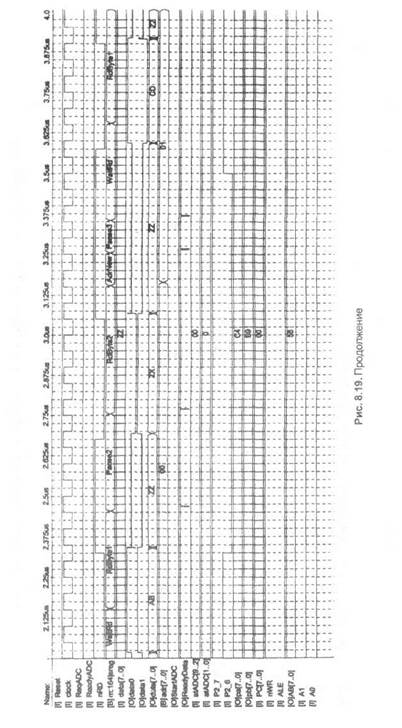

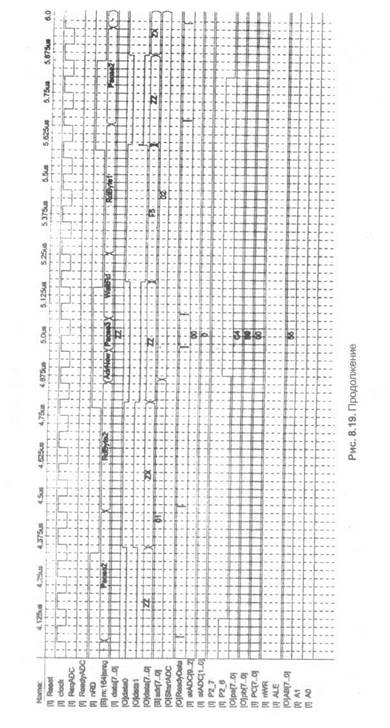

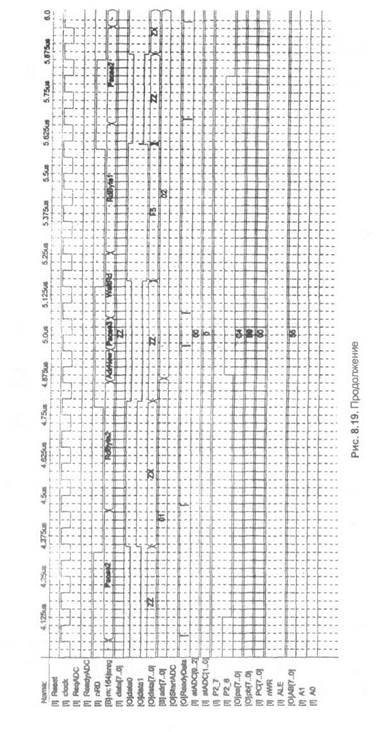

Тестирование проекта также выполнялось средствами САПР МАХ + PLUS||. Созданная тестовая последовательность должна была проверять лишь ключевые моменты работы разработанного устройства. Результаты моделирования приведены на рис. 8.19. дадим пояснения основным фрагментам моделирования.

Системное время — в интервале от 0 до 0,075 мкс. Режим начального сброса устройства. Проверка всех возможных исходных ситуаций перед сбросом весьма громоздка и в данном примере эти варианты из соображений большого объема не включены.

Системное время — в интервале от 0,075 до 0,2 мкс. Моделирование появления внешнего сигнала запроса (ReqADC) на запись в ОЗУ блока данных от АЦП. Для сокращения временной диаграммы моделирование осуществлялось для упрощенной схемы (сигнал Мах формируется после записи всего четырех адресов).

В интервале системного времени от 0,15 до 0,45 мкс в ответ на сигнал запуска цикла аналого-цифрового преобразования (StartADC) АЦП выставил сигнал готовности данных (ReadyADC) , и это служит основой для записи в ОЗУ по адресу 00 данных, равных АВ и 2 (здесь, как и далее, значения всех адресов и данных будут даны в шестнадцатиричной системе счисления).

От значения системного времени 0,45 до значения 1,75 мкс выполняется еще три записи в ОЗУ данных: (CD 3), (F5 1) и (7Е 2) по адресам ОЗУ 1, 2 и 3.

Ввиду аппаратной независимости записи в ОЗУ и работы периферии МК одновременно с моделированием записи блока данных в ОЗУ осуществлялось моделирование:

• фиксации в момент системного времени 0,45 мкс старшей части адреса внешнего ПЗУ — по сигналу АLЕ фиксировалось на выходе 8-разрядного регистра АВ значение 55, выставленное на шине данных МК;

• фиксации в момент системного времени 1,3 мкс в триггерах порта РА значения С4 (следствие появления сигнала nWRпри условиях Р2_б Р = 1, 2_7 0, А0 =0 и А1 = 0);

• фиксации в момент системного времени 1,625 мкс в триггерах порта РВ значения В9 (следствие появления сигнала nWR при условиях Р2_6 Р = 1, 2_7 = 0, А0 = 1 и А1 = 0).

Когда системное время достигло значения 1,75 мкс, автомат выставил сигнал о готовности данных в буфере (ReadyData) и перешел в режим ожидания блока сигналов считывания из буферного ОЗУ в МК. В ответ на сигналы nRD с соответствующими значениями сигналов Р2_6 и Р2_7 в интервалы системного времени (2,0 2,325), (2,675 3,05), (3,575 3,9), (4,325 4,75), (5,15 5,575), (5,85 6,25), (6,65 6,950) и (7,275 7,675) осуществляется выдача данных, сохраненных в буферном ОЗУ, на шину данных МК.

|

|

|

|

Признаком окончания передачи блока данных служит сброс сигнала ReadyData и переход автомата в состояние Idle (в примере это происходит после 7,95 мкс).

Анализ временных диаграмм позволяет не только проверить правильность функционирования устройства, но и исследовать временное поведение отдельных элементов проекта и прежде все определить и проконтролировать выполнение в реальной системе требуемого времени удержания некоторых сигналов.

Этап 6.Автоматическое определение временных параметров устройства

Возможности САПР вычислять временные соотношения между различными фрагментами проекта существенно облегчает проектировщику задачу проверки правильности работы проекта во временной области. Автоматизация этого этапа проектирования избавляет от необходимости ручного перебора исходных данных проекта с целью обнаружения отклонении от допустимых временных установок.

Этап 7. Практическая проверка результатов проектирования

Основным результатом работы компилятора является файл конфигурации БИС, соответствующий техническому заданию. Средства САПР позволяют на заключительных этапах работы поместить содержимое этого файла в интересующую проектировщика БИС, и на этом процесс проектирования может быть переведен в плоскость натурных экспериментов, для рассматриваемого примера натурные эксперименты производились с использованием специального отладочного стенда, содержащего две БИС ПЛ типа 10К10. Одна БИС использовалась для загрузки конфигурации проектируемой схемы, а другая —для загрузки конфигурации автомата, создающего тестовые воздействия, совпадающие с тестовыми воздействиями модельного эксперимента. Благодаря соединению контактов БИС между собою возможно наблюдение за работой спроектированной БИС на экране осциллографа в режимах, отличающихся от реальных условий только моделированием этих условий. Эксперименты позволяют убедиться в правильности созданного файла конфигурации (или вернуться на начальные этапы проектирования БИС ПЛ) и перейти к следующему уровню проектирования — проектированию печатной платы, содержащей требуемые элементы проектируемой системы. Поскольку в проектируемой системе для загрузки конфигурации в БИС ПЛ ЕРХ10К10 предполагается использовать специальную загрузочную БИС типа ЕРС, то практическим результатом этого этапа можно считать программирование последовательного загрузочного ПЗУ (например, типа ЕРС1 РС8 фирмы "Altera").