Подготовка к выполнению лабораторной работы

1. Изучить основы алгебры логики. Выписать основные логические функции двух переменных и основные законы алгебры логики.

2. Зарисовать условные графические обозначения изучаемых логических элементов.

3. Составить бланки таблиц состояний исследуемых схем.

4. Ознакомиться с порядком сборки и исследования схем.

Порядок выполнения лабораторной работы

Лабораторная работа выполняется на лабораторном стенде «Электроника» (рис.1.) или на универсальном стенде по основам автоматики и электронно-вычислительной техники (рис. 2).

4.1. Выполнение лабораторной работы на лабораторном стенде «Электроника»

1. Собрать схему в соответствии с рис. 4.1.

Рис. 4.1. Схема для исследования логических элементов

2. Для логических элементов НЕ, И, И-НЕ, схемы которых представлены на рис. 4.1, практически проверить правильность составленных ранее таблиц истинности и временных диаграмм. Для подачи на вход логического элемента уровня логической "1" необходимо подключить соответствующий вход через сопротивления R76, R79, R72 либо R73 к источнику питания "+5В". Для подачи на вход ЛЭ уровня логического "0" необходимо этот вход подключить к общему проводу. Выходной сигнал логического элемента регистрируется осциллографом.

3. Подав на один из входов логического элемента И, а затем на И-НЕ, прямоугольные импульсы от генератора ГС2 зарисовать осциллограммы на выходе при уровне на втором входе "0" и "1".

4. По результатам исследования составить таблицу истинности для каждого устройства.

5.Пояснить полученные осциллограммы.

Выполнение лабораторной работы на универсальном стенде по основам автоматики и электронно-вычислительной техники

1. Установить на стенд плату П1, на которой размещены 3 микросхемы. Каждая из микросхем содержит в своем составе по 4 двухвходовых логических элемента.

2. В ходе лабораторной работы исследуются устройства, изображенные на картах 1.1 - 1.9. Для каждой карты исследовать работу изучаемых логических устройств. Для этого:

3. Задать возможные комбинации входных сигналов с помощью тумблеров SA1 – SA5;

4. Составить таблицы истинности исследуемых устройств;

5. Определить логическую функцию, описывающую работу каждого логического устройства, и записать ее через операции И, ИЛИ и НЕ;

6. Определить тип каждого логического элемента, входящего в исследуемое устройство.

Контрольные вопросы.

1. Перечислить все имеющиеся в микропроцессорной технике основные логические элементы.

2. Изобразить условные обозначения основных логических элементов и их таблицы истинности.

3. Показать, как правильно осуществлять наборы значений аргументов в логических функциях 3-х, 4-х, и 5-ти аргументов.

4. Объяснить правила составления СДНФ и СКНФ по имеющимся таблицам истинности.

5. Перечислить основные законы алгебры логики.

6. Привести примеры устройств, выполняющих логические функции ИЛИ, И, ИСКЛЮЧАЮЩЕЕ ИЛИ в области электротехники.

7. Пользуясь законами алгебры логики, преобразовать заданную функцию в более простой вид: а)

б)

в)

8. Составить таблицы истинности для функций, указанных в п.7.

9. По заданным логическим функциям составить схему из основных логических элементов, реализующую уравнения:

10. Используя элементы Шеффера, составить схемы, реализующие логические операции И, ИЛИ, НЕ.

11. Назвать основные параметры логических элементов.

12. Изобразить схему логического элемента ИЛИ на диодах и пояснить ее работу.

13. Изобразить схему логического элемента И на диодах и пояснить ее работу.

14. Пояснить минимизацию функции с помощью метода карт Карно.

Лабораторная работа № 5

Исследование триггеров

Цель работы

Изучить и исследовать свойства RS, D и T триггеров.

Основные положения

Триггером называется устройство, состоящее из цепей управления и элемента памяти, обладающее двумя состояниями устойчивого равновесия, скачкообразно переходящего из одного состояния в другое.

Элемент памяти триггера состоит из двух половин – плеч, в которых одновременно удерживается два запоминающих сигнала: один высокого потенциала (условно принимаемого за «1»), другой низкого потенциала (условно принимаемого за «0»).

Триггеры нашли широкое распространение в вычислительной технике и составляют от 20 до 40% всего оборудования.

По функциональному назначению триггеры подразделяют на триггеры с раздельным запуском (RS-триггеры, JK-триггеры), со счетным запуском (Т-триггеры) и с элементами задержки (D-триггеры).

По способу записи информации триггеры подразделяют на асинхронные и тактирующие. В асинхронных триггерах запись информации осуществляется непосредственно с поступлением входного сигнала, тогда как в тактируемом триггере информация вводится только при наличии тактового импульса.

Условно выходы триггера обозначают буквами  Q и

Q и  , тогда если Q соответствует «1», то

, тогда если Q соответствует «1», то  - нулю и наоборот.

- нулю и наоборот.

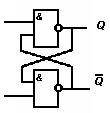

Рис. 5.1. RS-триггер

При установке триггера в состояние «1» на Q выходе запускающий информационный сигнал называют S (сигналом, устанавливающим триггер в состояние «1»), а информационный сигнал, подаваемый на другой вход триггера, называют R (сигналом, устанавливающим триггер в состояние «0»). Состояние на выходе соответствует «1» (Q=1), если S=1, а R=0, и соответствует «0» (Q=0) при S=0 и R=1. При состояниях на обоих входах, соответствующих «0», состояние на выходе триггера не изменится, а при состояниях на обоих входах, соответствующих «1», триггера принимает неопределенное состояние.

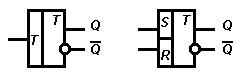

Условные обозначения триггеров имеют вид:

|

Т – триггер RS – триггер

Рис. 5.2. Триггеры

Наряду с данными триггерами широкое применение находят D и JK–триггеры.

D–триггер часто называют «триггером задержки». Он имеет один информационный вход D и обязательно синхронизируется тактовыми импульсами. Триггер повторяет информационный сигнал только тогда, когда присутствует тактовый импульс «С» независимо от предыдущего состояния.

JK-триггер аналогичен RS-триггеру. Он имеет два информационных входа. Роль входов S и R играют соответственно входы J и K. Отличие JK-триггера от RS-триггера заключается в том, что при наличии «1» на обоих входах его состояние переходит из предыдущего в последующее, т.е. если он находился в состоянии «0», то перейдет в состояние «1» и наоборот.

JK-триггер считается универсальным, на его базе путем ввода обратных связей можно получить любой из перечисленных выше триггеров.

Триггеры могут быть выполнены на логических элементах И-НЕ и ИЛИ-НЕ. Структурные схемы таких триггеров изображены на исследуемых картах лабораторной установки. Кроме того, любой из триггеров может быть выполнен на интегральной микросхеме (ИМС).