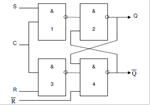

Нарисуйте схему синхронизируемого однотактного RS-триггера и его таблицу переходов

Таблица переходов для синхронизируемых входов R и S.

| R | s | Q | Примечание |

| Q | Хранение информации | ||

| Установка 1 | |||

| Установка 0 | |||

| - | Запрещено |

Функциональная схема синхронизируемого однотактного RS-триггера

| 13. | ||

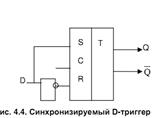

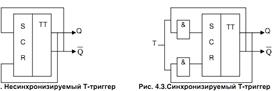

| Основные параметры системной платы. Системная (материнская) плата является важнейшим устройством персонального компьютера, выступая интегратором для других компонентов. Совместно с процессором и оперативной памятью она образует платформу, определяющую основные функциональные возможности компьютера и его производительность. Ключевой элемент системной платы — набор микросхем системной логики (НМСЛ). Он обеспечивает взаимодействие других компонентов и функционирование базовых интерфейсов. Такой набор часто называют чипсетом.Помимо НМСЛ системная плата содержит базовую систему ввода-вывода (BIOS), элементы питания компонентов, монтажные детали. Основными параметрами системной платы являются: форм-фактор (типоразмер) - Форм-фактор, или типоразмер системной платы, определяет ее габариты, параметры электропитания, расположение монтажных элементов, размещение различных компонентов.. применяемый чипсет ЧИПСЕТ — транскрипция англоязычного термина (Chip Set), обозначающего комплект микросхем системной логики, обслуживающий интерфейсы материнской платы.- Чипсет традиционной архитектуры состоит из двух микросхем, которые называют южным и северным мостами. Северный мост по своей сути является связующим мостом и контролирует потоки данных различных шин. К нему подключены ключевые интерфейсы компьютера: системная шина, шина памяти, шина графического контроллера (видеокарты), шина для сопряжения с южным мостом. Южный мост отвечает за периферийные устройства и различные внешние шины. Так, к нему подключены: шины расширения, порты USB, IDE-контроллер, дополнительные IDE, SATA-или FireWire-контроллеры | поддерживаемый интерфейс процессора - Обычно набор системной логики создается конструкторами с ориентацией на конкретное семейство процессоров. То есть обеспечивается поддержка определенного процессорного интерфейса. В это понятие включают тип разъема и системной шины, электрические параметры (разводка контактов, напряжение питания ядра и блоков ввода-вывода процессора), возможности BIOS по поддержке конкретных моделей процессоров. тип устанавливаемой оперативной памяти - Возможность установки на системной плате того или иного типа оперативной памяти определяется типом контроллера памяти. Такой контроллер интегрирован либо в НМСЛ, либо в процессор. Первый вариант применяется в системных платах для платформы Intel. Интегрированный в процессор контроллер памяти используется в платформах AMD.. поддерживаемые интерфейсы - Важнейшая функция НМСЛ и системной платы в целом — поддержка современных интерфейсов. Обычно базовую функциональность обеспечивает собственно чипсет. Производители системных плат за счет установки дополнительных контроллеров либо расширяют количество типовых портов, либо добавляют поддержку новейших или специфических интерфейсов. тип и возможности BIOS. - Важным элементом системной платы является BIOS (Basic Input/Output System) — базовая система ввода-вывода. Так называют встроенное программное обеспечение, которое доступно для процессора без обращения к накопителям. В микросхеме BIOS содержится программный код, необходимый для управления клавиатурой, видеокартой, дисками, портами и другими компонентами. Обычно BIOS размещается в микросхеме постоянного запоминающего устройства (ПЗУ), расположенной на материнской плате компьютера. Такая технология позволяет обеспечить доступ к BIOS независимо от работоспособности внешних по отношению к материнской плате компонентов (например, загрузочных дисков). Поскольку доступ к оперативной памяти осуществляется значительно быстрее, чем к ПЗУ, многие изготовители предусматривают при включении питания автоматическое копирование ВЮ5 из ПЗУ в оперативную память. | Что такое регистр? Перечислите операции, выполняемые регистром. Что такое операция сдвига кода в регистре? Что при этом происходит с разрядами слова? Регистром называется устройство, предназначенное для запоминания машинного слова, а Регистр представляет собой совокупность триггеров, число которых соответствует числу разрядов в слове, а также вспомогательных схем, обеспечивающих выполнение следующих операций: 1. Установка регистра в 0 или сброс; 2. Прием слова из другого устройства; 3. Передача слова в другой регистр или устройство; 4.  Сдвиг слова вправо или влево на требуемое число разрядов; 5. Преобразование последовательного кода слова в параллельный и наоборот; 6. Поразрядные логические операции. . Операция сдвига кода – перемещение в регистре всех разрядов кода слова на одинаковое число разрядов влево или вправо. В этом случае разряды слова, вышедшие из разрядной сетки регистра теряются, а в освободившиеся разряды регистра записываются нули. Как устроен T-триггер? Каким образом D-триггер реализует функцию временной задержки? Сдвиг слова вправо или влево на требуемое число разрядов; 5. Преобразование последовательного кода слова в параллельный и наоборот; 6. Поразрядные логические операции. . Операция сдвига кода – перемещение в регистре всех разрядов кода слова на одинаковое число разрядов влево или вправо. В этом случае разряды слова, вышедшие из разрядной сетки регистра теряются, а в освободившиеся разряды регистра записываются нули. Как устроен T-триггер? Каким образом D-триггер реализует функцию временной задержки?   Т-триггер может быть построен с использованием двухтактного синхронизируемого RS-триггера. Простейшая схема несинхронизируемого T-триггера (рис. 4.2.) приводит к записи в двухступенчатый RS-триггер состояния, противоположного ранее хранимому. При этом, так как триггер двухступенчатый, на его выходе сигнал изменится только по завершении действия сигнала t=1. Это исключает возникновение генерации в схеме с обратной связью. В данной схеме единичный входной сигнал представляется спадом сигнала t=1 и при любой продолжительности сигнала t=1 изменение состояния T-триггера происходит только один раз при снятии сигнала. При необходимости представлять потенциалом последовательность единиц на входе T-триггера используется вторая схема двухтактного синхронизируемого RS-триггера (рис.4.3.). Единичный входной сигнал в этой схеме представляется высоким уровнем сигнала t при наличии сигнала синхронизации C=1. Высоким уровнем сигнала t можно представить последовательность единиц. Причем смена состояния такого триггера происходит после окончания действия сигнала синхронизации при t=1. Состояние триггера изменяется на противоположное при t=0 состояние триггера не меняется. D-триггер является интегральной схемой, которая реализует функцию временной задержки. D-триггер имеет только режимы установки 1 и 0, и в этой связи несинхронизируемый D-триггер реализует функцию повтора входного сигнала. Синхронизируемый D-триггер задерживает распространение входного сигнала на время паузы между синхросигналами т.е. осуществляется задержка на пол периода. Для задержки на полный период используются схемы двухтактных D-триггеров. D-триггер вносит запаздывание Q(t+1)=D(t) Т-триггер может быть построен с использованием двухтактного синхронизируемого RS-триггера. Простейшая схема несинхронизируемого T-триггера (рис. 4.2.) приводит к записи в двухступенчатый RS-триггер состояния, противоположного ранее хранимому. При этом, так как триггер двухступенчатый, на его выходе сигнал изменится только по завершении действия сигнала t=1. Это исключает возникновение генерации в схеме с обратной связью. В данной схеме единичный входной сигнал представляется спадом сигнала t=1 и при любой продолжительности сигнала t=1 изменение состояния T-триггера происходит только один раз при снятии сигнала. При необходимости представлять потенциалом последовательность единиц на входе T-триггера используется вторая схема двухтактного синхронизируемого RS-триггера (рис.4.3.). Единичный входной сигнал в этой схеме представляется высоким уровнем сигнала t при наличии сигнала синхронизации C=1. Высоким уровнем сигнала t можно представить последовательность единиц. Причем смена состояния такого триггера происходит после окончания действия сигнала синхронизации при t=1. Состояние триггера изменяется на противоположное при t=0 состояние триггера не меняется. D-триггер является интегральной схемой, которая реализует функцию временной задержки. D-триггер имеет только режимы установки 1 и 0, и в этой связи несинхронизируемый D-триггер реализует функцию повтора входного сигнала. Синхронизируемый D-триггер задерживает распространение входного сигнала на время паузы между синхросигналами т.е. осуществляется задержка на пол периода. Для задержки на полный период используются схемы двухтактных D-триггеров. D-триггер вносит запаздывание Q(t+1)=D(t) |

14. Что такое дешифратор? Напишите значения булевых функции, вырабатываемых на выходах дешифраторов с номерами от 0 до 2n-1Для чего используются дешифраторы?Что такое дешифратор? Рис. 5.3.Условноеобозначениедешифратора Дешифратор – комбинационная схема с несколькими входами и выходами, преобразующая код, подаваемый на входы в сигнал на одном из выходов. Напишите значения булевых функции, вырабатываемых на выходах дешифраторов с номерами от 0 до 2n-1  Если на входы дешифратора подаются двоичные переменные, то на одном из выходов дешифратора вырабатывается сигнал, соответствующий 1, а на остальных выходах сохраняются сигналы, соответствующие 0. В общем случае дешифратор с n входами имеет 2n выходов, т.к. n-разрядный код входного слова может принимать 2n различных значений и каждому из этих значений соответствует сигнал 1 на одном из выходов дешифраторов. На выходах дешифраторов с номерами от 0 до 2n-1 вырабатываются значения булевых функций следующего вида: Для чего используются дешифраторы? Если на входы дешифратора подаются двоичные переменные, то на одном из выходов дешифратора вырабатывается сигнал, соответствующий 1, а на остальных выходах сохраняются сигналы, соответствующие 0. В общем случае дешифратор с n входами имеет 2n выходов, т.к. n-разрядный код входного слова может принимать 2n различных значений и каждому из этих значений соответствует сигнал 1 на одном из выходов дешифраторов. На выходах дешифраторов с номерами от 0 до 2n-1 вырабатываются значения булевых функций следующего вида: Для чего используются дешифраторы?   Дешифраторы устанавливаются в схемах вычислительных устройств, на выходах регистров или счетчиков и служат для преобразования кода слова, находящегося в регистре или счетчике, в управляющий сигнал на одном из выходов дешифраторов. На рисунке 5.2 показан способ построения дешифратора с инверсными выходами для 3-разрядного входного слова. Схема представляет собой набор из восьми элементов И-НЕ, на входы которых поданы все возможные комбинации прямых и инверсных значений разрядов слова. Если каждый выходной элемент дешифратора имеет вход для сигнала синхронизации, то такой дешифратор называется синхронизируемым, и при сигнале синхронизации С=1 все выходы такого дешифратора будут иметь единичное значение, а при сигнале С=0 он будет работать также, как и дешифратор с инверсными выходами. Какие операции могут выполняться в процессе обмена между локальной шиной процессора и системной шиной? Шины данных предназначены для передачи информации в двух направлениях. Шинные формирователи представляют собой двунаправленные устройства. Управление шинами формирователями осуществляется посредством двух сигналов: 1. Первый сигнал определяет время передачи данных. 2. Второй сигнал определяет направление передачи. Оба сигнала формируются микропроцессором в каждом цикле шины. Дешифраторы устанавливаются в схемах вычислительных устройств, на выходах регистров или счетчиков и служат для преобразования кода слова, находящегося в регистре или счетчике, в управляющий сигнал на одном из выходов дешифраторов. На рисунке 5.2 показан способ построения дешифратора с инверсными выходами для 3-разрядного входного слова. Схема представляет собой набор из восьми элементов И-НЕ, на входы которых поданы все возможные комбинации прямых и инверсных значений разрядов слова. Если каждый выходной элемент дешифратора имеет вход для сигнала синхронизации, то такой дешифратор называется синхронизируемым, и при сигнале синхронизации С=1 все выходы такого дешифратора будут иметь единичное значение, а при сигнале С=0 он будет работать также, как и дешифратор с инверсными выходами. Какие операции могут выполняться в процессе обмена между локальной шиной процессора и системной шиной? Шины данных предназначены для передачи информации в двух направлениях. Шинные формирователи представляют собой двунаправленные устройства. Управление шинами формирователями осуществляется посредством двух сигналов: 1. Первый сигнал определяет время передачи данных. 2. Второй сигнал определяет направление передачи. Оба сигнала формируются микропроцессором в каждом цикле шины. | ?В отличие от шин данных на шинах адресов выставляемые сигналы должны сохраняться значительно дольше, чем входные сигналы. Шинные формирователи адресов обязательно должны иметь память. Отличием шинных формирователей адресов от шин формирователей данных является их однонаправленность. Адресные сигналы всегда формируются микропроцессором и выставляются на шины адресов со стороны микропроцессора. или регистрами с защелками. В компьютерах IBM PC они выполняют функции шинных формирователей адресов. Что представляет собой шина управления?Шина управления представляет собой самостоятельную шину, по которой выставляются и передаются управляющие и синхронизирующие сигналы. Многие сигналы, оступающие на шину управления, формируются микропроцессором Какие операции могут выполняться в процессе обмена между локальной шиной процессора и системной шиной?Например, мост, который называется системный контроллер и буферный регистр данных в зависимости от цикла микропроцессора организует обмен данными между локальной шиной процессора и системной шиной, а также между локальной шиной и шиной ввода-вывода. В процессе обмена могут выполняться следующие операции: 1)Чтение данных из памяти; 2)Чтение данных из устройств.ввода-вывода информации; 3)Запись данных в память; 4)Запись данных в устройство ввода-вывода; 5)Подтверждение прерываний.. Что понимают под понятием «архитектура ЭВМ»? Под архитектурой ЭВМ понимается структура компьютера, существующая в текущий момент времени для выполнения ЭВМ конкретной задачи. Если будет решаться другая задача, то ЭВМ может быть представлена другой структурой, в которой содержатся другие устройства и блоки, отличные от первой архитектуры. Одним из требований, предъявляемых к архитектуре, должно быть представление о функционировании ЭВМ в соответствии с ее структурой. Архитектура ЭВМ охватывает обширный круг проблем, связанных с созданием комплекса аппаратных и программных средств и учитывающих большое количество определяющих факторов. Среди этих факторов самыми главными являются: стоимость, сфера применения, функциональные возможности, удобство в эксплуатации. Основным компонентом архитектуры считаются аппаратные средства. Архитектуру вычислительного средства необходимо отличать от его структуры. Структура вычислительного средства определяет его текущий состав на определенном уровне детализации и описывает связи внутри средства. Архитектура же определяет основные правила взаимодействия составных элементов вычислительного средства, описание которых выполняется в той мере, в какой необходимо для формирования правил их взаимодействия. Она устанавливает не все связи, а наиболее необходимые, которые должны быть известны для более грамотного использования применяемого средства. Из чего состоит любая вычислительная система? Во-первых, из того, что в англоязычных странах принято называть словом hardware, или техническое обеспечение: процессор, память, монитор, дисковые устройства и т.д., объединенные магистральным соединением, которое называется шиной. Во-вторых, вычислительная система состоит из программного обеспечения (software). | |

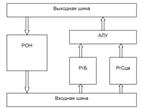

15. Какие компоненты входят в обрабатывающую часть микропроцессора? Процессоры современных ЭВМ ориентированы на обработку информации и управление ходом вычислительного процесса. Процессоры являются основой ЭВМ, основная особенность его функционирования – это программируемость работы.Под архитектурой микропроцессора понимается его схема техническая и логическая организация. Основным узлом микропроцессора является арифметико-логическое устройство, которое непосредственно предназначено для выполнения технических и логических операций с данными. Процессоры и микропроцессоры современных ЭВМ могут быть представлены, как два взаимодействующих модуля, из которых можно выделить устройство управления (УУ) и арифметико-логическое устройство (АЛУ). Условные обозначения: РОН – регистры общего назначения; РгБ – буферный регистр; РгСдв – регистр сдвига; Какие компоненты входят в обрабатывающую часть микропроцессора? В состав обрабатывающей части микропроцессора входят: блок регистров общего назначения, который часто называется сверхоперативным запоминающим устройством; буферный регистр; регистр сдвига.  Регистры общего назначения предназначены для хранения информационных слов, подлежащих обработке в АЛУ. Здесь же хранятся промежуточные результаты обработки информации и управляющие слова. Регистры общего назначения допускают считывание и запись информации, для чего предусмотрена их связь с выходной шиной, с шиной указания адреса, а также содержат управляющий вход, сигнал на котором создает режим работы микропроцессора, т.е. запись, хранение или чтение информации. Информация из регистров общего назначения может либо непосредственно поступать в АЛУ, либо может быть предварительно помещена в буферный или сдвиговый регистры, которые служат для предварительного хранения информации или осуществляют сдвиг информации непосредственно перед обработкой в АЛУ. Общие принципы функционирования системной памяти. В общем случае память вычислительной системы может быть представлена в виде некоторого многополюсника, который имеет соответствующую систему входов и выходов. На вход приходит информация в виде данных и адресов, а на выходе формируются сигналы, которые передаются в процессор. Один тип входов позволяет вводить информацию в память, а выход этого многополюсника представляет собой сформированные указания, куда будет размещаться выводимая информация, и откуда будет браться информация, выводимая из памяти. Вход для ввода информации это некоторый массив данных (na), а вход указания места хранения информации (nd). Таким образом, для ввода информации предусмотрено два входа. Один из них предназначен для ввода первичной информации, т.е. для ввода программы данных, для обеспечения запуска компьютера и обработки информации от внешних устройств. Другой вход предназначен для ввода информации от процессора во время обработки информации Регистры общего назначения предназначены для хранения информационных слов, подлежащих обработке в АЛУ. Здесь же хранятся промежуточные результаты обработки информации и управляющие слова. Регистры общего назначения допускают считывание и запись информации, для чего предусмотрена их связь с выходной шиной, с шиной указания адреса, а также содержат управляющий вход, сигнал на котором создает режим работы микропроцессора, т.е. запись, хранение или чтение информации. Информация из регистров общего назначения может либо непосредственно поступать в АЛУ, либо может быть предварительно помещена в буферный или сдвиговый регистры, которые служат для предварительного хранения информации или осуществляют сдвиг информации непосредственно перед обработкой в АЛУ. Общие принципы функционирования системной памяти. В общем случае память вычислительной системы может быть представлена в виде некоторого многополюсника, который имеет соответствующую систему входов и выходов. На вход приходит информация в виде данных и адресов, а на выходе формируются сигналы, которые передаются в процессор. Один тип входов позволяет вводить информацию в память, а выход этого многополюсника представляет собой сформированные указания, куда будет размещаться выводимая информация, и откуда будет браться информация, выводимая из памяти. Вход для ввода информации это некоторый массив данных (na), а вход указания места хранения информации (nd). Таким образом, для ввода информации предусмотрено два входа. Один из них предназначен для ввода первичной информации, т.е. для ввода программы данных, для обеспечения запуска компьютера и обработки информации от внешних устройств. Другой вход предназначен для ввода информации от процессора во время обработки информации | Память ЭВМ работает тактами. Полный такт работы называется временем обращения к памяти. Обращение к памяти может быть реализовано для записи информации в нее или для считывания из нее информации. Выполнить при одном обращении обе процедуры, т.е. записи и считывания,одновременно невозможно. Такт обращения выполняется за время T обр.При записи информации в память на вход na подается указание о том, куда в памяти будет записана информация. Затем на один из входов nd выставляется информация, подлежащая записи. После этого подается команда write. При чтении информации из памяти на вход na подается указание, откуда будет выбираться информация и затем подается команда read. На выходе многополюсника оявляется считываемая информация, которая и фиксируется процессором. Указания о месте расположения данных в памяти называют адресами. Как работает параллельным сумматором с последовательным переносом? От чего зависит его быстродействие? Обработка производится n-разрядных параллельных кодов чисел. При таком способе одновременно обрабатываются сразу все n разрядов. Чтобы обеспечить выполнение этих операций устройства ЭВМ должны меть входы для всех n разрядов числа. Обрабатывающим устройством является параллельный n-разрядный сумматор, который составляется из n одноразрядных сумматоров на три входа. На входы всех одноразрядных сумматоров биты разрядов слагаемых подаются одновременно. Однако разрядные суммы Si будут формироваться не одновременно, так как сумма второго разряда с номером 1 будет формироваться только тогда, когда на нее поступит перенос из нулевого разряда. Перенос поступает с задержкой на время, определяемое интервалом выполнения процедуры сложения. В связи с задержкой времени формирования переноса процесс сложения может быть организован за счет формирования полусумм, которое будет определяться, как время распространения переноса, которое зависит от количества разрядов сумматора. Такой сумматор, у которого формирование суммы происходит с задержкой на время формирования переноса, называется параллельным сумматором с последовательным переносом. Другой тип сумматора, в котором переносы из разряда в разряд формируются одновременно во всех разрядах, называют параллельным сумматором с параллельным переносом. Как правило, реализовать фактически такие операции полностью не удается. Быстродействие такого сумматора велико, но при этом оно зависит от разрядности обрабатываемых чисел. В настоящее время используют параллельные сумматоры с групповыми параллельно-последовательными переносами, у которых внутри групп перенососуществляется параллельно, а между группами последовательно. | |

| 16. Назовите основную особенность процессора ЭВМ. В основе особенности архитектуры микропроцессоров Intel лежит распределение зон оперативной памяти на сегменты, которые специализируются по применению, а именно сегменты данных, сегменты кодов, сегменты стека и т.д. Адреса обращения к этим сегментам формируются с использованием различных аппаратных средств. Это характерная особенность отражается на структуре команд и на архитектуре построения микропроцессоров. Для совместимости с микропроцессорами фирмы Intel необходимо полное соблюдение стандартов, разработанных для этой платформы. Что такое «совместимость сверху»?Важной стороной микропроцессоров фирмы Intel является их «совместимость сверху». Это позволяет использовать богатый комплекс программных продуктов, которые созданы для ЭВМ, построенных на базе микропроцессоров более ранних версий. Это может быть возможно только в том случае, когда сохраняется система команд микропроцессоров. В то же время система команд компьютеров старшего типа использует дополнительные команды, которых нет в микропроцессорах ранних версий. Фирмой Intel так организована система команд, что система команд процессоров, выпущенных ранее, является подмножеством команд компьютера старшего типа. Специалисты фирмы Intel утверждают, что компьютеры младших моделей являются составной частью от моделей старшего типа. Что определяет разрядность шины данных?Для оценки вычислительной мощности микропроцессоров следует оценивать разрядность шин данных и адресов. Разрядность шины данных определяет возможности компьютера передавать информацию от запоминающего устройства к процессору, либо от процессора к запоминающему устройству. Эта характеристика оказывает важное влияние на производительность компьютера. С другой стороны точность вычислений определяется разрядностью данных. Таким образом, для обеспечения вычислений с заданной точностью, данные должны представляться соответствующим числом разрядов, число разрядов при этом может оказаться большим числа разрядов шины данных. В этом случае информация из запоминающего устройства в процессор и обратно пересылается за несколько циклов шины данных. Такие многократные пересылки снижают производительность процессора, так как информацию можно обрабатывать только после поступления всех разрядов числа. Разрядность шины адресов определяет адресное пространство запоминающего устройства, к которому процессор обращается с произвольным доступом, т.е. к ячейке по любому адресу адресного пространства непосредственно. Адресное пространство в свою очередь определяет емкость запоминающего устройства. Как классифицируется память ЭВМ. по возможности хранения информации с включенным или выключенным • энергозависимой. Хранит информацию только при включенном напряжении питания. К таким устройствам памяти относится вся электронная и электрическая память; • энергонезависимая память. Сохраняет информацию при выключенном источнике питания. К ней относятся электромагнитная память, различного типа диодные и транзисторные матрицы, а также оптические диски, в которых информация может сохраняться длительное время.питанием; | по месту расположения; • Внутри ЭВМ – внутренняя память; • Вне ЭВМ – внешняя память. Названия внутренняя и внешняя являются условными. В настоящее время внутреннюю память определяют не только по месту ее расположения, а по тому, что обращение к ней производится по адресам, располагающимися непосредственно в командах процессора. Внешняя память, которая располагается внутри системного блоку или вне его адресуется через специальные программы или программы и другие физические устройства. по возможности записи информации в память в процессе решения задач; • Если такая запись является возможной, то память называется оперативной. • Если в процессе решения задачи из памяти информацию можно только читать, то такая память называется постоянной. В настоящее время только читаемую память называют ROM. В такую память информацию вносят вне цикла решения задачи. Например, при ее изготовлении на предприятии или при ее подготовке к решению задачи. Если информация может вноситься однократно, то память обозначается, как PROM, если многократно, с уф стиранием информации, то такая память обозначается EPROM, если память может использоваться многократно с электрическим стиранием информации, то такая память называется EEPROM. Последний вид памяти называется flash-memory или флэш-память. по порядку выборки; • Если по адресу, выставленному на адресный вход памяти сразу находится ячейка нужного номера, то такая память называется памятью с произвольным доступом. • Если такая память выполняет функции оперативной памяти, то ее называют сокращенно RAM (random access memory). Если после выставки адреса производится поиск нужной ячейки просмотром адресов других ячеек, то такая память называется памятью с последовательным доступом. по способу хранения информации? • В настоящее время существуют элементы памяти, которые принимают информацию и могут хранить ее до тех пор, пока не будет выключено электрическое питание. Выборка и считывание информации не влияет на ее содержание. Такой способ хранения информации определил название памяти, как статическая память. Элементы статической памяти выполняются на основе кодовых триггеров, ячейкой памяти, хранящей байт данных, является регистр из восьми кодовых RS-триггеров, выбираемых адресным словом. Память на триггерах является энергозависимой, а ее статическая особенность указывается как SRAM. • Другой способ хранения информации предполагает, что элемент памяти может терять информацию в процессе хранения и для того, чтобы информацию не утратить, ее необходимо периодически возобновлять или восстанавливать. Процесс восстановления информации называется регенерацией (refresh). Регенерацию производят периодически через каждые 15-20 микросекунд. Регенерируемую память называют динамической, если она является энергозависимой, то ее называют DRAM. В современной вычислительной технике это наиболее часто применяемая память. | |

| 17. Что такое арифметико-логическое устройство? Арифметико-логическое устройство предназначено для выполнения всех операций составляющих набор арифметических, логических и устройств обмена информацией с запоминающим устройством ЭВМ. Структурно-арифметико-логическое устройство входит в микропроцессор. Опишите, что происходит: На этапе формирования адреса очередной команды; На этапе формирования адреса команды под очередной командой понимается команда, выполняемая в данном командном машинном цикле. При этом сформированный адрес выставляется на шину адресов и находится в ней в течение всей продолжительности командного машинного цикла. Адрес очередной команды фиксируется специальным регистром адреса. При этом формирование адресов производится в соответствии со способом управления вычислительным процессом. Если управление вычислительным процессом осуществляется последовательно, то формирование номера очередной команды реализуется счетчиком, при этом счетчик называется счетчиком команд, а процедура формирования номера очередной команды реализуется как i+1. В том случае, если реализуется принудительный способ формирования адреса очередной команды, этот алгоритм определяется как i±y. Такой алгоритм вычисления адреса, как правило, реализую параллельным сумматором, где первое слагаемое представляет собой содержимое счетчика команд, а второе слагаемое представляет собой операнд команды безусловного или условного перехода. На этапе выборки команды из оперативной памяти и размещения кода команды в процессоре; На этапе выборки кода команды по выставленному на регистре числу (адресу) выбирается код очередной команды и размещается в регистре кода команды процессора, где хранится до конца выполнения текущей команды. Для этапа выборки кода команды на время пересылки кода магистраль процессора будет занята и никаких других пересылок информации между блоками ЭВМ выполняться не может. В этой связи введен критерий оценки производительности магистрали так называемый цикл шины, который представляет собой отрезок времени, за который по шине данных пропускается от источника до приемника слово основного формата. Словом основного формата может быть 1, 2, 3 или 4 байта. | На этапе формирования адресов операндов; Затем следует этап формирования адреса операнда. Для современных ЭВМ выполняемые команды могут быть безоперандовыми, однооперандовыми и двухоперандовми. В безоперандовых командах операнда может не быть. В однооперандовых командах может быть один адресуемый операнд или два операнда. Двухоперандовые команды адресуют сразу оба операнда, которые могут располагаться в процессоре. Вычисление адреса операнда или операндов производится по правилам адресации,принятым 54 для ЭВМ определенного класса. Для двухоперандовых команд один из операндов располагается в регистре процессора и его адрес может быть дешифрован по признакам, содержащимся в команде, а адрес другого операнда может вычисляться при помощи вычислительных средств, например, Аллу самого процессора. Вычисленный адрес при этом выставляется на регистр адреса как и адрес команды. На этапе выборки кода операнда из оперативной памяти или посылка операнда в оперативную память; На этапе выборки кода операнда по установленному в регистре адресу операнд извлекается из памяти и размещается в соответствующем адресе процессора. На этапе выполнения текущей команды? Этап выполнения текущей команды начинается с момента, когда код операции расположен в регистре кода команд и подключен к дешифратору кода команды, а операторы подключены, например к АЛУ. Что такое чипсет? Шинные формирователи могут входить составными частями в более крупные интегральные схемы, размещенные на системной плате компьютера. Такие интегральные схемы называют чипсетом. Они совместно с процессором выполняют объединение всех элементов в единую вычислительную систему. | |

| 18. Чем отличаются шинные формирователи адресов от шин формирователей данных? Посредством чего осуществляется управление шинами-формирователями? Шины данных предназначены для передачи информации в двух направлениях. Шинные формирователи представляют собой двунаправленные устройства. Управление шинами формирователями осуществляется посредством двух сигналов: 1. Первый сигнал определяет время передачи данных. 2. Второй сигнал определяет направление передачи. Оба сигнала формируются микропроцессором в каждом цикле шины. Что такое чипсет?Шинные формирователи могут входить составными частями в более крупные интегральные схемы, размещенные на системной плате компьютера. Такие интегральные схемы называют чипсетом. Они совместно с процессором выполняют объединение всех элементов в единую вычислительную систему. Чем отличаются шинные формирователи адресов от шин формирователей данных? В отличие от шин данных на шинах адресов выставляемые сигналы должны сохраняться значительно дольше, чем входные сигналы. Шинные формирователи адресов обязательно должны иметь память. Отличием шинных формирователей адресов от шин формирователей данных является их однонаправленность. Адресные сигналы всегда формируются микропроцессором и выставляются на шины адресов со стороны микропроцессора. Как устроены формирователи шин адресов? Подключение формирователя шин адресов осуществляется через системный регистр, находящийся в микропроцессоре. В каждом разряде системного регистра используется D-триггер. На каждый из D входов от микропроцессора подаются соответствующие разряды адреса, сформированного микропроцессора. Входы синхронизации триггеров объединяют между собой, образую один управляющий вход записи в системный регистр. Управляющий сигналы подаются на входы системного регистра, причем управляющим сигналом может быть сигнал, синхронизирующий выставку адресного слова на шину адресов. Специфика работы системного регистра используемого в качестве шинного формирователя адресов заключается в запоминании, фиксации и хранении адреса. Такие регистры часто называют индексными регистрами или регистрами с защелками. В компьютерах IBM PC они выполняют функции шинных формирователей адресов. Что представляет собой шина управления?Шина управления представляет собой самостоятельную шину, по которой выставляются и передаются управляющие и синхронизирующие сигналы. Многие сигналы, поступающие на шину управления, формируются микропроцессором. | Какие операции могут выполняться в процессе обмена между локальной шиной процессора и системной шиной? Какие операции могут выполняться в процессе обмена между локальной шиной процессора и системной шиной? Например, мост, который называется системный контроллер и буферный регистр данных в зависимости от цикла микропроцессора организует обмен данными между локальной шиной процессора и системной шиной, а также между локальной шиной и шиной ввода-вывода. В процессе обмена могут выполняться следующие операции: 1. Чтение данных из памяти; 2. Чтение данных из устройств ввода-вывода информации; 3. Запись данных в память; 4. Запись данных в устройство ввода-вывода; 5. Подтверждение прерываний.. Что определяет разрядность шины данных? Для оценки вычислительной мощности микропроцессоров следует оценивать разрядность шин данных и адресов. Разрядность шины данных определяет возможности компьютера передавать информацию от запоминающего устройства к процессору, либо от процессора к запоминающему устройству. Эта характеристика оказывает важное влияние на производительность компьютера. С другой стороны точность вычислений определяется разрядностью данных. Таким образом, для обеспечения вычислений с заданной точностью, данные должны представляться соответствующим числом разрядов, число разрядов при этом может оказаться большим числа разрядов шины данных. В этом случае информация из запоминающего устройства в процессор и обратно пересылается за несколько циклов шины данных. Такие многократные пересылки снижают производительность процессора, так как информацию можно обрабатывать только после поступления всех разрядов числа. Разрядность шины адресов определяет адресное пространство запоминающего устройства, к которому процессор обращается с произвольным доступом, т.е. к ячейке по любому адресу адресного пространства непосредственно. Адресное пространство в свою очередь определяет емкость запоминающего устройства. | |

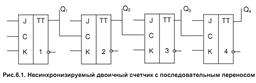

19. Какие типы счетчиков существуют? С чем связано понижение предельной частоты работы счетчика с последовательным переносом при росте разрядности счетчика?Какая схема используется для повышения быстродействия счетчика?Счетчик – узел ЭВМ, предназначенный для подсчета числа входных сигналов. Счетчики используются для образования последовательности .Счетчики подразделяются на: суммирующие; вычитающие; реверсивные. 19. Какие типы счетчиков существуют? С чем связано понижение предельной частоты работы счетчика с последовательным переносом при росте разрядности счетчика?Какая схема используется для повышения быстродействия счетчика?Счетчик – узел ЭВМ, предназначенный для подсчета числа входных сигналов. Счетчики используются для образования последовательности .Счетчики подразделяются на: суммирующие; вычитающие; реверсивные.  Схемы несинхронизируемого счетчика с последовательным переносом (рис.6.1) построена на JK-триггерах, у которых на входы J и K подаются сигналы соответствующие двоичной единице. Выход каждого предыдущего триггера соединен с входом синхронизации Cn последующего триггера. Каждый JK-триггер выполняет функцию несинхронизируемого триггера со счетным входом. По спаду единичного выходного сигнала изменяется состояние триггера младшего разряда счетчика на противоположное. В последующих разрядах аналогичное действие выполняет математическую операцию переноса единицы в старший разряд. Как правило, счетчик имеет цепь установки в нулевое состояние. Начальное состояние может быть задано передачей в счетчик некоторого числа, с которого затем будет начинаться операция подсчета единиц. Такой режим работы необходим счетчику при образовании последовательности адресов команд при заданном исходном адресе. С ростом разрядности счетчика понижается предельная частота его работы. Это объясняется тем, что с ростом разрядности счетчика n будет возрастать задержка поступления сигнала на вход синхронизации некоторого j-го разряда относительно поступления входного сигнала x счетчика на вход синхронизации младшего разряда счетчика.Чтобы повысить быстродействие счетчиков часто используется схема с параллельным переносом (рис. 6.3). Особенностью данной схемы является то, что выходы всех предшествующих разрядов подаются на входы J и K j-го триггера. Длительность переходного процесса в таком счетчике равна длительности переключения одного разряда. С возрастанием порядкового номера триггера увеличивается число входов в элементах i JK-триггеров. Так как число входов J и K и нагрузочная способность триггеров ограничены, то разрядность счетчика с параллельным переносом невелика (8, 16 разрядов). Поэтому при числе разрядов счетчика большем максимального числа входов J и K, счетчик разбивают на группы и внутри каждой группы строят цепи параллельного переноса. В таком случае при последовательном переносе возрастает разрядность счетчика. Схемы несинхронизируемого счетчика с последовательным переносом (рис.6.1) построена на JK-триггерах, у которых на входы J и K подаются сигналы соответствующие двоичной единице. Выход каждого предыдущего триггера соединен с входом синхронизации Cn последующего триггера. Каждый JK-триггер выполняет функцию несинхронизируемого триггера со счетным входом. По спаду единичного выходного сигнала изменяется состояние триггера младшего разряда счетчика на противоположное. В последующих разрядах аналогичное действие выполняет математическую операцию переноса единицы в старший разряд. Как правило, счетчик имеет цепь установки в нулевое состояние. Начальное состояние может быть задано передачей в счетчик некоторого числа, с которого затем будет начинаться операция подсчета единиц. Такой режим работы необходим счетчику при образовании последовательности адресов команд при заданном исходном адресе. С ростом разрядности счетчика понижается предельная частота его работы. Это объясняется тем, что с ростом разрядности счетчика n будет возрастать задержка поступления сигнала на вход синхронизации некоторого j-го разряда относительно поступления входного сигнала x счетчика на вход синхронизации младшего разряда счетчика.Чтобы повысить быстродействие счетчиков часто используется схема с параллельным переносом (рис. 6.3). Особенностью данной схемы является то, что выходы всех предшествующих разрядов подаются на входы J и K j-го триггера. Длительность переходного процесса в таком счетчике равна длительности переключения одного разряда. С возрастанием порядкового номера триггера увеличивается число входов в элементах i JK-триггеров. Так как число входов J и K и нагрузочная способность триггеров ограничены, то разрядность счетчика с параллельным переносом невелика (8, 16 разрядов). Поэтому при числе разрядов счетчика большем максимального числа входов J и K, счетчик разбивают на группы и внутри каждой группы строят цепи параллельного переноса. В таком случае при последовательном переносе возрастает разрядность счетчика. | Что такое система логических элементов ЭВМ?  Системой или комплексом или серией логических элементов ЭВМ называется предназначенный для построения цифровых устройств функционально полный набор логических элементов, объединяемых общими электрическими, конструктивными и технологическими параметрами, использующий одинаковый тип представления информации и одинаковый способ межэлементных связей. Логические операции над двоичными переменными реализуются схемами, которые называются комбинационными логическими элементами. Число входов комбинационного логического элемента соответствует числу аргументов воспроизводимых им одной или несколькими булевыми функциями. В свою очередь комбинационная схема строится из элементарных схем, называемых логическими элементами. Последовательно соединение комбинационных схем соответствует подстановки в булевой функции в качестве аргументов других булевых функций. Пересоединение на входах комбинационных схем соответствует перестановки аргументов булевых функций.Схемы, в которых показаны связи между различными логическими элементами, называют функциональными. При этом сами элементы представляются условными обозначениями.Что происходит при потенциальном способе передачи информации?Что происходит при импульсном способе передачи информации?Для физического представления информации в цифровых устройствах ЭВМ применяют потенциальные и импульсные способы представления информации.При потенциальном способе двум значениям двоичной переменной соответствуют разные формы потенциалов, соответствующей точки схемы цифрового электронного устройства. Электрический сигнал при потенциальном ходе сохраняет постоянный уровень в течение такта, а его значения в переходные моменты времени не являются определёнными.При импульсном способе передачи информации единичное и нулевое значение двоичной переменной отображаются наличием или отсутствием электрического импульса или разно-полярными импульсами в соответствующей точке электронной схемы. Импульсный сигнал характеризует амплитудой импульса, продолжительностью импульса по основанию, а так же длительностью фронта импульса и среза импульса.В зависимости от применяемого кода для обработки информации устройства вычислительной техники называют последовательными или параллельными. Устройства, реализующие последовательный код работают значительно медленнее, поэтому в современных ЭВМ основные устройства, участвующие в обработке информации для достижения высокого быстродействия строятся как параллельные, хотя и требуют большего количество аппаратуры. Системой или комплексом или серией логических элементов ЭВМ называется предназначенный для построения цифровых устройств функционально полный набор логических элементов, объединяемых общими электрическими, конструктивными и технологическими параметрами, использующий одинаковый тип представления информации и одинаковый способ межэлементных связей. Логические операции над двоичными переменными реализуются схемами, которые называются комбинационными логическими элементами. Число входов комбинационного логического элемента соответствует числу аргументов воспроизводимых им одной или несколькими булевыми функциями. В свою очередь комбинационная схема строится из элементарных схем, называемых логическими элементами. Последовательно соединение комбинационных схем соответствует подстановки в булевой функции в качестве аргументов других булевых функций. Пересоединение на входах комбинационных схем соответствует перестановки аргументов булевых функций.Схемы, в которых показаны связи между различными логическими элементами, называют функциональными. При этом сами элементы представляются условными обозначениями.Что происходит при потенциальном способе передачи информации?Что происходит при импульсном способе передачи информации?Для физического представления информации в цифровых устройствах ЭВМ применяют потенциальные и импульсные способы представления информации.При потенциальном способе двум значениям двоичной переменной соответствуют разные формы потенциалов, соответствующей точки схемы цифрового электронного устройства. Электрический сигнал при потенциальном ходе сохраняет постоянный уровень в течение такта, а его значения в переходные моменты времени не являются определёнными.При импульсном способе передачи информации единичное и нулевое значение двоичной переменной отображаются наличием или отсутствием электрического импульса или разно-полярными импульсами в соответствующей точке электронной схемы. Импульсный сигнал характеризует амплитудой импульса, продолжительностью импульса по основанию, а так же длительностью фронта импульса и среза импульса.В зависимости от применяемого кода для обработки информации устройства вычислительной техники называют последовательными или параллельными. Устройства, реализующие последовательный код работают значительно медленнее, поэтому в современных ЭВМ основные устройства, участвующие в обработке информации для достижения высокого быстродействия строятся как параллельные, хотя и требуют большего количество аппаратуры. | |

20.Чем отличается представление информации с помощью последовательного кода от представления информации с помощью параллельного кода? При последовательном коде все разряды двоичного слова разбиваются на временные такты таким образом, что каждый разряд представляется на отдельном такте. В этом случае все разряды слова фиксируются отдельными элементами и проходят через одну линию передачи информации. При параллельном коде все разряды двоичного слова представляются в одном временном такте, каждый разряд фиксируется отдельным элементом и каждый разряд проходит через отдельную линию, каждая из которых служит для представления и передачи только одного разряда слова. При параллельной передаче информации код слова развёртывается не во времени, а в пространстве, т.к. значения всех разрядов передаются одновременно.В зависимости от применяемого кода для обработки информации устройства вычислительной техники называют последовательными или параллельными. Устройства, реализующие последовательный код работают значительно медленнее, поэтому в современных ЭВМ основные устройства, участвующие в обработке информации для достижения высокого быстродействия строятся как параллельные, хотя и требуют большего количество аппаратуры.Для экономии оборудования в некоторых устройствах применяют последовательно-параллельный код, при котором слова разбиваются на части и обработка информации производится последовательно слог за слогом, а в свою очередь каждый слог представляется параллельным кодом. Перечислите логические элементы, напишите их функции и нарисуйте условные обозначения.  Логические операции над двоичными переменными реализуются схемами, которые называются комбинационными логическими элементами. Число входов комбинационного логического элемента соответствует числу аргументов воспроизводимых им одной или несколькими булевыми функциями. В свою очередь комбинационная схема строится из элементарных схем, называемых логическими элементами. Последовательно соединение комбинационных схем соответствует подстановки в булевой функции в качестве аргументов других булевых функций. Пересоединение на входах комбинационных схем соответствует перестановки аргументов булевых функций.Схемы, в которых показаны связи между различными логическими элементами, называют функциональными. При этом сами элементы представляются условными обозначениями. Логические операции над двоичными переменными реализуются схемами, которые называются комбинационными логическими элементами. Число входов комбинационного логического элемента соответствует числу аргументов воспроизводимых им одной или несколькими булевыми функциями. В свою очередь комбинационная схема строится из элементарных схем, называемых логическими элементами. Последовательно соединение комбинационных схем соответствует подстановки в булевой функции в качестве аргументов других булевых функций. Пересоединение на входах комбинационных схем соответствует перестановки аргументов булевых функций.Схемы, в которых показаны связи между различными логическими элементами, называют функциональными. При этом сами элементы представляются условными обозначениями. |  Назовите два типа устройств управления микропроцессоров. Чем они отличаются друг от друга? Назовите недостатки микропрограммного способа управления. Назовите недостатки микропроцессора с фиксированной системой команд. Для управления выполнением операций, выбором команд программы в необходимой последовательности, их дешифровки и обработки составляющих модулей служат входящие в микропроцессор устройства управления.В настоящее время применяются микропроцессоры с двумя типами устройств Назовите два типа устройств управления микропроцессоров. Чем они отличаются друг от друга? Назовите недостатки микропрограммного способа управления. Назовите недостатки микропроцессора с фиксированной системой команд. Для управления выполнением операций, выбором команд программы в необходимой последовательности, их дешифровки и обработки составляющих модулей служат входящие в микропроцессор устройства управления.В настоящее время применяются микропроцессоры с двумя типами устройств  управления: с микропрограммным управлением с фиксированной системой команд МП – микропроцессор; ДШ – дешифратор; ЗУ – запоминающее устройство. Микропрограммным способом управления позволяет легко вносить изменения в систему команд микропроцессора путем записи в запоминающее устройство микропрограммы выполнения новой программы. Такие устройства управления имеют недостатки, вызванные ограниченностью скоростью быстродействия микропроцессора, быстродействие управляющего запоминающего устройства. В микропроцессоре с фиксированной системой команд управляющий блок расшифровывает поступившую команду и в соответствии с ее кодом вырабатывает управляющие сигналы в необходимой последовательности. Расшифровке поддаются только те команды, которые входят в систему команд данного микропроцессора. Такой способ организации управления получил название жесткого или схемного. К недостаткам такого способа управления относится жесткость и сложность структуры управляющего устройства. Положительным качеством является высокое быстродействие такой схемы управления. управления: с микропрограммным управлением с фиксированной системой команд МП – микропроцессор; ДШ – дешифратор; ЗУ – запоминающее устройство. Микропрограммным способом управления позволяет легко вносить изменения в систему команд микропроцессора путем записи в запоминающее устройство микропрограммы выполнения новой программы. Такие устройства управления имеют недостатки, вызванные ограниченностью скоростью быстродействия микропроцессора, быстродействие управляющего запоминающего устройства. В микропроцессоре с фиксированной системой команд управляющий блок расшифровывает поступившую команду и в соответствии с ее кодом вырабатывает управляющие сигналы в необходимой последовательности. Расшифровке поддаются только те команды, которые входят в систему команд данного микропроцессора. Такой способ организации управления получил название жесткого или схемного. К недостаткам такого способа управления относится жесткость и сложность структуры управляющего устройства. Положительным качеством является высокое быстродействие такой схемы управления. |