Доступ к линиям т1/серт. поддержка basic isdn

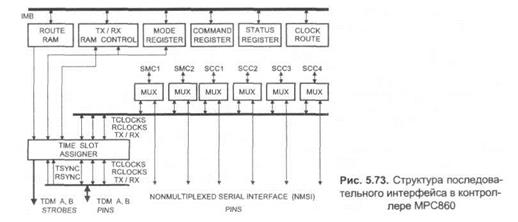

Последовательный интерфейс. Физический интерфейс SI (Serial Interface) может работать в двух режимах: TSA и NMSI. Режим TSA (Time Slot Assigner) или мультиплексированный режим объединяет передачу данных от нескольких каналов ввода/вывода в режиме временного мультиплексирования на общие выводы. В контроллере МРС860 (рис. 5.73) блок TSA имеет собственные внешние контакты для двух каналов временного мультиплексирования: TDMa и TDMb (Time Division Multiplexed). При совместной работе нескольких каналов в коммуникационных контроллерах возможна любая комбинация режимов работы TSA и NMSI для каждого из каналов.

В режиме TSA синхронизация работы каналов осуществляется через внешние контакты (TCLOCK и RCLOCK в СРМ или TCLK и RCLK в СР) от внешнего источника. Каждый TDM-канал имеет независимые приемник и передатчик, которые используют каждый свою внешнюю синхронизацию через контакты RCLOCK и TCLOCK, и свои внешние пробирующие сигналы RSYNC и TSYNC, которые уведомляют о начале нового кадра данных. Работа каждого TDM-канала может быть запрограммирована на срабатывание или по положительному или по отрицательному фронту тактового сигнала.

Максимальная частота синхронизации TSA-каналов - это системная частота, деленная на 2,5 (SyncCLK/2,5). Напомним, что модуль конфигурации системы SIM60 может производить предварительное деление системной частоты. Системная частота зависит от частоты знешнего источника тактирования контроллера (обычно это кварц) и равна 1/2 частоты внешнего кварца. Например, если частота кварца 25 МГц, то SyncCLK равна 12,5 МГц.

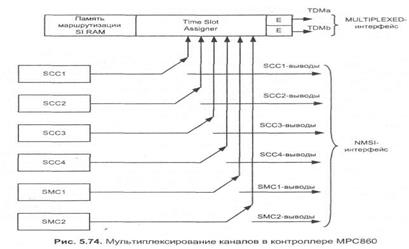

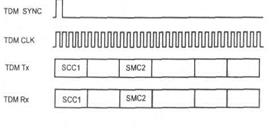

Блок Time Slot Assigner (TSA) обеспечивает на каждом TDM-канале объединение данных от двух-четырех любых SCC-контроллеров и двух SMC-контроллеров в два мультиплексированных интерфейса с временным разделением TDM (рис. 5.74), использующих форматы:

• Motorola Interchip Digital Link (IDL);

• General Circuit Interface (GCI), известный как IOM-2;

• Pulse Code Modulation (PCM) Highway Interface;

• Т1/СЕРТ-ЛИНИЙ;

• User-defined interace.

В немультиплексируемом режиме NMSI (Nonmultiplexed Serial Interface) каждый канал - SCC или SMC имеет собственные внешние контакты (через контакты параллельных портов А, В и С) и может работать независимо от других каналов.

Каждый SCC-канал в режиме NMSI поддерживает следующие модемные сигналы: TXD, RXD, TCLK, RCLK,  ,

,  ,

,  . Поддержку дополнительных сигналов DSR и DTD пользователь может запрограммировать через порты ввода/вывода .В СРМ каналы SMC также имеют четыре внешних контакта: SMTXD, SMRXD, CLK и

. Поддержку дополнительных сигналов DSR и DTD пользователь может запрограммировать через порты ввода/вывода .В СРМ каналы SMC также имеют четыре внешних контакта: SMTXD, SMRXD, CLK и  . Если контроллер канала ввода/вывода работает в мультиплексируемом режиме, то его NMSI-выводы могут быть использованы для других целей как линии параллельных портов.

. Если контроллер канала ввода/вывода работает в мультиплексируемом режиме, то его NMSI-выводы могут быть использованы для других целей как линии параллельных портов.

В режиме NMSI в СРМ каждый канал может тактироваться или от восьми внешних источников тактовых сигналов, или от четырех встроенных генераторов скорости передачи BRG. В режиме NMSI максимальная частота синхронизации каналов - это системная частота, деленная на два (SyncCLK/2).

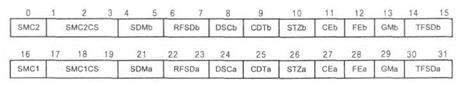

Настройка режимов работы последовательного интерфейса. Главным регистром, который определяет работу физического интерфейса SI в мультиплексируемом TSA- и немультиплексируемом NMSI-режимах, является регистр режима SIMODE (рис. 5.75).

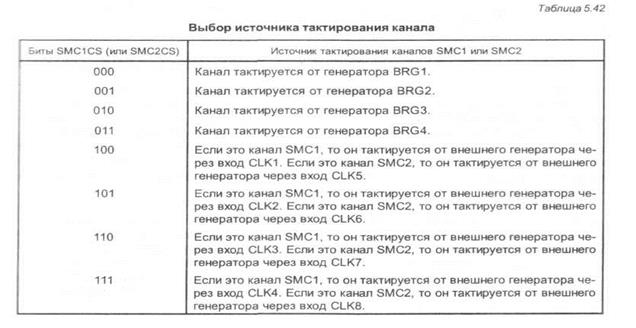

Биты SMC1 и SMC2 определяют режим работы соответствующих каналов управления SMC1 иSMC2(0-peжимNMSI, 1 - режим TSA). Каналы SMC могут иметь независимые источники тактирования, но всегда приемник и передатчик одного канала используют одну частоту синхронизации, и, если каналы SMC работают в немультиплексируемом режиме NMSI, то биты SMC1CS и SMC2CS определяют источник тактирования для данного канала управления (табл. 5.42).

|

Рис. 5.75. Формат регистра настройки режимов работы последовательного интерфейса SIMODE в контроллере МРС860

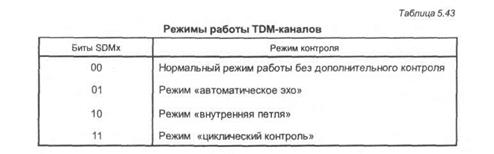

Во всех коммуникационных контроллерах интерфейс SI поддерживает режимы контроля аппаратуры приемника и передатчика. Биты SDMa и SDMb определяют, какой режим контроля выбран для канала TDMa и канала TDMb (табл. 5.43).

В режиме автоматического эха канал сразу же передает принятый от физического интерфейса бит данных. Значения сигналов на контакте L1GRX игнорируются. В режиме внутренней петли происходит внутреннее соединение выводов LITXDx и MRXDx. Данные передаются по линии LITXDx и сразу же читаются. Сигнал L1RQx выставляется нормально, а значения сигналов на входах L1 RXDx и L1 GRx игнорируются. Режим циклического контроля работает аналогично режиму внутренней петли, только он предназначен для контроля работы аппаратуры приемника и передатчика без воздействия на внешние выводы микросхемы. Поэтому внешние выводы LITXDx и MRGx остаются в неактивном состоянии.

В модуле СРМ предусмотрена возможность работы с повышенной частотой синхронизации, так как некоторые TDM-каналы при работе в режиме GCI-интерфейса требуют, чтобы на каждый битовый интервал приходилось по два периода тактового сигнала. Биты DЗСа и DSCb, если они равны единице, определяют для своего канала TDMx режим заботы с удвоенной частотой.

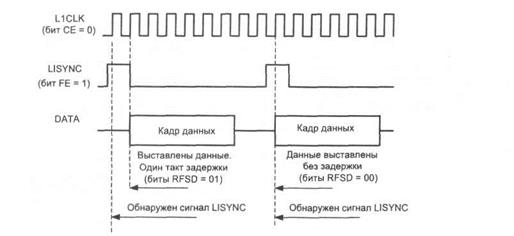

Каждый кадр данных при работе в режиме TSA стробируется внешним сигналом SYNC. Обычно наличие этого сигнала в TDMx-канале проверяется по положительному перепаду тактового сигнала CLK, если биты FEa и FEb равны единице для каналов TDMa и TDMb соответственно, и по отрицательному перепаду тактового сигнала, если эти биты равны нулю. Анализ наличия стробирующего сигнала по отрицательному перепаду тактового сигнала используется, если выбранный TDMx-канал работает с IDL-или GCI-интерфейсами.

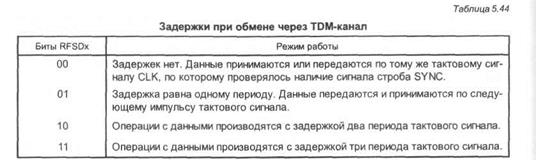

Биты RFSDa, RFSDb, TFSDa и TFSDb определяют количество тактов задержки при передаче/приеме на выбранном канале TDMa или TDMb (табл. 5.44).

Значения битов СЕа и СЕЬ определяют, по какому перепаду тактового сигнала CLK производятся операции с данными на каналах TDMa и TDMb соответственно. Если бит равен нулю, то на выбранном TDMx-канале данные передаются по положительному перепаду тактового сигнала и считываются по отрицательному перепаду. Такой режим обработки данных используется при работе с IDL- и GCI-интерфейсами. Если бит равен единице, то на выбранном TDMx-канале данные выставляются по отрицательному перепаду тактового сигнала, а считываются - по положительному. На рис. 5.76 представлен пример настройки работы последовательного интерфейса.

TDM-канал при работе может поддерживать механизм запросов на передачу по D-каналу (grant механизм). Биты GMa и GMb определяют, для какого физического интерфейса GCI (значение бита равно нулю) или IDL (значение бита равно единице) будет включен этот механизм. Дополнительно пользователь должен настроить каждый SCC-канал на поддержку механизма запросов, установив биты GR1-GR4 в регистре SICR.

Если биты STZa и/или STZb имеют значение «1», то для GCI-активации данного TDM-канала будет использована установка в «0» сигналов на линиях LITXDa и/или UTXDb при передаче тактовых сигналов CLK.

Реализация функций маршрутизации. TSA разрешает одновременную работу двух полнодуплексных TDM-каналов. Каждый TDM-канал может работать с временными каналами, длина которых задается как в битах, так и в байтах. Максимальная длина обрабатываемого кадра для МРС860 составляет 8192 бита. Максимальное число обрабатываемых временных каналов в в МРС860 - 64. Каналы могут обмениваться данными между

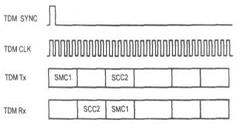

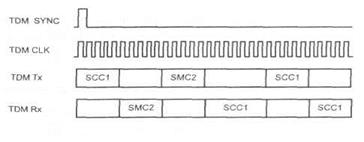

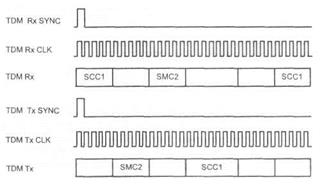

своими временными слотами, и TSA может решать задачи маршрутизации временных каналов с помощью программирования внутренней памяти маршрутизации SI RAM. Примеры использования TDM-каналов приведены на рис. 5.77 - 5.80.

|

Рис. 5.76. Пример настройки последовательного интерфейса. Первый кадр данных выставляется с одним тактом задержки (бит RFSD = 01), второй -без задержки (бит RFSD = 00). Данные передаются по положительному перепаду тактового сигнала L1CLK (бит СЕ = 0). Анализ сигнала L1SYNC производится по положительному перепаду тактового сигнала (бит FE = 1)

|

Рис. 5.77. Один внешний сигнал строба кадра SYNC и одна внешняя синхронизация используются и для приемника Rx, и для передатчика Тх одного TDM-канала. Модификация временных каналов не производится

|

Рис.5.78 Один внешний сигнал строба

кадра SYNC и одна внешняя синхронизация

используются и для приемника Rx, и для передатчика Тх одного TDM-канала

Производится изменение временного слота

для данных от каналов SCC2 и SМС1.

|

Рис. 5.79. Производится модификация временных каналов. Изменяется размер каналов. Данные от SCC1 занимают несколько временных слотов при приеме и выдаются в другие временные слоты при передаче с изменением размеров этих временных слотов

|

Рис. 5.80. Полностью независимые приемная (Rx) и передающая (Тх) части, каждая использует свою частоту синхронизации и свой сигнал стробирования кадра. Также производится модификация временных слотов

При работе с временными каналами TSA дополнительно поддерживает выработку четырех внешних стробирующих сигналов-L1STA1,L1STA2, L1STB1 и L1STB2. Функционирование этих стробов не зависит от работы SCC- и SMC-каналов, и они могут быть использованы для управления обменом данными с другими устройствами, которые не поддерживают работу в режиме временного мультиплексирования.

Использование памяти маршрутизации SI RAM. Программирование функций маршрутизации или функций обмена данными между временными слотами производится с использованием специальной памяти маршрутизации SI RAM, которая введена в состав СРМ. Память маршрутизации состоит из двух частей, каждая размером 64x16 бит в МРС860. Одна часть памяти используется для управления маршрутизацией принимаемой информации, другая -для управления пересылкой передаваемой информации.

Суммарный объем SI RAM в МРС860 - 256 байт. Память маршрутизации расположена во внутренней памяти регистров контроллера и может программироваться центральным процессором. Следует обратить внимание, что SI RAM расположена не в двухпортовой памяти и предназначена только для управления потоками данных между временными слотами TDM-каналов и буферами контроллеров SCC- и SMC-каналов и не используется для хранения данных. С помощью памяти маршрутизации пользователь может определять, информация какого SCC- или SMC-канала будет передана/принята на какой TDM-канал, в какой временной слот и каким внешним стробирующим сигналом она будет синхронизирована. Размер каждой части SI RAM зависит от конфигурации TDM-каналов и может иметь, например, для МРС860 контроллера максимальный размер 256 байт или минимальный размер 32 байта.

SI RAM состоит из ячеек (entries), которые определяют режимы работы и параметры каждого временного слота. Содержимое i-ячейки (рис. 5.81) определяет, как будет обрабатываться i-временной слот кадра. Число ячеек равно числу поддерживаемых временных слотов в кадре данных. Бит LST = 1, установленный в некоторой ячейке, сообщает,что кадр данных закончен, и это ячейка соответствовала последнему временному каналу этого кадра. Это значит, что теперь Sl-интерфейс заканчивает обработку текущего кадра и будет ждать появления нового внешнего SYNC-сигнала, стробирующего начало нового кадра, чтобы начать обработку нового кадра. Если бит LST = 0, то текущий временной канал - не последний в кадре, и Sl-интерфейс читает содержимое очередной ячейки, чтобы определить правила обработки следующего временного слота.

|

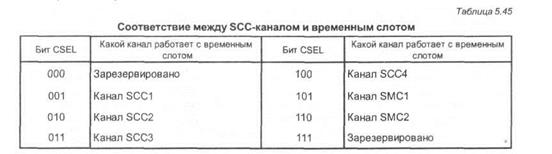

Биты CSEL определяют, откуда будет взята информация для выбранного временного

слота(табл.5.45).

Размер временного слота определяют биты CNT и BYT. Если BYT = 0, то размер равен (CNT+1) бит. Если BYT = 1, то размер равен (CNT+1) байт.

Биты SSEL1-SSEL4 определяют, какой из внешних стробирующих сигналов -L1STA1, L1STA2, L1STB1, L1STB2 может быть выставлен в течение временного слота. Возможно использовать для стробирования одного временного канала одновременно несколько стробирующих сигналов. Если один стробирующий сигнал выбран для двух последовательных временных каналов, то он будет удерживаться без сброса на границе временных каналов.

Бит SWTR используется для особых случаев, когда пользователь желает принимать данные с Тх-входа и передавать данные на Rx-выход. Этот режим может быть применен для функций контроля работы приемника и передатчика каждого TDM-канала. Установка этого бита оказывает влияние только на часть SI RAM, которая относится к приемнику, и на состояние сигналов на контактах L1RXD и L1TXD.

При значении бита LOOP = 1 включается тестовый режим для выбранного временного слота. В этом режиме полученные с контакта RXD данные будут бит за битом передаваться на контакт TXD.

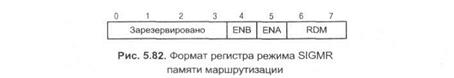

Выбор режима работы TDM-каналов производится при программировании регистра режима SI SIGMR, формат которого приведен на рис. 5.82.

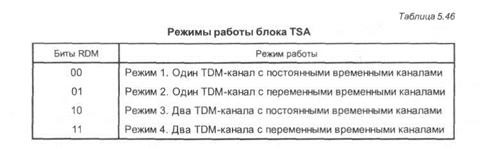

Биты RDM[1], RDM[0] задают один из четырех режимов работы, описанных в

табл. 5.46.

|

Биты ENb и ENa определяют, работает ли маршрутизация на каналах TDMb и TDMa. Если бит ENx равен единице, то память SI RAM доступна при работе данного канала.

При режиме работы TDM-каналов с переменными временными каналами назначение источников маршрутизации и параметров канала может быть изменено во время работы. Для этого SI RAM дополнительно делится на основную, с которой работает TSA в данный момент времени, и теневую, в которую пользователь вносит свои изменения в таблицу маршрутизации. Когда все изменения внесены, пользователь устанавливает соответствующие биты - CSRRa, CSRTa, CSRRb, CSRTb в регистре команд SICMR (рис. 5.83). Биты CSRRa и CSRRb, равные единице, задают смену назначения частей памяти для приемников каналов TDMa и TDMb соответственно, а биты CSRTa и CSRTb, равные единице, -для передатчиков каналов TDM. В результате происходит преобразование теневой памяти (shadow RAM) в основную. Преобразование предусматривает смену внутреннего назначения частей памяти, теневая становится основной, а основная - теневой. По окончании преобразования сбрасывается соответствующий бит CSRxx.

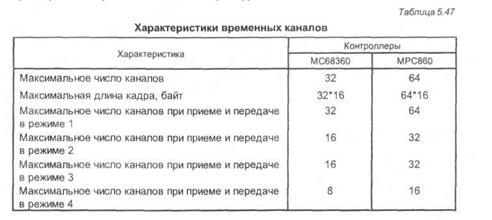

Характеристики временных каналов приведены в табл. 5.47.

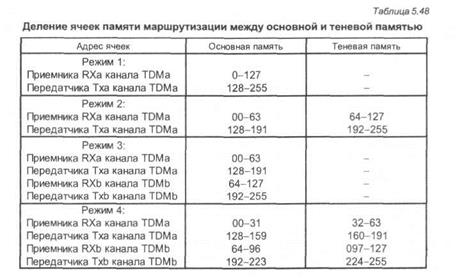

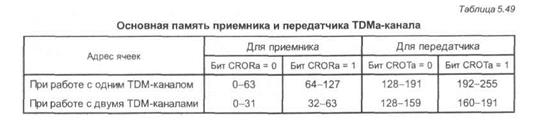

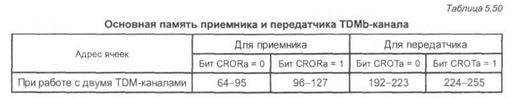

Режим 1. SI RAM разделена на две части - по 64 ячейки у МРС860. Работает только канал TDMa. Теневая память не используется (табл. 5.48). Все ячейки расположены в основной памяти. Максимальное число обрабатываемых временных каналов в кадре - 64.

Режим 2. SI RAM разделена на четыре части - по 32 ячейки у МРС860. Максимальное число обрабатываемых временных каналов в кадре - 32. Работает только канал TDMa. Распределение памяти проиллюстрировано в табл. 5.48.

Режим 3. SI RAM разделена на четыре части - по 32 ячейки у МРС860. Максимальное число обрабатываемых временных каналов в кадре - 32. Работают оба TDM-канала. Теневая память не используется (табл. 5.48). Все ячейки расположены в основной памяти.

Режим 4. SI RAM разделена на восемь частей - по 16 ячейки у МРС860. Максимальное число обрабатываемых временных каналов в кадре -16. Работают оба TDM-канала (табл. 5.48).

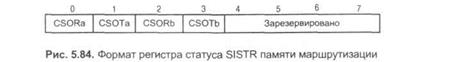

Пользователь может в любой момент времени прочитать содержимое регистра статуса SI (SISTR), формат которого показан на рис. 5.84, и определить, какая часть SI RAM считается основной в текущий момент времени.

Значение бита CRORa определяет адреса ячеек основной памяти, которые выделены для работы с приемником RXa канала TDMa (табл. 5.49). Значение бита CROTa определяет адреса ячеек основной памяти, которые выделены для работы с передатчиком ТХа канала TDMa (табл. 5.49).

Значения битов CRORb и CROTb определяют адреса ячеек основной памяти, которые выделены для работы с приемником RXb и передатчиком ТХЬ канала TDMb (табл. 5.50). Значения этих битов имеют смысл, только если TSA настроен на работу с

двумя TDM-каналами.

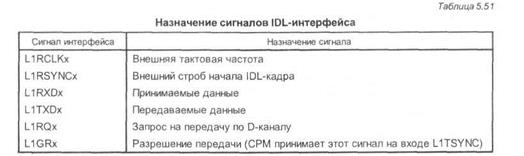

IDL-интерфейс. IDL интерфейс-полнодуплексный ISDN-интерфейс, предназначенный для подключения сетевых устройств к коммуникационному контроллеру. Для выхода на S/T-интерфейс требуется дополнительно на выводах контроллера подключать специальный S/T-трансивер, например, Motorola MC145474.

Контроллер МРС860 поддерживает все каналы IDL-протокола в режимах работы basic ISDN и primary ISDN. В режиме basic ISDN данные передаются по трем временным каналам (В1 и В2 - 8-битные информационные каналы, D - 2-битный канал управления) в виде 20-битного кадра со скоростью 160 Кбит/с.

Коммуникационные контроллеры могут работать только как пассивные (slave) ISDN-устройства, поэтому тактовая частота и сигнал строба начала кадра должны поступать от внешнего активного (master) устройства. Все контроллеры поддерживают полнодуплексный режим обмена и имеют независимые линии приема и передачи данных, но одни и те же сигналы тактовой частоты и строба кадра используются и для приемника, и для передатчика. СРМ может обрабатывать IDL-протокол одновременно на двух TDM-каналах, причем каждый канал может иметь свои сигналы синхронизации и стробирования. Назначение сигналов IDL-интерфейса приведено в табл. 5.51.

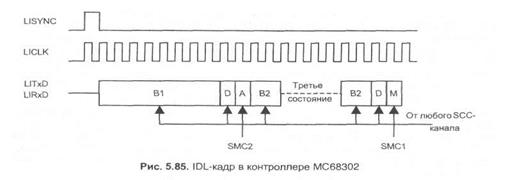

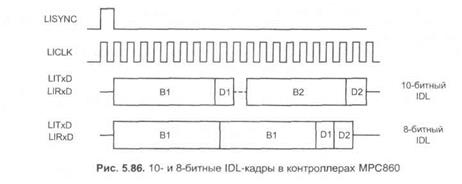

СРМ поддерживает две разновидности IDL-кадров: 8-битный и 10-битный. Разница заключается только в порядке передачи битов внутри кадра. Общая длина IDL-кадра постоянна и равна 20 битам. Функциональное назначение полей в обоих типах кадра совпадает. Ранние версии Motorola IDL-интерфейса, например в СР контроллера МС68302 (рис. 5.85), поддерживали дополнительно два однобитовых канала: (auxiliary) А-канал и (maintenance) М-канал, которые использовались для передачи информации о дополнительном управлении и контроле обмена между сетевыми устройствами. При желании пользователь может запрограммировать в СРМ TDM-каналы на передачу через эти битовые служебные каналы «прозрачной» информации от любого SCC или SMC-контроллера

.

.

Поскольку IDL-интерфейс поддерживает рекомендации CCITT 1.460, то каждый бит 20-битного IDL-кадра может быть запрограммирован пользователем в TDM как отдельный битовый временной канал со скоростью передачи данных 8 Кбит/с, предназначенный для работы со своим SCC- или SMC-контроллером. Работа с таким битовым каналом может сопровождаться выработкой специальных стробирующих сигналов (при приеме или передаче этого бита) для внешних устройств, которые не поддерживают ISDN-интерфейс. Таким образом, 20-битный IDL-кадр в контроллере МРС860 (рис. 5.86) может рассматриваться как объединение от 1 до 20 различных каналов, каждый из которых может обрабатываться своим SCC- или SMC-контроллером. Настройку на конкретный режим работы пользователь выполняет при программировании ячеек памяти маршрутизации SI RAM.

При передаче данных по D-каналу для определения коллизий коммуникационный контроллер использует метод запросов-подтверждений. Контроллер выставляет запрос L1RQx к устройству физического уровня модели OSI, например к S/T-трансиверу. Если D-канал свободен, то устройство выставляет ответный активный сигнал подтверждения L1 GRx. Контроллер проверяет наличие сигнала L1 GRx в течение действия импульса строба LIRSYNCx. Если обнаружен активный сигнал подтверждения, то контроллер выставляет на D-канал первый бит кадра данных. Если во время передачи по D-каналу сигнал L1GRx будет сброшен в пассивное состояние, то контроллер остановит передачу и начнет повторную передачу, когда сигнал L1GRx станет активным.

СРМ-контроллер также поддерживает режим работы с primary IDL-протоколом. В этом режиме IDL-кадр может состоять из четырех восьмибитных временных каналов данных.

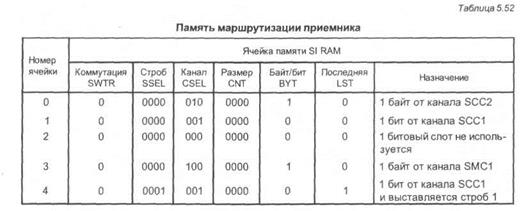

При программировании памяти маршрутизации SI RAM пользователь может запрограммировать прием более чем одного временного канала на один высокоскоростной SCC-контроллер, а также может обеспечить выработку внешних стробирующих сигналов при передаче/приеме каждого временного канала. На практике возможна реализация 32 виртуальных каналов (четыре канала в IDL-кадре по 8 бит), каждый из которых имеет размер 1 бит, представляет собой независимый В-канал и адресован своему SCC-контроп-леру. Такое применение 32 виртуальных каналов реализовано в контроллере МРС860МН. Рассмотрим пример программирования таблицы маршрутизации для реализации basic IDL-интерфейса с 10-битным форматом кадра, состоящим из трех каналов. Канал В1 обслуживается контроллером SCC2, канал В2 - контроллером SMC1, канал D - контроллером SCC1. В табл. 5.52 приведено заполнение ячеек SI RAM, которое необходимо повторить и для секции памяти приема и для секции памяти передачи. Во все оставшиеся ячейки записывается код 0x0001. При этом в каждой из ячеек будет установлен бит последней ячейки LST, и эти ячейки будут выключены из работы.

|

РСМ-интерфейс. В режиме импульсной модуляции PCM (Pulse Code Modulation) несколько SCC-каналов объединяются в режиме временного мультиплексирования. Стандарт РСМ поддерживает такие хорошо известные интерфейсы, как Т1 и СЕРТ.

Внешняя частота синхронизации поступает на вход L1CLK для тактирования как приемника, так и передатчика. Если необходимо использовать разные частоты синхронизации приемника и передатчика, то рекомендуется запрограммировать немультиплексиру-емый NMSI-режим работы канала вместо РСМ-режима.

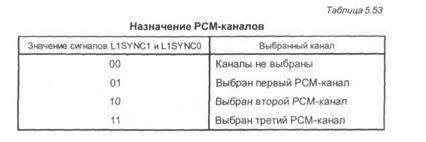

Для выделения временных каналов в СРМ используются два стробирующих сигнала -L1SYNC0 и L1SYNC1. Комбинация этих сигналов определяет выбор одного из трех РСМ-каналов (табл. 5.53).

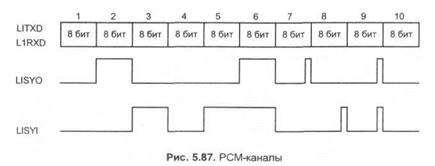

Эти стробирующие сигналы могут удерживаться или в течение передачи всех данных канала или стробировать появление первого бита данных канала. В случае стробирова-ния первого бита стробирующий сигнал представляет собой импульс шириной один битовый интервал, по отрицательному фронту которого выставляется первый бит данных. На линиях в интерфейсе Т1/СЕРТ используется удержание стробирующих сигналов в течение передачи всех данных РСМ-канала. На рис. 5.87 приведен пример различных способов стробирования РСМ-каналов.

После выбора SCC-канала, работающего с данным РСМ-каналом, данные от него будут передаваться по линии L1TXD и приниматься с линии L1RXD, но только пока идет передача тактирующих импульсов по линии L1CLK. Если на линии L1CLK нет передачи тактовых импульсов, то линия L1TXD находится в Z-состоянии, а сигналы на линии L1RXD игнорируются.

Можно настроить режим, когда каждый РСМ-канал управляется отдельным SCC-koh-троллером или когда все РСМ-каналы запрограммированы для работы с одним SCC-контроллером, который будет в одиночку обрабатывать высокоскоростной поток данных. В этом режиме рекомендуется остальные каналы ввода/вывода перевести в выключенное состояние, так как при увеличении числа одновременно работающих каналов уменьшается максимальная скорость передачи информации. При увеличении числа работающих каналов усложняется процесс арбитража доступа к шине для передач от SDMA-каналов и увеличивается время ожидания доступа к шине для передачи данных между FIFO и памятью. Максимальная скорость передачи канала контроллера достигается, когда работает только один канал ввода/вывода.

При работе с РСМ-интерфейсом можно дополнительно использовать выработку сигналов  для каждого РСМ-канала. Эти сигналы выставляются, когда SCC-контроллер желает передать данные по РСМ-каналу и удерживаются в течение передачи всех данных от этого контроллера, даже если эта передача требует занятия нескольких временных слотов. На рис. 5.87 приведен пример использования нескольких РСМ-каналов, причем второй канал занимает два временных слота.

для каждого РСМ-канала. Эти сигналы выставляются, когда SCC-контроллер желает передать данные по РСМ-каналу и удерживаются в течение передачи всех данных от этого контроллера, даже если эта передача требует занятия нескольких временных слотов. На рис. 5.87 приведен пример использования нескольких РСМ-каналов, причем второй канал занимает два временных слота.

GCI-интерфейс. Основные режимы работы GCI-интерфейса, GCI (General Circuit Interface) -4-проводной интерфейс для подключения устройств к ISDN-сети. Интерфейс может работать в режиме передачи данных и в режиме контроля (maintenance) функционирования сетевых устройств. Контроллер может работать как NT(Network Terminal)- или TE(Terminal Equipment)-ycTponcTBO в сети ISDN. При работе в NT-режиме станция может быть или master- или slave-устройством. При работе в ТЕ-режиме станция может быть только slave-устройством.

Интерфейс использует четыре сигнала: прием, передача, единый тактовый сигнал для приема и передачи и сигнал строба начала обмена данными. Передний фронт строб-

сигнала говорит о начале кадра и сбрасывает счетчики контроля длины кадра, В режиме slave тактовый сигнал и строб являются внешними сигналами по отношению к контроллеру.

Тактовая частота должна быть в два раза больше частоты передачи данных. Данные выставляются по положительному перепаду тактового сигнала и читаются через 1-1,5 периода после начала битового интервала.

Интерфейс позволяет работать в сетях с конфигурациями point-to-point и multipoint. Входные данные поступают от БЯ-передатчика. Выходные данные передаются на внешний контакт с открытым коллектором и с внешним pull-up-сопротивлением, такой способ подключения реализован для объединения в шину «монтажное ИЛИ» с выходами других GCI-устройств. Данные передаются S/T-передатчику в определенные временные слоты, в другое время линия находится в Z-состоянии.

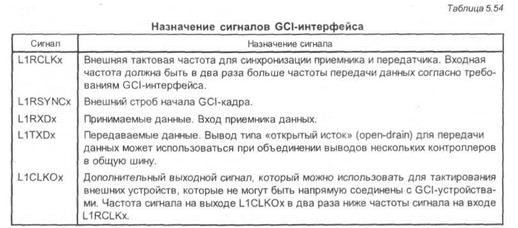

В СРМ каждый TDM-канал поддерживает независимые GCI-интерфейсы с независимыми приемной и передающей частями. В табл. 5.54 приведен набор сигналов GCI-ин-терфейса, которые используют коммуникационные контроллеры для обмена информацией с внешними S/T-трансиверами.

GCI-интерфейс может быть настроен на работу в двух режимах: нормальном рабочем GCI-режиме и в режиме SCIT (Special Circuit Interface for Terminal). Режим SCIT настраивается при программировании регистра SIMODE.

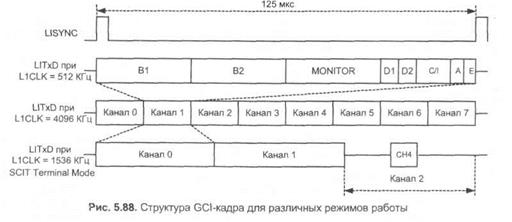

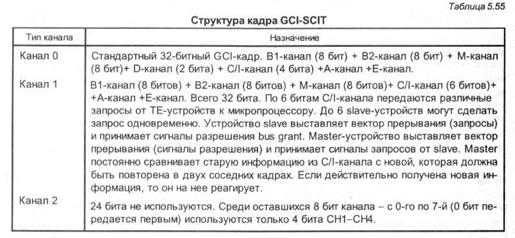

Структура GCI-кадра. Каждый GCI-канал представляет собой 4-байтовую структуру, использующую режим временного мультиплексирования (рис. 5.88). Сигнал начала кадра выставляется с частотой 8 КГц, т. е. один раз в 125 мкс. Два независимых В-канала с пропускной способностью 64 Кбит/с используются для передачи цифровых данных и голоса. М-канал используется для настройки и управления передачей. C/l-канал делится на 2-битовый D-канал, 4 бита C/Ι-канала (Control/Indication) и 2 бита для А- и Е-каналов, которые предназначены для контроля за передачей информации по М-каналу.

При работе в режиме SCIT СРМ поддерживает механизм определения коллизий при передаче по D-каналу. Управление доступом к D-каналу в устройствах S/T-интерфейса реализуется с помощью канала команд C/l (Command/Indicator). Внешние сетевые устройства, работающие на физическом уровне модели OSI (например, трансивер), определяют активность D-канала и уведомляют об этом СРМ обычно через бит 4 второго канала C/I. Этот бит СН4 выполняет функции сигнала SG (stop/go).Если этот бит равен 0, то

канал занят или произошла коллизия. В этом случае СРМ прекращает передачу и возобновляет ее только после сброса этого бита. Обычно повторная передача прерванной информации выполняется автоматически для двух первых буферов данных кадра.

Каналы 0 и 2 предназначены для обмена данными между устройствами.

Обычно GCi-кадр содержит комбинацию 32 битовых временных каналов, передаваемых со скоростью 8 КГц, что составляет суммарную скорость передачи кадра в 256 Кбит/с.

Но в устройствах NT1 и NT2 до 8 GCI-каналов могут быть объединены в один кадр с пропускной способностью от 256 до 3088 Кбит/с. При этом для всего объединенного кадра используется строб-сигнал с частотой 8 КГц, как и для GCI-кадра с одним каналом. Таким образом, во временной интервал 125 мкс, заданный строб-сигналом, можно вложить от 1 до 8 отдельных GCI-каналов, которые образуют единый кадр. Каждый отдельный GCI-

канал в таком кадре имеет номер от 0 до 7, соответствующий временному слоту, в который он вставлен. Скорость передачи данных внутри каждого GCI-канала составляет 256 Кбит/с. В режиме SCIT кадр данных объединяет три GCI-канала. В этом случае скорость передачи данных в кадре составляет 2048 Кбит/с.

При доступе к каналу GCI-SCIT-кадра (Special Circuit Interface for Terminal) до 8 HDLC-контроллеров могут быть объединены для передачи по D- и C/l-каналам. Механизм доступа к каналу позволяет исключить потерю данных. Перед началом передачи GCI-koh-троллер проверяет состояние СН4 - 4 бита третьего GCI-канала (канал номер 2). Этот бит показывает состояние C/I- и D-каналов. Если бит равен 1, то канал свободен, если бит равен 0, то канал занят. Если канал свободен, то HDLC-контроллер начинает передавать на биты СН1-СНЗ третьего канала GCI свои разряды адреса AD2-AD0 и тут же их читает. Если при чтении обнаружено несовпадение адресов, то процедура доступа к каналу прекращается. Если выставленный адрес совпал с прочитанным, то контроллер получает доступ к каналу и передает бит СН4 = 0. HDLC-контроллер с наименьшим адресом имеет самый высокий приоритет доступа к каналу. Структура GCI-SCIT-кадра приведена в табл. 5.55.

Рассмотрим пример программирования таблицы маршрутизации для реализации basic 2B+D GCI-интерфейса для 96-битного кадра, состоящего из объединения трех каналов GCI по 32 бита каждый. Канал В1 обслуживается контроллером SCC2, канал В2 - контроллером SCC4, канал D- контроллером SCC1. Контроллер SMC1 передает управление по C/l-каналу. Включена поддержка механизма обнаружения коллизий при доступе к D-каналу, которая реализуется в 4 бите C/l-канала на втором SCIT GCI-канале.

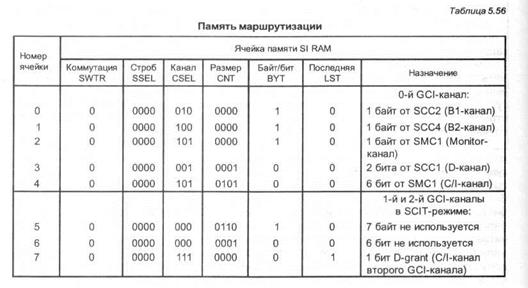

В табл. 5.56 приведено заполнение ячеек SI RAM, которое необходимо повторить и для секции памяти приема и для секции памяти передачи. Во все оставшиеся ячейки записывается код 0x0001. При этом в каждой из ячеек будет установлен бит последней ячейки LST, и эти ячейки будут выключены из работы.

|

|

М- и А/Е-каналы. Канал Monitor (М-канал) - независимый канал, который служит для передачи команд и управляющей информации между схемами 1-го уровня управления в сетевых устройствах. Через М-канал происходит обмен содержимым и конфигурирование внутренних регистров GCI-устройств, например, S/T-передатчика. А- и Е-каналы предназначены для контроля передачи информации по М-каналу (flow control) с использованием режима подтверждений. Для А- и Е-битов активное состояние - «0», а пассивное

состояние канала - Z-состояние. MSB-байт передается по М-каналу первым. Если по каналу нет передачи, то во время данного временного слота выводы контроллера находятся в Z-состоянии.

Все сообщения М-канала имеют длину 2 байта. При записи информации в регистры GCI-устройства в первом байте передается адрес регистра. Для некоторых микросхем бит АО = 0 определяет цикл записи содержимого второго байта в регистр с указанным адресом. Если АО = 1, то это означает цикл чтения с возвратом, и значение второго байта игнорируется и GCI-устройство должно послать сообщение-ответ, в котором передает содержимое регистра с указанным адресом.

Каждый байт посылается (дублируется), по крайней мере, в двух соседних кадрах для обеспечения надежности передачи, при этом приемник проверяет совпадение и целостность информации. Биты А и Е в GCI-канале используются для контроля и подтверждений передачи между GCI-устройствами по М-каналу. Когда по М-каналу нет передачи, биты А и Е находятся в неактивном состоянии (Z-состоянии). Бит Е устанавливается передатчиком, чтобы указать, что он передает байт. Бит А используется приемником для подтверждения приема байта. Второй байт команды передается только после получения

подтверждения на первый байт.

Передача по М-каналу начнется только после получения неактивного бита А = Z в течение двух последовательных GCI-кадров. Передача начинается с установки GCI-устройством бита Е в активное состояние (Е = 0) и посылкой этого бита в том же кадре, в котором передается первый байт данных. Передача этого байта повторяется, по крайней мере, в двух соседних GCI-кадрах, пока не будет получено подтверждение. После получения двух одинаковых байтов приемник подтверждает прием байта, установив бит А в активное состояние и удерживая его активным, по крайней мере, в течение следующего кадра. Если совпадение не обнаружено, то устанавливается активный бит А только для одного кадра.

Поскольку пока ожидается подтверждение на первый байт,посылающее устройствоустанавливает бит Е в неактивное Z-состояние и передает первый кадр второго байта. Затем второй байт повторяется, но уже с активным битом Е = 0, до тех пор пока не будет получено подтверждение.

Успешная передача следующего байта подтверждается принимающим устройством установкой и передачей неактивного значения А = Z во время приема первой копии следующего байта данных и передачей активного значения А = 0, когда будет получена вторая копия байта. При совпадении двух байтов приемник в течение двух соседних кадров вначале устанавливает бит А в неактивное состояние (предустановка подтверждения), а затем снова в активное состояние (подтверждение). Если совпадения не произошло, то бит А остается неактивным в течение двух соседних кадров, тем самым показывая запрос на прерывание. Передатчик после получения запроса на прерывание будет повторно передавать все последние сообщения, пока не получит правильного подтверждения.

Бит Е может быть неактивным только для одного кадра. Конец сообщения отмечается установкой бита Е = Z при передаче обеих копий последнего байта сообщения. Если бит Е неактивен более двух кадров, то это означает конец сообщения.

Передача кода IDLE (OxFF) по М-каналу отмечается тем, что биты А и Е будут неактивны (в Z-состоянии) в течение двух последовательных GCI-кадров.

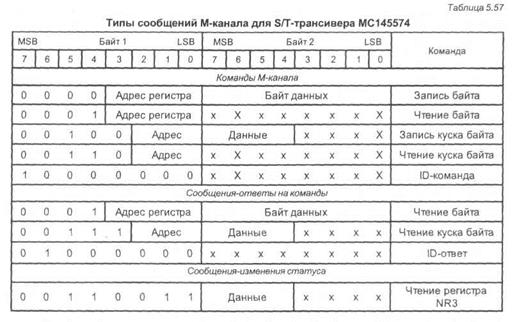

Сообщения М-канала. Используются три типа сообщений. Первая группа сообщений и команд -для чтения и записи внутренних регистров GCI-устройства. Это команды, которые записывают данные во внутренние регистры, принимаются и выполняются, но сообщение-ответ не передается. GCI-устройство подтверждает все принятые по М-каналу команды (табл. 5.57). Если принята некорректная команда, то она не выполняется, но подтверждение посылается.

Вторая группа -ответы от GCI-устройства, которые передаются после получения по М-каналу команды чтения или записи. Сообщения-ответы передаются по М-каналу в ответ на команду чтения регистра.

Третья группа сообщений - сообщения индикации состояния. Эти сообщения отражают изменение статуса регистров устройства. Сообщения изменения статуса автоматически передаются в GCI Monitor-канал GCI-устройством, когда изменение статуса обнаруживается внутри устройства. Эти сообщения –аналог сигнала Interrupt. Сообщения Status Indication должны вызывать чтение регистра состояния прерываний (interrupt status).

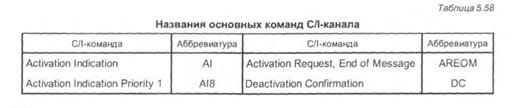

Управление передачей по С/Ι-каналу. Канал С/Ι (Command/Indication) служит для передачи процедур управления 1-го уровня, таких как активация и деактивация линии, петлевой контроль и другие контрольные функции. C/l-коды имеют длину 4 бита и должны быть получены приемником в двух последовательных кадрах, прежде чем команда будет выполнена. Биты команды нумеруются от 4-го до 1-го, и старший (MSB) 4-й бит передается в канал первым.

Для любого канала 4-битное слово команды передается последовательно в GCI-ка-нал кадра, пока не будет заменено другой командой C/l-канала. Поэтому при приеме новой команды приемник сравнивает ее код с кодом предыдущей команды и приступает к выполнению полученной команды, только если ее код отличается от кода предыдущей команды. Для каждой микросхемы может быть определен свой набор регистров и команд для C/l-управления (табл. 5.58).

Процедуры активации и деактивации S/T трансивера. В состоянии деактивации тактовые сигналы CLK между контроллером и внешним сетевым устройством не передаются, а линии данных находятся в состоянии логической «1». Сетевые устройства активируют работу сетевого контроллера, начиная передавать на его входы тактовые сигналы CLK, и с помощью команд индикации на канале 0 C/І -канала. СРМ выставляет немаскируемое прерывание, извещая центральный процессор о том, что в буфере SMC-koh-троллера находится код «индикации».

При активации линий центральный процессор выставляет на линии передачи данных LITXDx код «0» (при программировании используется бит STZx = 1 в регистре конфигурации последовательного интерфейса SIMODE) и передает сетевому устройству код команды «Timing TIM» (код «0») по 0-му каналу C/I временного канала до тех пор, пока не будет сброшен бит STZx. Этот бит сбрасывает центральный процессор, когда необходимо разрешить передачу данных. Код «0» на нулевом канале C/I сообщает внешнему сетевому устройству о процессе активации коммуникационного контроллера.

Обычно C/І-канал используется для контроля процедур активации/деактивации. Стандартные процедуры активации/деактивации выполняются при помощи команд AR, DR и AI. Команда DI обычно передается по сети перед выключением питания. Класс сообщения выделяется C/І -командами AR8 и AR10. Команда AREOM может быть использована для завершения передачи сообщения на D-канале.

Если нет активных S/T-трансиверов, то тактовый сигнал TCLK между S/T-трансиве-ром и контроллером не вырабатывается. Первый передатчик, который будет активирован, начнет выдавать TCLK-сигнал. В контроллере QUICC для формирования тактового сигнала может быть использован внутренний BRG-генератор с соответствующими коэффициентами деления, чтобы получить частоту 2,048 МГц.

Кадр S/T содержит 48 бит. При передаче от NT к ТЕ-станциям один из битов, А-бит, используется для контроля. Бит А = 1, когда SU loop работает в активном рабочем режиме и бит А = 0 в другое время.

Активация режима S/TLoop от NT-станции. NT-станция активирует режим S/T Loop, передавая к ТЕ-станции в кадре команду AR. ТЕ станция, получив кадр, синхронизируется этим сигналом, начинает выдавать своему контроллеру TCLK сигнал и передает подтверждение о начале активации в виде кадра с командой AI. Далее, получив от ТЕ-станции этот кадр, NT-станция отвечает кадром с командой AI, тем самым активизируя цикл обмена (loop).

Активация режима S/T Loop от ТЕ-станции. ТЕ-станция запускает свой тактовый генератор TCLK сигнала и активирует этот режим, передавая кадр с командой AR8/AR10 к NT-станции. NT-станция, получив кадр, начинает выдавать своему контроллеру TCLK-сигнал и передает в ответ подтверждение в виде кадра с командой AR и битом А = 0.

ТЕ-станция, приняв ответный кадр от NT и убедившись, что это кадр с командой AR, прекращает передачу предыдущего кадра, дублирует содержимое принятого кадра в кадр с командой AI и возвращает его NT-станции, тем самым активизируя цикл (loop). NT-станция подтверждает активацию канала, передав ТЕ-станции кадр с командой AI8/AI10 и битом А = 1.

Деактивация. Стандарты CCITT I.430 и ANSI T1.605 определяют, что только NT-станция может провести процедуру деактивации режима S/T loop посылкой кадра с командой DR к ТЕ-станциям, которые подтверждают получение кадра и начало деактивации, передавая в ответ кадр с командой DI и выключая свой генератор TCLK-сигнала. Получив подтверждение, NT-станция завершает процедуру деактивации, передав ТЕ-станции коианду DC.