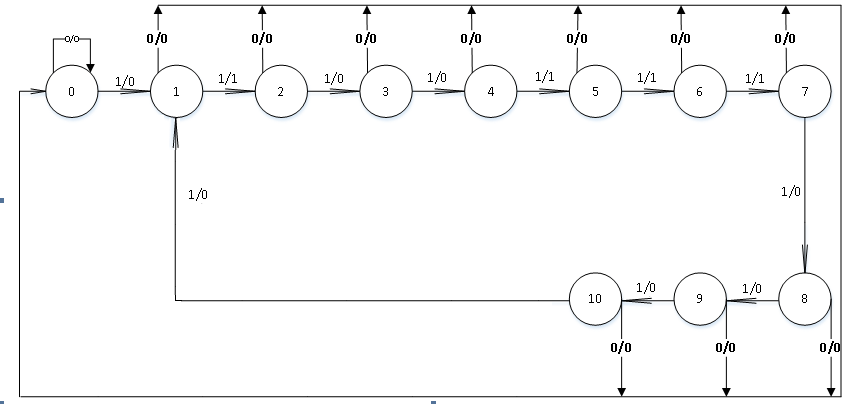

Граф переходов состояний конечного автомата

Пояснительная записка о выполнении курсового проекта

по дисциплине "Микропроцессорные устройства"

"Проектирование безопасной микропроцессорной системы"

Выполнили студент гр. АТС-401У

Дмитриев А.В

Санкт-Петербург, 2016 год.

Оглавление

1. Цель проекта. 3

2. Сведения о конечных автоматах. 3

3. Описание метода программной реализации. 3

4. Структурная схема проектируемого конечного автомата. 3

5. Граф переходов состояний конечного автомата. 4

6. Таблица переходов и выходов конечного автомата. 4

7. Кодированная таблица переходов и выходов автомата. 5

8. Карты Карно для проектируемого автомата. 5

9. Полученные функции алгебры логики. 6

10. Полученные функции алгебры логики на языке программирования С++ Builder 7

11. Блок - схема алгоритма приложения в целом.. 8

12. Блок-схема алгоритма Timer1Timer 9

13. Краткое описание используемых объектов. 10

14. Краткое описание этапов разработки проекта. 10

16. Структурная схема безопасной реализации конечного автомата. 11

17. Расчет периода диагностирования безопасной реализации микропроцессорной системы.. 11

18. Выводы.. 12

Цель проекта

Проектирование безопасной микропроцессорной системы, которая должна генерировать определенные по задания проекта сигналы.

Сведения о конечных автоматах

Конечными автоматами называются дискретные устройства с памятью, имеющие конечное число состояний. В конечных автоматах выходной сигнал определяется не только значениями сигналов на входах в данный момент времени, но и его внутренним состоянием. Внутреннее состояние автомата определяется состоянием его элементов памяти. Существует несколько способов задания конечных автоматов: по графам переходов состояний, по таблицам переходов и выходов, по булевым функциям и задание на языке регулярных выражений.

Описание метода программной реализации

В проекте для реализации конечного автомата используется метод непосредственного вычисления булевых функций. Основная идея состоит в том, что заданную формулу надо записать, используя логические операции языка С++ Builder. Блоки программы вычисляют отдельные части логической формулы в соответствии с законами алгебры логики. Каждая переменная представлена значениями 0 и 1. Для каждой переменной отводится один байт, то есть одна ячейка памяти, имеющая восемь разрядов, из которых используется только один. Состояние других - безразлично.

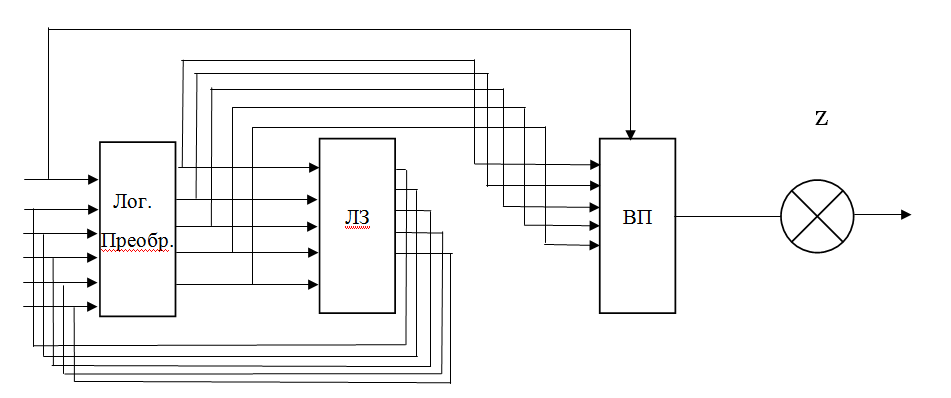

Структурная схема проектируемого конечного автомата

рис. 1 - Структурная схема автомата Мили II рода

Граф переходов состояний конечного автомата

рис. 2 - Граф переходов состояний автомата

Таблица переходов и выходов конечного автомата

Таблица 1. Таблица переходов и выходов

| S | X=0 | X=1 |

| 0,0 | 1,0 | |

| 0,0 | 2,1 | |

| 0,0 | 3,0 | |

| 0,0 | 4,0 | |

| 0,0 | 5,1 | |

| 0,0 | 6,1 | |

| 0,0 | 7,1 | |

| 0,0 | 8,0 | |

| 0,0 | 9,0 | |

| 0,0 | 10,0 | |

| 0,0 | 1,0 |

Кодированная таблица переходов и выходов автомата

Таблица 2. Совмещенная кодированная таблица переходов и выходов

| S | Y4 | Y3 | Y2 | Y1 | X=0 | X=1 |

| 0000,0 | 0001,0 | |||||

| 0000,0 | 0010,1 | |||||

| 0000,0 | 0011,0 | |||||

| 0000,0 | 0100,0 | |||||

| 0000,0 | 0101,1 | |||||

| 0000,0 | 0110,1 | |||||

| 0000,0 | 0111,1 | |||||

| 0000,0 | 1000,0 | |||||

| 0000,0 | 1001,0 | |||||

| 0000,0 | 1010,0 | |||||

| 0000,0 | 0001,0 | |||||

| ~ | ~ | |||||

| ~ | ~ | |||||

| ~ | ~ | |||||

| ~ | ~ | |||||

| ~ | ~ |