Аналоговые программируемые микросхемы

ОБЩИЕ СВЕДЕНИЯ

Более половины всех электронных проектов связаны с применением аналоговой или аналого-цифровой схемотехники. Поэтому естественно, что в области разработки БИС/ СБИС с программируемой структурой этому направлению также уделяется необходимое внимание.

Аналоговые и аналого-цифровые фрагменты уже давно встраиваются в БИС/СБИС микроконтроллеров, технология БМК также нашла применение в этой области. В последние годы интерес фирм-разработчиков вызывают аналоговые и аналого-цифровые БИС/ СБИС с программируемой структурой. Наличие микросхем, структура которых конфигурируется из аналоговых блоков с программируемыми параметрами, позволяет создавать устройства для решения многих задач обработки аналоговых сигналов. Такие задачи характерны для систем управления техническими объектами различного назначения, получающими информацию отдатчиков физических величин той или иной природы (температуры, давления и т. п.) в виде электрических сигналов. В подобных системах нужны как аналого-цифровые преобразователи (АЦП) для оцифровки выходных сигналов датчиков, так и средства коммутации аналоговых сигналов, их предварительной фильтрации, суммирования или вычитания, нормализации, интегрирования и т. д. Подобные задачи решаются средствами, для которых иногда используется термин «Front-End Design». На основе микросхем с программируемыми структурами возможно быстрое проектирование подсистем аналоговой и аналого-цифровой обработки сигналов, их отладка, создание промышленных образцов и быстрый выход на рынок.

Впервые о создании БИС с массивом программируемых пользователем аналоговых элементов объявила фирма «Motorola» (1997 г.). Эти БИС были анонсированы под названием МРАА020 (Motorola Field Programmable Analog Arrays), но не доведены до промышленного выпуска. Тем не менее анализ организации и возможностей этих БИС представляет интерес, поскольку проявляется преемственность в вопросах реализации между этими БИС и последующими разработками. В 1999 г. фирма «Lattice Semiconductor» выпустила семейство внутрисхемно программируемых (In-System Programmable) аналоговых схем типа ispPACIO и ispPAC20.

В микросхемах фирмы «Motorola» для построения операционных звеньев используется схемотехника с переключаемыми конденсаторами, в микросхемах фирмы «Lattice Semiconductor» - традиционные решения с применением точных масштабирующих резисторов.

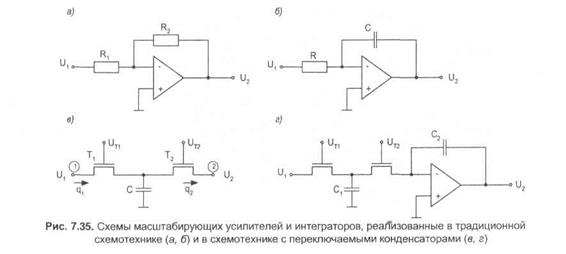

В цифровой технике сигналы принимают лишь два значения, одно из которых соответствует логической единице, другое - логическому нулю. Проблема точного задания этих сигналов отсутствует - требуется лишь надежно отличать один из этих сигналов от другого. Совершенно иным является положение в аналоговой технике, где сигнал должен передавать точное значение величины с погрешностью в десятые или сотые доли процента, т. е. требуется «дозирование» сигналов с разрешающей способностью в тысячи или даже более уровней. Традиционно (до конца 1970-х- начала 1980-х гг.) роль дозирующих параметров играли в первую очередь сопротивления точных резисторов. Так, например, в известной схеме масштабирующего усилителя, т. е. устройства умножения сигнала, заданного напряжением постоянного тока, на константу (рис. 7.35, а) используются два точных резистора, от соотношения сопротивлений которых зависит функциональная характеристика схемы, в идеализированном виде имеющая вид U2 = (- R2/R1 )U1. Интегратор (рис. 7.35, б) имеет идеализированную функциональную характеристику вида U2 = (-1/ RC)INT U1(t)dt, в которых роль масштабирующего коэффициента играет произведение сопротивления точного резистора на емкость конденсатора цепи обратной связи.

В схемотехнике с дискретными схемными элементами проблема реализации точных резисторов нашла удовлетворительное решение. Для технологии интегральных схем эта проблема намного сложнее, но существует альтернативное схемное решение, благодаря которому резисторы имитируются цепями, содержащими коммутируемые (переключаемые) конденсаторы (рис. 7.35, в). В такие цепи входят конденсатор С и ключевые транзисторы Т1 и Т2, управляемые тактирующими напряжениями UT1 и UT2. Транзисторы Т1 и Т2 под воздействием тактирующих напряжений замыкаются поочередно, и конденсатор С попеременно заряжается через замкнутый ключевой транзистор до напряжения U1 или U2. В момент замыкания ключевого транзистора заряд конденсатора изменяется на величину q = q1 = q2 = C(U1 - U2).Изменение заряда осуществляется короткими импульсами тока, протекающими через конденсатор при замыкании соответствующего ключевого транзистора.

Среднее значение тока в цепи между точками 1 и 2 составляет величину i= q/T = = (U1-U2)C/T, где Т - период тактирующих импульсов.

Из полученного выражения видно, что в определенном смысле, для средних значений сигналов цепь ведет себя как резистор с сопротивлением R=T/C.

На основе схем с переключаемыми конденсаторами можно строить разнообразные операционные звенья, аналогичные известным из традиционной аналоговой схемотехники, путем замены резисторов эквивалентными им цепями. Сопротивления эквивалентных цепочек управляются значениями тактовой частоты f = 1/T. В схемотехнике с переключаемыми конденсаторами строятся схемы, масштабные коэффициенты функциональных характеристик которых зависят от отношения емкостей, которое может задаваться с высокой точностью. Параметры емкостей мало критичны к изменению температуры и старению. Резко (в сотни раз) снижается площадь, занимаемая цепями с переключаемыми конденсаторами в сравнении с цепями, содержащими точные резисторы.

Схема интегратора с переключаемыми конденсаторами, основного элемента для многих операционных звеньев, показана на рис. 7.35, г. Ее функциональная характеристика в терминах теории импульсных цепей с использованием Z-преобразования имеет вид H(Z) =

= (-C1/C2)(Z –1/1-Z –1),где Н(Z)-функция передачи интегратора, Z-оператор дискретного преобразования Лапласа.

ПРАКТИЧЕСКИЕ РАЗРАБОТКИ

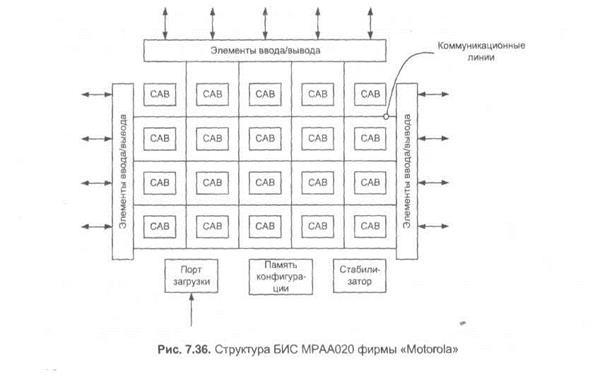

БИС МРАА020 фирмы «Motorola» (рис. 7.36) - набор конфигурируемых аналоговых блоков CAB (Configurable Analog Blocks), соединяемых между собой и подключаемых к элементам ввода/вывода ключевыми КМОП-элементами. Конфигурации CAB и состояния переключателей определяются содержимым памяти типа SRAM.

БИС реализованы в корпусе с 160 контактами и содержат 20 CAB в матрице 4x5. Каждый CAB (рис. 7.37) содержит один операционный усилитель ОУ, пять регулируемых конденсаторов, компаратор, набор переключателей и управляющую логику.

Для разработок проектов с использованием БИС типа МРАА фирма «Motorola» создала специальные средства: библиотеку макрофункций, САПР для проектирования конфигурации БИС, кабели для загрузки данных конфигурации из компьютеров и прототипные платы (Evaluation Boards) для верификации проектных решений.

Каждая макрофункция библиотеки соответствует решению определенной задачи и позволяет задать функциональную характеристику проектируемого блока не путем вычисления требуемых параметров схемы, а путем задания функциональных характеристик узла (частоты генератора, коэффициента усиления усилителя, полосы пропускания для фильтра и т. д.).

В качестве САПР разработан программный пакет EasyAnalogDesign-Software, ориентированный на работу в PC-совместимых компьютерах в ОС Windows 95/NT. Работа проектировщика с проектом организована в форме интерактивного общения. Проектировщик задает типы макрофункций, расположенных в выбранных местах матрицы, и требуемые свойства узлов. Далее пакет позволяет организовать соединения между схемными элементами и их связи с выходными блоками, контролируя и блокируя при этом недопустимые типы соединений. После завершения формирования проекта пакет позволяет загрузить данные конфигурации БИС соединением при помощи специального загрузочного кабеля выхода последовательного порта компьютера с БИС МРАА020.

Прототипная плата Evaluation Board помимо БИС РАА020 содержит цепи, поддерживающие функционирование БИС, и различные органы пользовательского управления, что обеспечивает легкость и скорость верификации созданных проектов.

К реализуемым на одном CAB функциональным узлам относятся усилительные каскады с заданным коэффициентом усиления, сумматоры, вычитатели, сглаживающие каскады, цепи выборки и хранения аналоговых сигналов, фильтры первого порядка. Более сложные функ

.

циональные узлы, такие как биквадратные и полосовые фильтры, детекторы уровней и др. могут быть образованы с помощью соединения нескольких CAB в требуемую структуру.

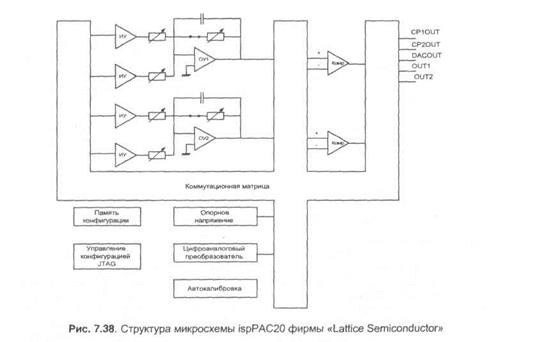

Микросхемы семейства ispPAC фирмы «Lattice Semiconductor» имеют ряд отличий от микросхем фирмы «Motorola». В них не используется техника переключаемых конденсаторов, они архитектурно проще (имеют меньше конфигурируемых ресурсов), имеют меньшие габаритные размеры и число контактов ввода/вывода. Память конфигурации реализована по технологии EEPROM и может загружаться через специально выделенные контакты JTAG интерфейса. Конфигурация может быть закрыта от несанкционированного доступа битом секретности. Отличием является и включение в состав конфигурируемых ресурсов не только аналоговых, но и цифроаналоговых средств (схема ispPAC20 имеет встроенный 8-разрядный цифроаналоговый преобразователь). Заметим при этом, что цифроаналоговые и аналого-цифровые блоки имеют, как правило, жесткую внутреннюю структуру, не позволяющую произвольно их перестраивать. Например, ясно, что из двух 8-разрядных ЦАП или АЦП непосредственным образом не составить 16-разрядные ЦАП и АЦП, поскольку точностные требования к параметрам таких блоков резко различаются. Также не имеет смысла разбивать 16-разрядные ЦАП и АЦП на 8-разрядные, поскольку при реализации 8-разрядных преобразователей не нужны такие жесткие точностные требования, как это необходимо для 16-разрядных.

Структура ИС ispPAC20 (рис. 7.38) имеет в основе два программируемых усилительных блока (РАСЫоск) с дифференциальными входными усилителями, имеющими и дифференциальный выход, что позволяет изменять знак и численное значение коэффициента усиления в пределах от 1 до 10 целочисленными приращениями. Конденсаторы цепей обратных связей могут программироваться на величины от 1 до 63 пФ (всего 128 возможных значений) и позволяют строить на основе усилительных ступеней активные фильтры. Возможны конфигурации интеграторов. Как видно из рисунка, один РАС-блок имеет на входе двухвходовый коммутатор, а другой - внешнее управление инвертированием. Помимо РАС-блоков в БИС включены два аналоговых компаратора, коммутационные линии, 8-разрядный ЦАП, память конфигурации и средства ее загрузки (JTAG контроллер).

Схема ispPACIO отличается от уже рассмотренной наличием только четырех программируемых РАС-блоков.

Точностные возможности макроячеек микросхем ispPAC достаточно далеки от предельных для аналоговой техники, но могут считаться удовлетворительными для немалого числа практически реализуемых устройств. Общее представление об этих точностных возможностях дают следующие цифры. Приведенный ко входу температурный дрейф макроячейки составляет 50 мкВ/град., диапазон изменения выходного напряжения на отдельном выходе микросхемы 3-4 В при сопротивлении нагрузки между дифференциальными выходами 300 Ом. Для выходных напряжений АЦП достижимо полное использование напряжения питания 5 В, при этом значение единицы младшего разряда 1,25 мВ. Эксплуатационный диапазон температур микросхемы - от -40 до +85 °С. Если алгоритм работы конкретного устройства допускает наличие пауз в процессе его функционирования, то можно проводить периодическую автокалибровку характеристик блоков, длительность которой 100 мс. Автокалибровка гарантирует дифференциальное напряжение смещения нуля в 1 мВ.

Типовые значения коэффициента гармоник для дифференциального выхода при единичном усилении -88 дб на 10 кГц и -67 дб на 100 кГц, а при коэффициенте усиления 10 соответственно -72 дб и -61 дб.

Максимальная погрешность установки коэффициента усиления макроячейки составляет 4 %.

Погрешность установки частоты полюса в схеме активного фильтра не более 5 %. Время установления выходного напряжения ЦАП с погрешностью в 0,1 % - не более 6 мкс, дифференциальная нелинейность ЦАП - не более значения единицы младшего разряда. Типовое время переключения компаратора при напряжении перепада 10 мВ составляет 750 не.

Типовой входной ток макроячейки - 3 пА, максимальные токи потребления микросхем - приблизительно 20 мА.

Число циклов стирания-перепрограммирования - не менее 10 000.

Программное обеспечение фирмы «Lattice Semiconductor» под названием РАС-Designer ориентировано на использование в PC-совместимых компьютерах с ОС Windows. САПР позволяет вводить информацию о проекте, моделировать функционирование схем, компилировать проекты и загружать результаты компиляции в память конфигурации БИС.