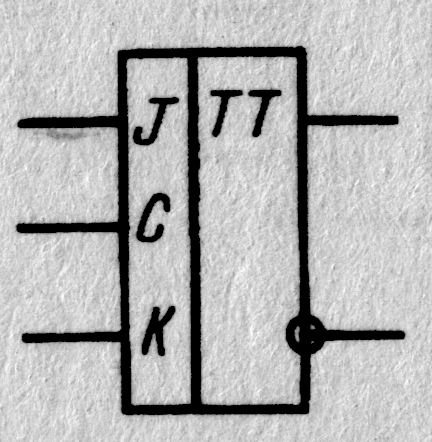

Универсальный JK-триггер с двухступенчатым запоминающим информации

|  |

| Вход | Выход | |

| J | K | Q |

| Q0 | ||

|

При J=0 и К=0 срабатывание не происходит и триггер остается в исходном состоянии Q0.

При J=0 и К=1 логическая единица действует на вход установки в нулевое состояние К и триггер переходит в нулевое состояние.

При J=1 и К=0 логическая единица действует на вход установки в единичное состояние J и триггер переходит в единичное состояние.

Универсальный триггер не имеет запрещенной комбинации входных сигналов и при J=1 и К=1 состояние триггера меняется на противоположное.

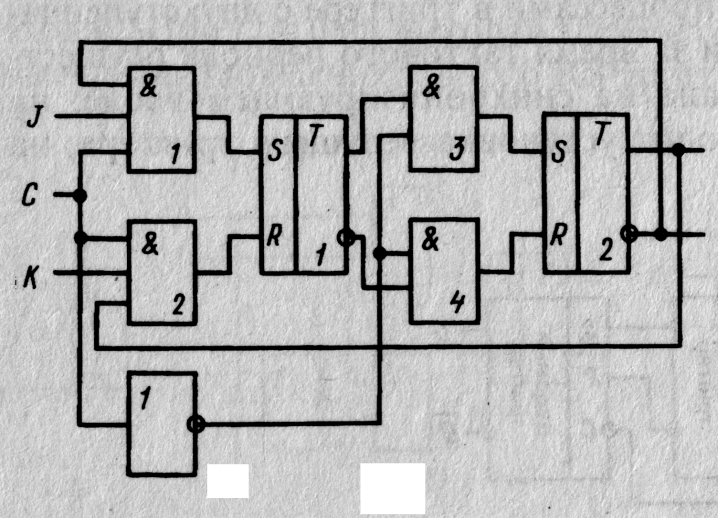

Срабатывание триггера с двухступенчатым запоминанием информации происходит в два этапа:

1)при положительном перепаде (С=1) новое состояние формируется в первом RS-триггере, а логические уровни на выходах JK триггера не изменяются;

2)при отрицательном перепаде (С=0) новое состояние, сформированное в первом RS-триггере передается во второй RS- триггер и меняются логические уровни на выходах JK-триггера.

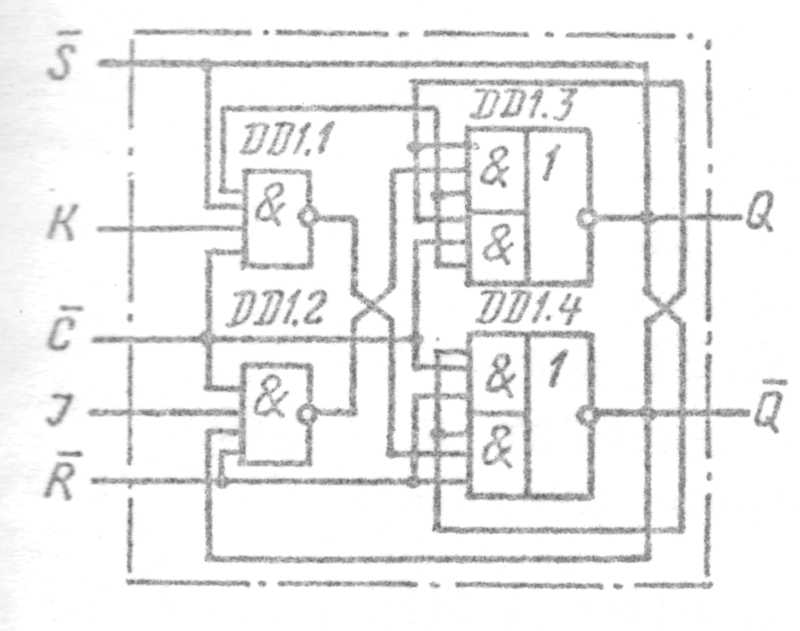

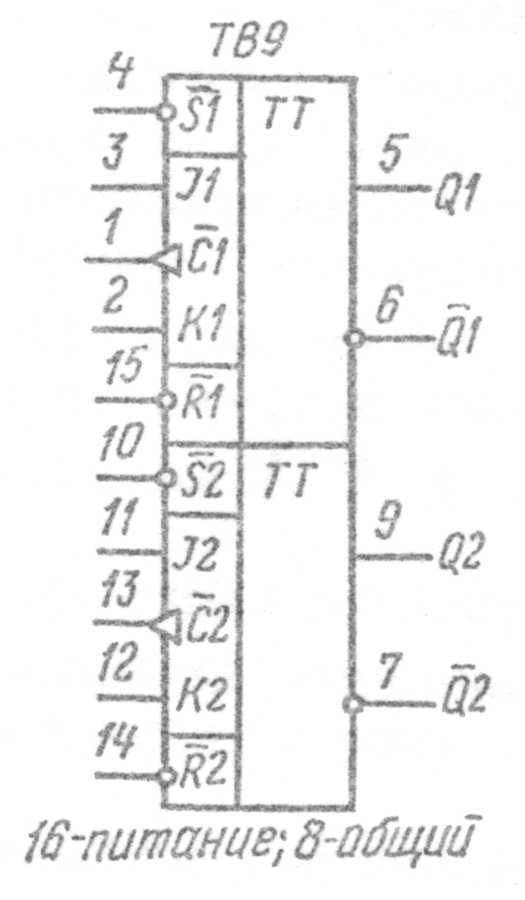

Микросхема К155ТВ9

Микросхемы ТВ6 и ТВ9, ТВ 10 и ТВ 11 содержат по два JK-триггера с общим выводом питания (рис. 2.52). Вход синхронизации  у всех триггеров инверсный динамический, поэтому Данные от входов J и K переносятся на выходы Q и

у всех триггеров инверсный динамический, поэтому Данные от входов J и K переносятся на выходы Q и  по отрицательному перепаду импульса

по отрицательному перепаду импульса  . Когда импульс на входе

. Когда импульс на входе  переходит от высокого уровня к низкому, сигналы на входах J и K не должны изменяться. Информацию от входов J и K следует загружать в триггер, когда на входе

переходит от высокого уровня к низкому, сигналы на входах J и K не должны изменяться. Информацию от входов J и K следует загружать в триггер, когда на входе  присутствует напряжение высокого уровня. У триггеров микросхемы ТВ6 нет входа предварительной установки

присутствует напряжение высокого уровня. У триггеров микросхемы ТВ6 нет входа предварительной установки  , поэтому в таблице состояний (комбинированного J K-триггера) необходимо исключить первую строку (асинхронную установку 1). Если на вход

, поэтому в таблице состояний (комбинированного J K-триггера) необходимо исключить первую строку (асинхронную установку 1). Если на вход  будет подано напряжение низкого уровня, то входы J, K и

будет подано напряжение низкого уровня, то входы J, K и  не действуют. У триггеров микросхемы ТВ10 нет входа предварительного сброса

не действуют. У триггеров микросхемы ТВ10 нет входа предварительного сброса  , поэтому в таблице состояний комбинированного J K-триггера необходимо исключить вторую строку (асинхронный сброс 0). Для микросхем ТВ6 и ТВ10 в таблице состояний не имеет смысла и третья строка, т.к. они имеют только по одному асинхронному входу (либо

, поэтому в таблице состояний комбинированного J K-триггера необходимо исключить вторую строку (асинхронный сброс 0). Для микросхем ТВ6 и ТВ10 в таблице состояний не имеет смысла и третья строка, т.к. они имеют только по одному асинхронному входу (либо  , либо

, либо  ). Триггеры микросхемы ТВ11 в отличие от триггеров микросхемы ТВ9 имеют две общие цепи управления: вход синхронизации

). Триггеры микросхемы ТВ11 в отличие от триггеров микросхемы ТВ9 имеют две общие цепи управления: вход синхронизации  и асинхронный вход сброса

и асинхронный вход сброса  (рис. 2.53).

(рис. 2.53).

Рис. 2.52. Структура, условное обозначение и цоколевка микросхем ТВ 6, ТВ9 и ТВ 10

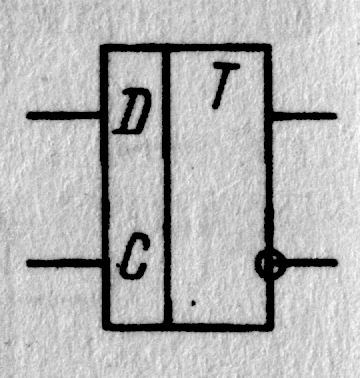

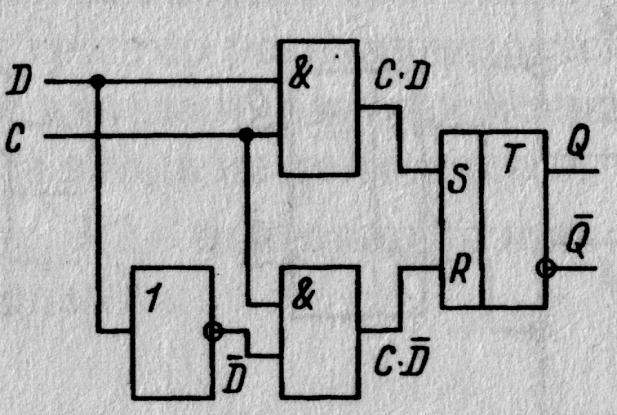

Синхронный D – триггер.

|  |

| Вход | Выход |

| D | Q |

При С=0 срабатывание триггера не происходит.

При С=1 и D=0 триггер устанавливается в нулевое состояние. При С=1 и D=1 триггер устанавливается в единичное состояние.

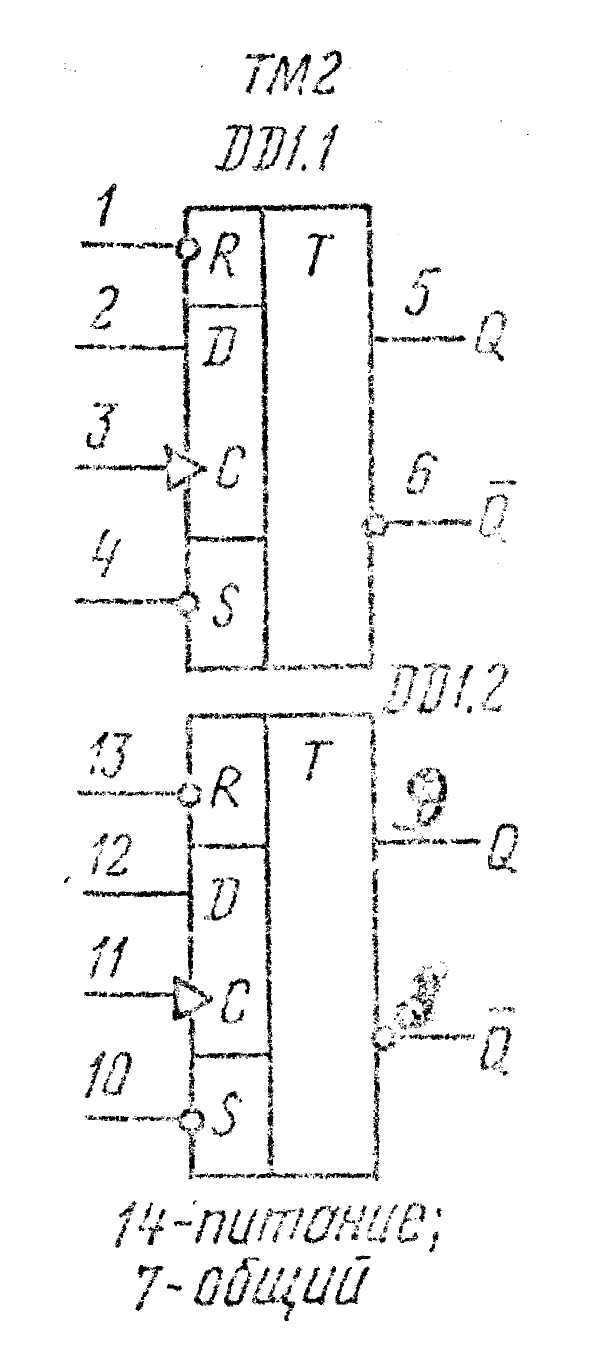

Микросхема К155ТМ 2

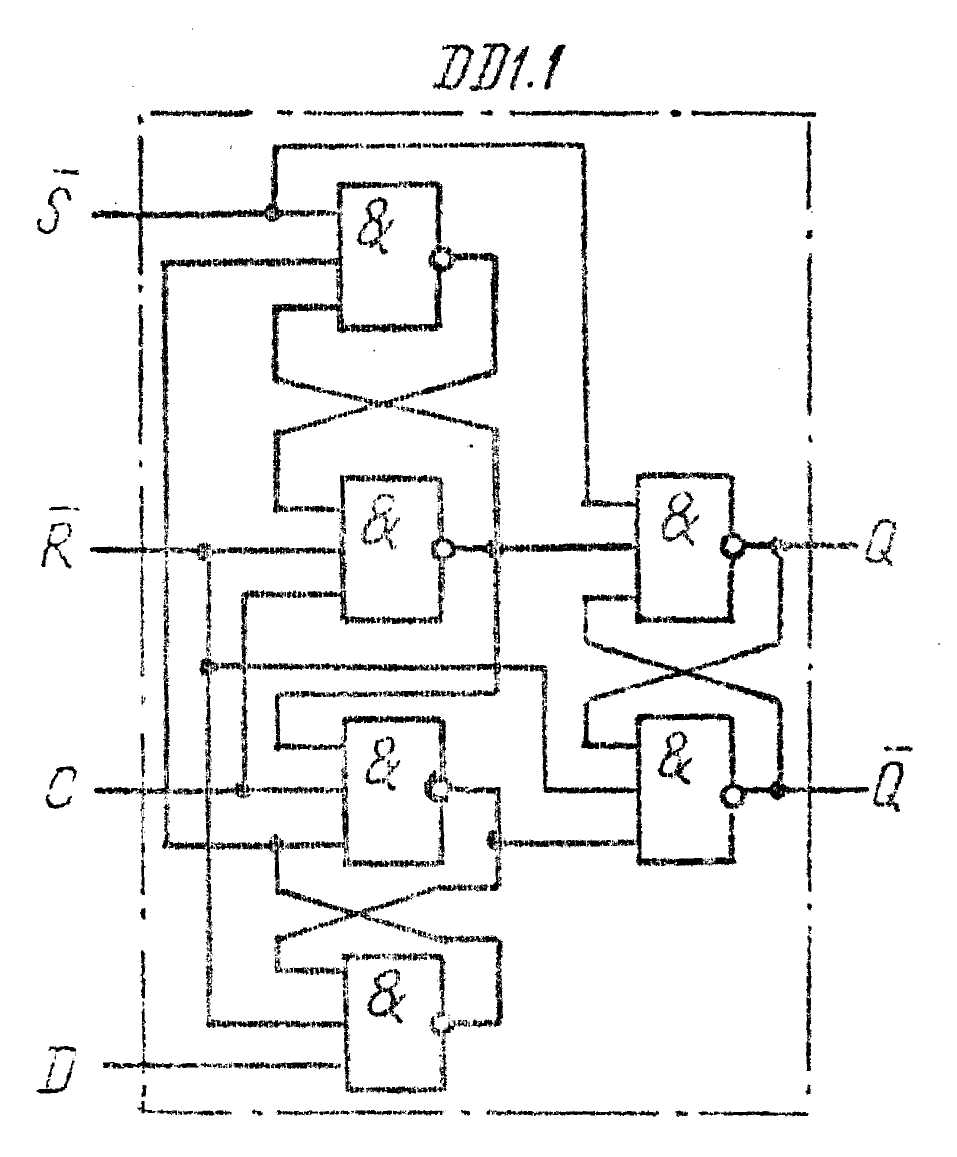

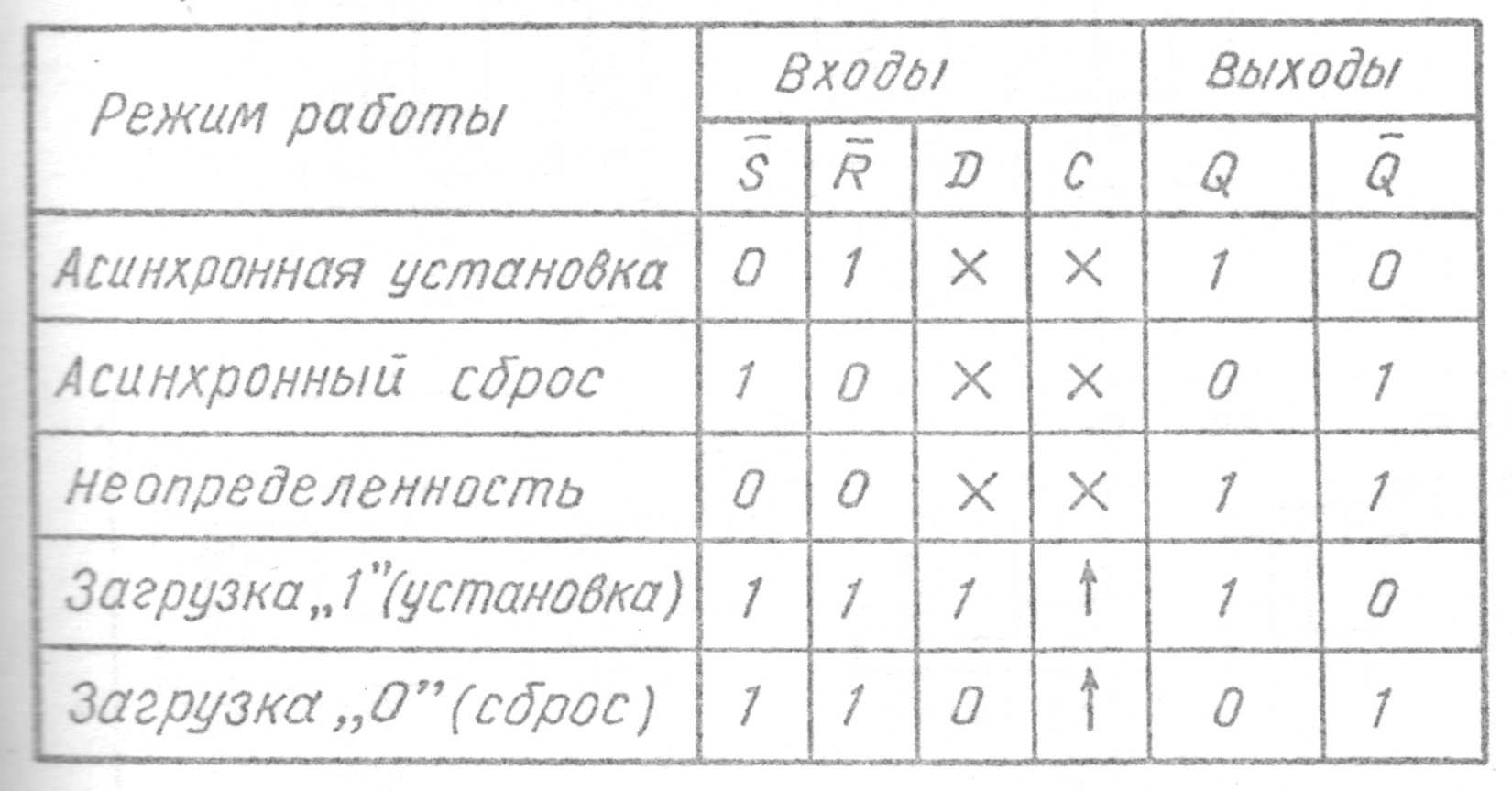

Микросхема ТМ 2 содержит два независимых комбинированных D-триггера, имеющих общую цепь питания. У каждого триггера имеется один информационный вход D, вход синхронизации С и два дополнительных входа  и

и  независимой асинхронной установки триггера в единичное и нулевое состояния, а также комплементарные выходы Q и

независимой асинхронной установки триггера в единичное и нулевое состояния, а также комплементарные выходы Q и  (рис. 2.46). Логическая структура одного D-триггера {рис. 2.46) содержит следующие элементы: основной асинхронный RS-триггер (ТЗ), вспомогательный синхронный RS-триггер (Т1) записи логической единицы (высокого уровня) в основной триггер, вспомогательный синхронный RS-триггер (Т2) записи логического нуля (низкого уровня) в основной триггер. Входы

(рис. 2.46). Логическая структура одного D-триггера {рис. 2.46) содержит следующие элементы: основной асинхронный RS-триггер (ТЗ), вспомогательный синхронный RS-триггер (Т1) записи логической единицы (высокого уровня) в основной триггер, вспомогательный синхронный RS-триггер (Т2) записи логического нуля (низкого уровня) в основной триггер. Входы  и

и  - асинхронные, потому что они работают (сбрасывают состояние триггера) независимо от сигнала на тактовом входе, активный уровень для них низкий (т. е. инверсные входы S и R).

- асинхронные, потому что они работают (сбрасывают состояние триггера) независимо от сигнала на тактовом входе, активный уровень для них низкий (т. е. инверсные входы S и R).

Асинхронная установка D-триггера в единичное или нулевое состояния осуществляется подачей взаимопротивоположных логических сигналов на входы  и

и  . В это время входы D и С не влияют.

. В это время входы D и С не влияют.

Если на входы  и

и  одновременно подать сигнал низкого уровня (логический нуль), то на обоих выходах триггера Q и

одновременно подать сигнал низкого уровня (логический нуль), то на обоих выходах триггера Q и  будет высокий уровень (логическая единица). Однако после снятия этих сигналов со входов

будет высокий уровень (логическая единица). Однако после снятия этих сигналов со входов  и

и  состояние триггера будет неопределенным. Поэтому комбинация

состояние триггера будет неопределенным. Поэтому комбинация  =

=  = 0 для этих входов является запрещенной.

= 0 для этих входов является запрещенной.

Загрузить в триггер входные уровни В или Н (т, е. логические 1 или 0) можно, если на входы  и

и  подать напряжение высокого уровня:

подать напряжение высокого уровня:  =

=  = 1. Сигнал от входа D передается на выходы триггера при поступлении положительного перепада импульса на вход С (изменение от низкого к высокому). Однако, чтобы D-триггер переключался правильно (согласно таблице состояний, табл. 2.24), необходимо уровень на входе D зафиксировать заранее, т, е. до прихода перепада на вход С. Причём этот защитный временной интервал должен быть больше времени задержки распространения сигнала в триггере (определяется по справочнику).

= 1. Сигнал от входа D передается на выходы триггера при поступлении положительного перепада импульса на вход С (изменение от низкого к высокому). Однако, чтобы D-триггер переключался правильно (согласно таблице состояний, табл. 2.24), необходимо уровень на входе D зафиксировать заранее, т, е. до прихода перепада на вход С. Причём этот защитный временной интервал должен быть больше времени задержки распространения сигнала в триггере (определяется по справочнику).

Цоколевка микросхемы ТМ 2 приведена на рис. 2.47, а основные параметры см. в табл. 2.20.

Рис. 2.46. Структура D-триггера Рис. 2.47. Условное обозначение и микросхемы ТМ 2 цоколевка микросхемы ТМ 2

Таблица 2.24. Состояния триггера ТМ 2

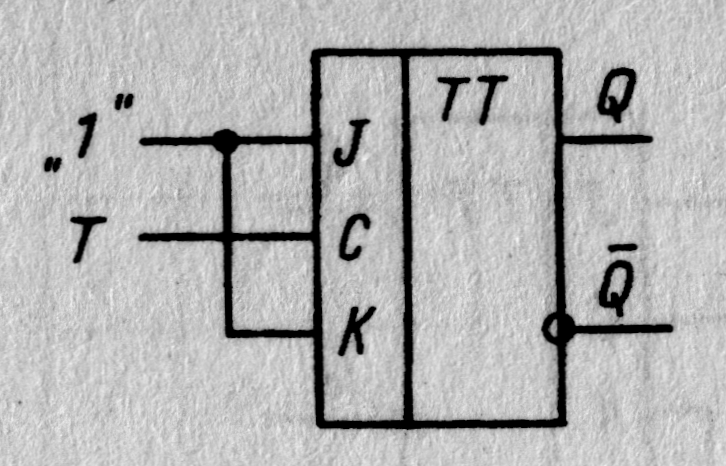

Т-триггер

Состояние триггера меняется на противоположное, если на вход поступает прямоугольный импульс, во всех остальных случаях срабатывание триггера не происходит.

Регистры

Общие сведения

Регистр предназначен для хранения многоразрядных двоичных чисел (слов). Поэтому его основу составляют запоминающие элементы – триггеры. В каждом из них хранится цифра разряда числа. Кроме хранения, регистр может осуществлять сдвиг принятого слова, преобразование параллельного кода в последовательный и наоборот, преобразование кода из прямого в обратный (когда 1 заменяются 0, а 0 – 1) и наоборот, и некоторые арифметические и логические операции.

В соответствии со способом ввода и вывода разрядов числа различают параллельные, последовательные и комбинированные регистры (рис. 4.2.1).

Рис. 4.2.1.

В параллельном регистре (регистре памяти) ввод и вывод слова осуществляется в параллельной форме – одновременно всех рарядов, в последовательном (сдвиговом) регистре разряды числа вводятся и выводятся последовательно, в комбинированном регистре ввод числа осуществляется в параллельной форме, а вывод в последовательной или наоборот.

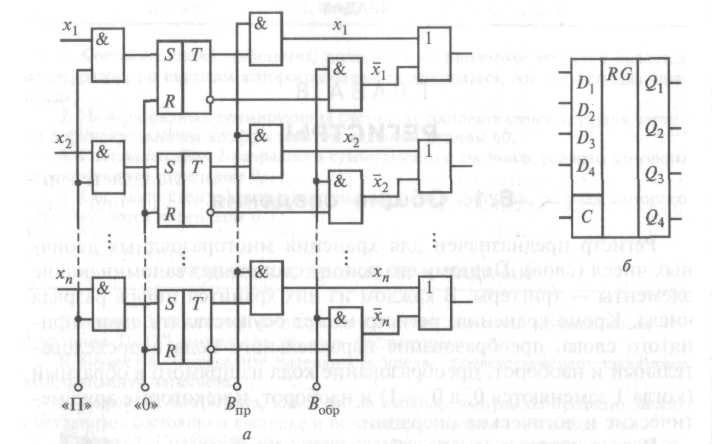

Параллельный регистр

На рис. 4.2.2, а приведена функциональная схема параллельного регистра (регистра памяти) на RS - триггерах при однофазном способе приема числа хn... х2, х1,. Так как сигналы, поступающие только на входы S, не могут установить соответствующие триггеры в состояния 0 (из-за чего число будет записано с ошибкой), то перед приемом числа все триггеры регистра обнуляются. Для этого на линию «О» подается лог. 1. Подготовка к приему новой информации составляет первый такт. Во втором такте по сигналу 1 на линии «П» («Прием») двоичное число всеми разрядами одновременно (параллельно) через конъюнкторы записывается в разряды регистра. Выдача числа в прямом коде осуществляется по сигналу лог. 1 на линии Впр, а в обратном – по сигналу лог. 1 на линии Вобр.

Рис. 4.2.2

Ввод информации в рассматриваемом регистре может осуществляться и парафазным способом, когда i-й разряд числа на S-вход поступает непосредственно, а на R-вход – через инвертор. Этим исключается необходимость предварительной установки триггеров в 0, так как теперь его состояние целиком определяется сигналами на S- и R-входах, т. е. цифрой в разряде кода. Такая запись числа осуществляется в один такт и производится намного быстрее, чем двухтактная. Параллельный регистр можно реализовать и на других типах триггеров, имеющих информационные входы.

Условное изображение одного из типов параллельного четырехразрядного регистра приведено на рис. 8.2, б, где Q1– Q4 – выходы разрядов регистра, D1–D4 – входы, с которых в регистр одновременно записываются все разряды заносимого слова при поступлении импульса разрешения на С-вход.

Последовательный регистр

В последовательных регистрах число вводится и выводится последовательно разряд за разрядом. Разряды такого регистра соединены последовательно. Каждый разряд выдает информацию в следующий и одновременно принимает новую информацию из предыдущего. Для этого каждый разряд должен иметь два запоминающих элемента. В первый элемент передается информация из предыдущего разряда, одновременно второй запоминающий элемент передает свою информацию в последующий разряд; затем информация, принятая первым запоминающим элементом, передается во второй, а первый освобождается для приема новой информации.

Двухступенчатый триггер (например, JK-триггер, D-триггер) представляет совокупность двух запоминающих элементов, поэтому он один может составлять разряд последовательного регистра.

Если в цепи таких триггеров выходы одного триггера соединить со входами другого, то по фронту тактового импульса во входную ступень каждого триггера будет заноситься информация из выходной ступени предыдущего триггера, а по спаду импульса она будет переписываться в выходную ступень. Теперь (по фронту следующего тактового импульса) во входной ступени триггера информация может быть заменена новой (из предыдущего триггера) без опасения, что предыдущая будет потеряна.

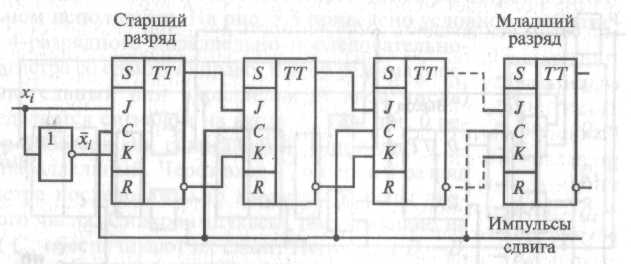

Функциональная схема последовательного регистра приведена на рис. 4.2.3, где, к примеру, левый триггер предназначен для хранения старшего разряда числа, а правый – для хранения младшего разряда. Разряды двоичного числа (высокие и низкие потенциалы), начиная с его младшего разряда, последовательно поступают на входы старшего разряда регистра. Поступление разрядов числа чередуется с поступлением импульсов сдвига, которыми вводимые разряды продвигаются вдоль регистра, пока младший разряд n –разрядного числа не окажется в младшем разряде регистра.

Рис. 4.2.3

Для выдачи записанного в последовательной форме числа надо на входы старшего разряда регистра подать хi= 0, хi = 1, а на линию импульсов сдвига – n импульсов. Первый импульс выдвинет из младшего разряда регистра младший разряд числа, на его место передвинется второй разряд числа и т. д. – все число сдвинется вдоль регистра на один разряд. Одновременно с входов в старший разряд регистра будет записан 0. Второй импульс сдвига выдвинет из регистра второй разряд числа и продвинет 0 из старшего разряда регистра в соседний, более младший и т. д. После n импульсов сдвига число будет полностью выведено из регистра, в разряды которого окажутся записанными нули. В соответствии с механизмом перемещения разрядов числа вдоль регистра последовательный регистр называют сдвигающим (сдвиговым). Он может быть однонаправленным (для сдвига числа в сторону младшего разряда – правый сдвиг, в сторону старшего разряда – левый сдвиг), а также реверсивным, обеспечивающим сдвиг в обе стороны.

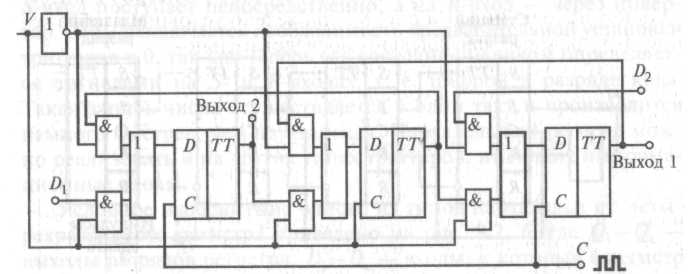

Схема реверсивного сдвигового регистра изображена на рис. 4.2.4. При V= 1 верхний ряд конъюнкторов заблокирован и в регистр сдвиговыми импульсами могут вдвигаться разряды слова слева направо с входа D1. При V=0 блокируется нижний ряд конъюнкторов и слово может вдвигаться в регистр с входа D2 справа налево.

Рис. 4.2.4.