Правила схемного включения элементов

Выпускаемые промышленностью микросхемы ТТЛ серий выполняют простейшие логические операции (И–НЕ; ИЛИ–НЕ и др.), содержат в одном корпусе несколько независимых логических элементов, связанных между собой только источником питания.

Если некоторые логические элементы, входящие в состав корпуса, не используются, то рекомендуется такие элементы включать так, чтобы на их выходах был высокий потенциал  . Для этого входы неиспользуемых элементов ТТЛ серий, выполняющих операции И–НЕ и ИЛИ–НЕ соединяют с общей (земляной) шиной. В таком состоянии элемент потребляет (рассеивает) минимальную мощность, и его выход можно использовать как источник логической единицы на входах других схем.

. Для этого входы неиспользуемых элементов ТТЛ серий, выполняющих операции И–НЕ и ИЛИ–НЕ соединяют с общей (земляной) шиной. В таком состоянии элемент потребляет (рассеивает) минимальную мощность, и его выход можно использовать как источник логической единицы на входах других схем.

Неиспользованные входы логического элемента ТТЛ серий можно оставлять свободными, но при этом снижается помехоустойчивость из-за воздействия наводок на свободные выводы. В сериях ТТЛ и ТТЛШ неиспользованные входы объединяют с другими используемыми входами, если это не ведет к превышению нагрузочной способности предыдущего каскада, либо подключают к источнику логической единицы.

В качестве источника логической единицы используют неиспользованные элементы, входы которых заземлены, или источник питания микросхемы, который подключают ко входу через резистор с сопротивлением 1 кОм, ограничивающий входной ток. К одному такому резистору обычно подключается до 20 неиспользованных входов.

Для уменьшения помех по цепи питания в точках подключения к шинам групп логических элементов включаются развязывающие керамические конденсаторы емкостью порядка 0,1 мкФ на один корпус. При большом числе одновременно переключаемых логических элементов броски тока в цепи питания достигают единиц–десятков А. Поэтому между цепью питания и общей шиной устанавливаются электролитические конденсаторы большой емкости, которые компенсируют кратковременные импульсы тока и обеспечивают уменьшение взаимосвязи логических элементов через цепь питания.

Небольшие значения выходных сопротивлений элементов ТТЛ серий приводят к тому, что во время переключения схемы ток в цепи питания возрастает и может в несколько раз превышать ток, потребляемый схемой в статическом режиме. Поэтому при увеличении частоты переключения, мощность потребляемая ТТЛ схемой со сложным инвертором растет, все это приводит к недопустимости соединения выходов нескольких схем. Если такое соединение осуществить, то в состоянии, когда один из элементов имеет на выходе низкий уровень напряжения  , а другой – высокий

, а другой – высокий  , через последовательно включенные транзистор VТ3 одной схемы и транзистор VТ4 другой схемы (рис. 9.16) будет протекать большой ток.

, через последовательно включенные транзистор VТ3 одной схемы и транзистор VТ4 другой схемы (рис. 9.16) будет протекать большой ток.

Величина этого тока определяется выражением (9.30) и может в несколько раз превышать ток в статическом режиме

, (9.30)

, (9.30)

где Uпр – падение напряжения на открытом транзисторе.

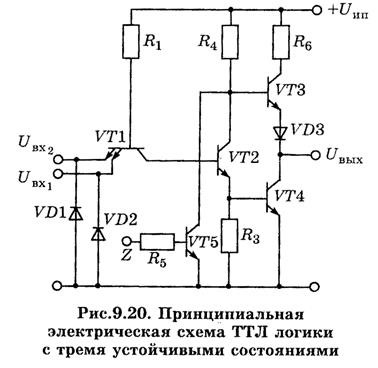

При этом резко возрастает потребляемая мощность, и возможен выход схем из строя, так как транзисторы обычно не рассчитаны на длительное протекание больших токов. В связи с этим при проектировании цифровых схем не допускается объединение выходов таких элементов. Если несколько узлов или блоков работают на общую нагрузку, то объединение выходов является необходимым. Для этих целей используется схема ТТЛ с тремя устойчивыми состояниями, представленная на рис. 9.20.

В приведенной схеме отличие от базового элемента состоит в том, что имеется третье состояние, при котором выходные транзисторы закрыты, и схе-

ма полностью отключается от нагрузки сигналом управляющего вывода Z, дающим разрешение по выходу. Третье состояние элемента не зависит от комбинации логических сигналов на входе элемента. Такие схемы объединяют по выходам, и они работают на общую нагрузку. Управление микросхем предусматривает обслуживание нагрузки в любой момент времени одним элементом, а другие элементы должны находиться в третьем состоянии. Выходное сопротивление закрытых транзисторов велико и элемент практически отключен от нагрузки. Такое состояние элементов называют высокоимпедансным. Это состояние достигается тем, что в схему включен транзистор VТ5 и резистор R5. При подаче на управляющий вход Z напряжения логического нуля, транзистор VT5 закрывается, элемент работает как обычный базовый элемент. Если на управляющий вход Z подается напряжение логической единицы, транзистор VТ5 переходит в режим насыщения, а транзисторы VТ3, VТ4 закрываются. Такие микросхемы используются в информационной технике для обслуживания проводника шины данных, и примером являются микросхемы К531ЛА17П, К531ЛА19П.

ма полностью отключается от нагрузки сигналом управляющего вывода Z, дающим разрешение по выходу. Третье состояние элемента не зависит от комбинации логических сигналов на входе элемента. Такие схемы объединяют по выходам, и они работают на общую нагрузку. Управление микросхем предусматривает обслуживание нагрузки в любой момент времени одним элементом, а другие элементы должны находиться в третьем состоянии. Выходное сопротивление закрытых транзисторов велико и элемент практически отключен от нагрузки. Такое состояние элементов называют высокоимпедансным. Это состояние достигается тем, что в схему включен транзистор VТ5 и резистор R5. При подаче на управляющий вход Z напряжения логического нуля, транзистор VT5 закрывается, элемент работает как обычный базовый элемент. Если на управляющий вход Z подается напряжение логической единицы, транзистор VТ5 переходит в режим насыщения, а транзисторы VТ3, VТ4 закрываются. Такие микросхемы используются в информационной технике для обслуживания проводника шины данных, и примером являются микросхемы К531ЛА17П, К531ЛА19П.

9.13. Эмиттерно–связанная логика

Цифровые микросхемы эмиттерно–связанной логики составляют схемы на переключателях тока с объединенными эмиттерами, обладающие по сравнению с другими типами цифровых схем наибольшим быстродействием и большой потребляемой мощностью.

Большое быстродействие ЭСЛ логики обеспечивается:

– за счет работы транзисторов в ненасыщенном (линейном) режиме;

– за счет применения на выходах схемы эмиттерных повторителей, ускоряющих процесс заряда и разряда нагрузочных емкостей;

– за счет ограничения перепада выходного напряжения, что приводит к снижению статической помехоустойчивости.

Наибольшее распространение получили ЭСЛ серии 100, 500, К500, 700, К1500, обеспечивающие выполнение любых арифметических и логических операций.

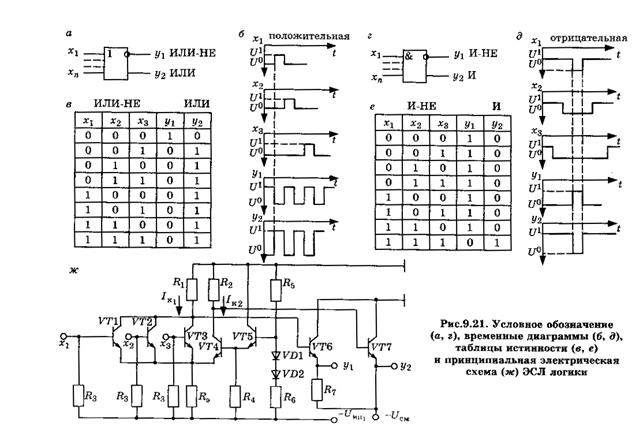

На рис. 9.21 представлены: условное графическое обозначение базового элемента, временные диаграммы, поясняющие работу элемента, таблица истинности и принципиальная электрическая схема ЭСЛ-логики. В зависимости от способа кодирования входной информации ("1" и "0") одна и та же схема (рис. 9.21,ж) может реализовать либо функции ИЛИ–НЕ, ИЛИ для положительной логики, либо функции И–НЕ, И для отрицательной логики. Для положительной логики "1" и "0" представляются напряжениями U0 = –1,45…–1,9 В; U1= –0,7…–0,95 В, а для отрицательной логики –напряжениями U1= –0,7…–0,95 В; U0= –1,45…–1,9 В.

В схемах ЭСЛ серий эмиттеры транзисторов токового переключателя через резистор Rэ подключаются к отрицательной шине источника напряжения Uип= –5,2±5 % В; коллекторные цепи заземляются. Такое включение обеспечивает меньшую зависимость выходного напряжения от наводок по цепи питания и лучшую помехозащищенность. Для повышения нагрузочной способности и расширения функциональных возможностей на выходах токового переключателя (VТЗ, VT4) включены транзисторы VТ6, VТ7, предназначенные для использования в качестве выходных эмиттерных повторителей с резисторами в цепи эмиттеров порядка 240…50 Ом. Для уменьшения потребляемой мощности при малых сопротивлениях нагрузок используют второй источник питания – Uсм. Для исключения влияния на логическую часть схемы импульсных помех, возникающих в коллекторных цепях эмиттерных повторителей в момент переключения схемы при работе на низкоомную нагрузку, используются две шины земля. Кроме того, выходные эмиттерные повторители смещают уровни сигналов по напряжению и обеспечивают совместимость ЭСЛ элементов по входу и выходу.

На транзисторах VТ1–VТ4 собран токовый переключатель, содержащий две ветви, работающие в режиме ключа и связанные эмиттерами через резистор Rэ. Транзисторы VТ1–VТЗ первой ветви и транзистор VТ4 второй ветви работают в активной области и не входят в режим насыщения. Для создания опорного напряжения Uбэ транзистора VT4 используется температурно-компенcирующая цепь (транзистор VТ5, диоды VD1, VD2 и резисторы R5, R6).

Рассмотрим принцип работы базового логического элемента для положительной логики. Если на все логические входы подается напряжение низкого уровня, соответствующее логическому нулю, то транзисторы VТ1–VТ3 закрываются, а транзистор VТ4 открывается, так как напряжение на его базе становится выше, чем на базах входных транзисторов. Через открытый транзистор протекает ток  , значение которого задается резистором Rэ, и создает падение напряжения на резисторе R2. Потенциал коллектора транзистора VТ4 при этом понижается и подается на вход эмиттерного повторителя, собранного на транзисторе VТ7. На выходе эмиттерного повторителя получается низкий уровень напряжения, соответствующий логическому нулю.

, значение которого задается резистором Rэ, и создает падение напряжения на резисторе R2. Потенциал коллектора транзистора VТ4 при этом понижается и подается на вход эмиттерного повторителя, собранного на транзисторе VТ7. На выходе эмиттерного повторителя получается низкий уровень напряжения, соответствующий логическому нулю.

В это же время через резистор R1 левой ветви токового ключа протекает небольшой обратный ток  . Потенциал коллектора транзистора VТ3 повышается и поступает на базу эмиттерного повторителя транзистора VТ6. На выходе транзистора VT6 имеем большой потенциал, логическую единицу, при этом выполняется логическая операция ИЛИ–НЕ.

. Потенциал коллектора транзистора VТ3 повышается и поступает на базу эмиттерного повторителя транзистора VТ6. На выходе транзистора VT6 имеем большой потенциал, логическую единицу, при этом выполняется логическая операция ИЛИ–НЕ.

Предположим, что на один из входов (вход 1) подается напряжение логической единицы, а на остальных входах действует логический нуль. Под действием входного сигнала транзистор VТ1 отрывается, через коллекторную и эмиттерную цепь протекают большие токи  и Iэ. Ток Iэ создает падение напряжения на сопротивлении резистора Rэ, которое резко уменьшает напряжение

и Iэ. Ток Iэ создает падение напряжения на сопротивлении резистора Rэ, которое резко уменьшает напряжение  , транзистор VТ4 закрывается. Перепады напряжений коллекторных цепей транзисторов VТ1, VТ4 подаются на входы соответствующих эмиттерных повторителей. Таким образом по выходу транзистора VТ6 выполняется логическая операция ИЛИ–НЕ, а по выходу транзистора VТ7 – логическая операция ИЛИ. Воздействие входного сигнала приводит к переключению тока эмиттера Iэ, который проходит в зависимости от амплитуды входного сигнала то через левую, то через правую ветви, и при этом на выходе создаются низкий и высокий уровни напряжения одновременно. Поэтому такую схему с объединенными эмиттерами часто называют токовым ключом.

, транзистор VТ4 закрывается. Перепады напряжений коллекторных цепей транзисторов VТ1, VТ4 подаются на входы соответствующих эмиттерных повторителей. Таким образом по выходу транзистора VТ6 выполняется логическая операция ИЛИ–НЕ, а по выходу транзистора VТ7 – логическая операция ИЛИ. Воздействие входного сигнала приводит к переключению тока эмиттера Iэ, который проходит в зависимости от амплитуды входного сигнала то через левую, то через правую ветви, и при этом на выходе создаются низкий и высокий уровни напряжения одновременно. Поэтому такую схему с объединенными эмиттерами часто называют токовым ключом.

Резисторы в цепях базы токового ключа R3 служат для стекания обратного базового тока и надежного запирания незадействованных входных транзисторов. При их отсутствии самоотпирание незадействованных входных транзисторов будет мешать нормальной работе схемы, и потребуется внешнее принудительное подключение таких входов к источнику отрицательного напряжения.

Перспективными считаются ЭСЛ серии 500 и К1500. Серия К1500 относится к числу субнаносекундных и имеет время задержки менее 1 нс.

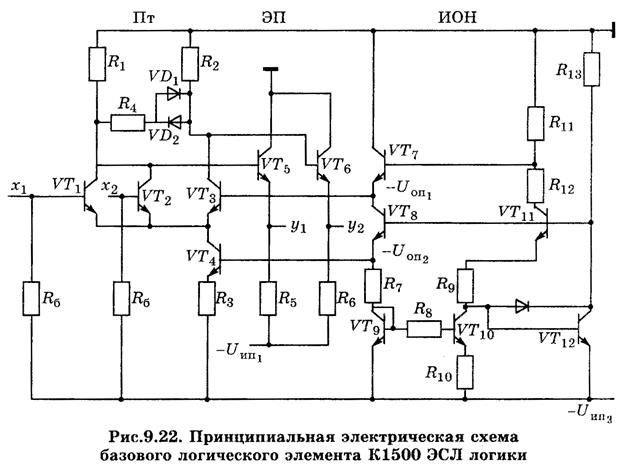

На рис. 9.22 приведена принципиальная электрическая схема базового логического элемента серии К1500, являющегося модернизацией базового логического элемента серии 500. Элемент реализует функции 2И/2И–НЕ, И для отрицательной логики.

Логический элемент состоит из трех частей: токового переключателя (ТП), эмиттерных повторителей (ЭП), источника опорного напряжения (ИОН). Назначение и функции указанных частей соответствуют назначению и функциям аналогичных цепей рассмотренного базового логического элемента ЭСЛ серий. В микросхеме К1500 используется более стабильный генератор тока на транзисторе VТ4 и резисторе R3, термостабилизирующая цепочка на диодах VD1, VD2, резисторе R4, между коллекторами транзисторов переключателя тока, усовершенствованный источник опорного напряжения, раздельные источники питания  (для ЭП),

(для ЭП),  (для ПТ и ИОН).

(для ПТ и ИОН).

Все это позволило стабилизировать статические и динамические параметры схемы:

– при изменении напряжения питания  в диапазоне –5,7…–4,2 В;

в диапазоне –5,7…–4,2 В;

– при изменении температуры на основании корпуса в пределах +1…+85 °С;

– увеличить помехозащищенность схемы по цепи питания.

Недостатком данной схемы является большая потребляемая мощность Pп ср = 50 мВт.

Интегральные схемы на эмиттерно–связанной логике используются в качестве элементной базы быстродействующих систем связи, вычислительной техники и радиоэлектронной аппаратуры. Они обладают следующими достоинствами:

1. Высокая помехоустойчивость.

2. Высокое быстродействие при средней потребляемой мощности и сверхвысокое быстродействие при большой потребляемой мощности.

3. Высокая стабильность динамических параметров при изменении рабочей температуры и напряжения питания.

4. Высокий коэффициент разветвления (высокая нагрузочная способность).

5. Возможность работы на низкоомные согласованные линии связи и нагрузки.

6. Малая мощность переключения и независимость тока потребления от частоты переключения.

7. Использование биполярной технологии изготовления.

9.14. Интегральная инжекционная логика (И2Л)

Схемы интегральной инжекционной логики иногда называемые совмещенной транзисторной логикой (СТЛ) или схемами с инжекционным питанием нашли широкое применение при создании БИС и СБИС и не имеют аналогов среди логических элементов на дискретных транзисторах. В БИС с инжекционным питанием питание осуществляется путем инжекции неравновесных носителей в полупроводниковый кристалл через инжекторный переход.

Питание инжектора осуществляется от внешнего генератора тока или от источника напряжения через внешний резистор. Напряжение питания невелико и составляет 1…1,5 В. Схемы с инжекционным питанием могут нормально функционировать при изменении тока питания Iп в широких пределах (10-8…10-3 А), что достигается изменением сопротивления резистора, который для уменьшения мощности рассеивания в кристалле находится вне корпуса микросхемы. Изменяя сопротивление резистора R или напряжение источника питания Uип можно в широких пределах (3…4 порядка) регулировать ток питания, мощность потребляемую схемой и быстродействие, что невозможно выполнять в ТТЛ и ЭСЛ схемах. Инжекционные логические схемы способны работать при сверхмалых токах (1 нА), в связи с чем возникает проблема токовой совместимости с другими логическими элементами. Увеличение тока получают с помощью каскадирования элементов И2Л с соответствующим увеличением площади коллекторов от каскада к каскаду. Входная цепь И2Л выполняется с учетом совместимости своих входных и выходных сигналов от предшествующих каскадов, которыми обычно служат элементы ТТЛ типа.

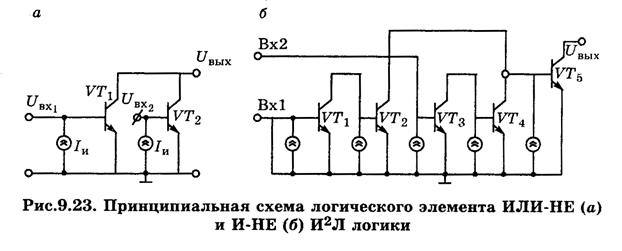

Основой элементов интегральной инжекционной логики является ключ, представляющий собой транзистор с инжекционным питанием. Упрощенная эквивалентная схема которого состоит из транзистора n–p–n типа и генератора тока инжекции Iи в цепи базы. Схема элемента, выполняющего логическую операцию ИЛИ–НЕ, представлена на рис. 9.23,а.

Принцип работы схемы следующий. Если хотя бы на один из входов схемы подать сигнал логической единицы, от предыдущей схемы, у которой транзистор закрыт, то ток от генератора тока Iи потечет в базу транзистора, транзистор открывается и переходит в режим насыщения. Выходное напряжение соответствует логическому нулю. Если на обоих входах действуют сигналы логического нуля, т.е. входы закорочены, токи Iи не будут проходить в базу транзисторов, а потекут во входные цепи. Транзисторы VТ1, VТ2 будут закрыты, их выходное напряжение соответствует логической единице. Таким образом параллельное соединение нескольких ключей образует логический элемент ИЛИ–НЕ.

Принципиальная схема логического элемента И–НЕ представлена на рис. 9.23,б. Сигнал на общем выходе схемы – коллекторе транзистора VТ5 будет тогда, когда на входы одновременно поступают одинаковые сигналы. Если на все входы подается низкий потенциал, соответствующий логическому нулю, инвертор VТ5 закрывается, и на выходе имеется высокий потенциал.

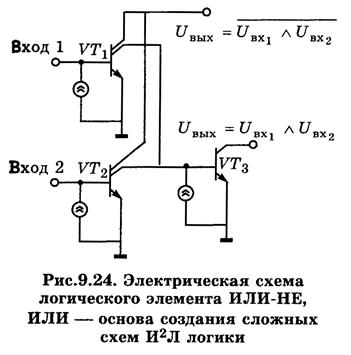

При подключении нескольких входных цепей к выходу одного каскада может ухудшиться функциональная надежность элемента, потому что входные (базовые) токи нагрузочных транзисторов в режиме насыщения зависят от коллекторных токов входных транзисторов. Транзисторы с большими коллекторными токами будут иметь меньший коэффициент насыщения. Для устранения этого недостатка используются многоколлекторные n–р–n транзисторы, у которых в области базы формируется несколько коллекторных областей. Каждый коллектор в элементе И2Л-типа рассматривается как независимый источник выходного сигнала. Наличие нескольких коллекторов позволяет получить развязанные логические выходы для одной ключевой схемы, что облегчает построение сложной логической схемы. На рис. 9.24 представлена схема, выполняющая логические операции ИЛИ–НЕ и ИЛИ, которая является основой для создания более сложных цифровых схем. Число коллекторов переключательного транзистора определяет нагрузочную способность схемы.

Интегральные инжек-ционные логические схемы являются перспективными для совершенствования БИС. Струк-туры с инжекционным питанием все время совершенствуются за счет:

Интегральные инжек-ционные логические схемы являются перспективными для совершенствования БИС. Струк-туры с инжекционным питанием все время совершенствуются за счет:

1. Использования диодов Шотки для реализации логичес-ких функций и уменьшения логического перепада.

2. Создания структур с низкоомным эмиттером, активная область эмиттерного перехода приближается к размеру коллек-тора.

3. Применения метали-ческого коллектора.

Достоинствами элементов интегральной инжекционной логики и микросхем на их основе являются: малое потребление энергии, среднее быстродействие, высокая степень интеграции.

Недостатками являются: малый перепад между логической единицей и нулем, чувствительность к помехам, невозможность непосредственной стыковки с другими типами логических микросхем. Элементы И2Л используются для создания БИС и СБИС, где они выполняют все логические функции внутри структуры и связь с внешними цепями осуществляется с помощью ТТЛ элементов.