Типовые функциональные узлы цифровых устройств

До сих пор мы рассматривали варианты реализации и характеристики логических элементов, выполняющих простейшие операции над булевыми переменными. Далее будут рассмотрены функциональные узлы, выполняющие типовые для цифровых устройств микрооперации.

Функциональные узлы сложнее, чем логические элементы, поэтому рассмотрение их на уровне электрических схем чаще всего неприемлемо. Как правило, работа функциональных узлов исследуется приближенно, без раскрытия их электрических схем, когда узлы представляются логической структурой, составленной из идеализированных логических элементов.

При рассмотрении функциональных узлов встречаются действия не только над буквенными переменными, но и над словами (многоразрядными), то есть упорядоченными совокупностями переменных:

- двоичные переменные

- двоичные переменные  .

.  или

или  .

.

В дальнейшем, если специально не оговорено, подразумеваем, что старший разряд находится слева.

При проектировании цифровых логических устройств необходимо учитывать не только реализуемые или логические операции, но и задержки в самих логических элементах и цепях связи.

В простейшей и наиболее распространенной модели логического элемента характеристикой времени распространения сигнала служит так называемая «чистая» задержка  . Наиболее часто изготовитель элементов указывает предельные максимальные значения задержек

. Наиболее часто изготовитель элементов указывает предельные максимальные значения задержек  . Максимальная задержка сигнала на пути, содержащем

. Максимальная задержка сигнала на пути, содержащем  каскадов:

каскадов:

В действительности время задержки может оказаться меньшим.

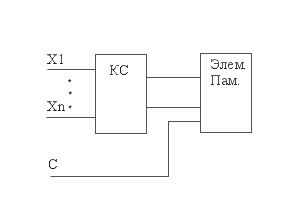

Влияние задержек в элементах может существенно изменять функционирование цифровых устройств. Для комбинационных цепей задержки не только ограничивают быстродействие, но могут создавать на выходе одновременно существующие ложные сигналы (риски или риски сбоя). Со временем они исчезают и выход приобретает значение, предусмотренное логической формулой, описывающей работу устройства. Особенно опасны, если выход КС является входом памяти.

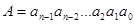

Различают статические и динамические риски. Статические риски существуют, когда состояние выхода должно остаться неизменным, но в действительности кратковременно изменяется. Пример:

Цепь реализует операцию  , возможно одновременное изменение аргументов. При изменении набора с 10 на 01 или наоборот на выходе должна сохраняться логическая единица. Из-за разных задержек

, возможно одновременное изменение аргументов. При изменении набора с 10 на 01 или наоборот на выходе должна сохраняться логическая единица. Из-за разных задержек  и

и  в цепях схемы возникают ситуации: без сбоя а) или со сбоем б). В последнем случае проявляется статический риск сбоя – на выходе временно появляется нулевой сигнал, не предусмотренный логикой работы схемы.

в цепях схемы возникают ситуации: без сбоя а) или со сбоем б). В последнем случае проявляется статический риск сбоя – на выходе временно появляется нулевой сигнал, не предусмотренный логикой работы схемы.

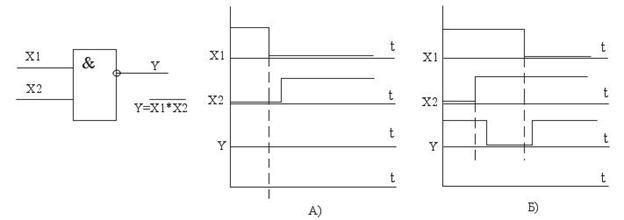

Для элемента ИЛИ-НЕ аналогично:

Динамический риск возникает когда логика работы схемы предусматривает изменение состояния на выходах, однако вместо однократного перехода выходной величины с одного уровня на другой происходят многократные переходы.

При динамическом риске первый и последний переходы всегда совпадают с алгоритмическим переходом, предусмотренный с логикой схемы. Статический риск таким свойством не обладает и считается более неблагоприятным.

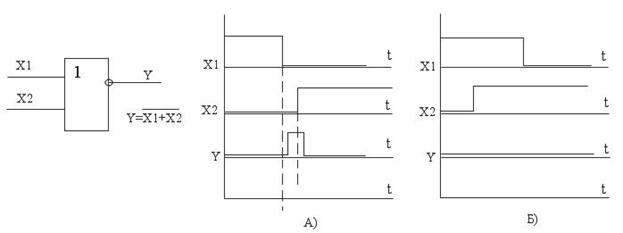

Для устранения сбоев из-за статического и динамического рисков используется синхронизация процессов при записи информации в элементы памяти.

Прием информации разрешается сигналом  , подаваемым после завершения переходных процессов в комбинационной схеме.

, подаваемым после завершения переходных процессов в комбинационной схеме.

Поэтому с точки зрения организации временных процессов ЦУ делят на асинхронные и синхронные.

В асинхронных – процессы переключения элементов происходят без внешнего управления.

В синхронных (тактируемых) процесс обработки информации упорядочен во времени с помощью тактовых сигналов от специального генератора.