Двоичная система счисления

Системой счисления называют совокупность символов (цифр) и приемов записи чисел. В зависимости от способа записи (изображения) чисел системы счисления делятся на непозиционные (например, римская система счисления) и позиционные. В современных ЭВМ используются только позиционные системы счисления. В позиционной системе счисления значение цифры в числе определяется ее местом (позицией).

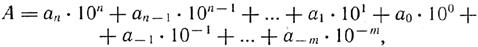

Позиционные системы счисления имеют наименования, совпадающие с количеством используемых в них цифр. В повседневной жизни мы пользуемся десятичной системой счисления, в которой для записи чисел используются десять цифр от 0 до 9. Любое положительное число А в десятичной системе можно записать в виде ряда

где 10 — основание системы; аn, an-1, ..., a1, a0, a-1, ..., a-т — коэффициенты, принимающие одно из значений от 0 до 9; п и т — любые целые цисла. Например, число 2078,5 может быть представлено в виде

Места, занимаемые цифрами числа, называются разрядами. В десятичной системе счисления единица каждого разряда «весит» в 10 раз больше единицы соседнего справа разряда.

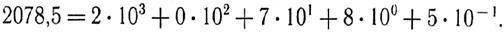

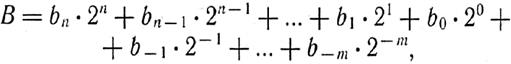

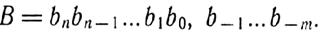

При цифровой обработке информации широко используется двоичная система счисления, в которой для записи чисел используются только две цифры: 0 и 1. Любое положительное число В в двоичной системе записывается в виде

где 2 — основание системы; bn, bn-1, ..., b1, b0, b-1, ..., b-т — коэффициенты, принимающие значения 0 или 1; пит — любые целые числа.

При записи чисел в двоичной системе счисления (как и в десятичной) знаки «плюс» между разрядами и основания системы с их степенными показателями опускаются, и двоичная запись числа В приобретает вид .

Целая часть числа отделяется от дробной точкой.

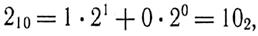

Числа 0 и 1 записываются в двоичной и десятичной системах одинаково. Начиная с числа 2 запись чисел в двоичной системе отличается от их записи в десятичной системе. Например, число 2 в двоичной системе записывается в виде

а число 3 — в виде

и т. д. Из этого примера также видно, что в двоичной системе единица каждого разряда (старшего) «весит» в два раза больше единицы соседнего с ним справа (младшего) разряда. Поэтому для записи некоторого числа в двоичной системе счисления необходимо иметь большее число разрядов, чем для записи этого числа в десятичной системе. Несмотря на этот недостаток, двоичная система широко применяется в цифровой технике благодаря тому, что для изображения одного разряда числа требуется элемент с двумя устойчивыми состояниями, одно из которых принимается за 0, а другое за 1. Таким элементом, как известно, может служить триггер.

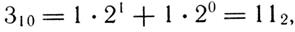

Арифметические действия с двоичными числами оказываются наиболее простыми по сравнению с арифметическими действиями над числами в других позиционных системах счисления и выполняются в соответствии с правилами, представленными в табл. 13.1.

Табл. 13.1. Правила выполнения арифметических операций с двоичными числами

В ЦВМ, помимо двоичной системы счисления, применяются восьмеричная, шестнадцатеричная и двоично-десятичная. Эти системы счисления являются вспомогательными и используются при подготовке задач к решению, т. е. при программировании.

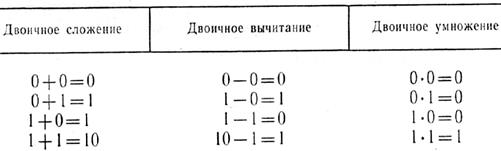

Достоинством восьмеричной системы счисления является то, что запись числа в ней оказывается в три раза короче записи этого же числа в двоичной системе, а переводы из восьмеричной системы в двоичную и наоборот очень просты. Если требуется двоичное число 11010010111 записать в восьмеричном коде, то его разбивают в обе стороны от точки, разделяющей целую и дробную части, на триады и каждую триаду представляют цифрой в восьмеричной системе:

Следовательно, 11010010112 = 32278. При переводе восьмеричного числа в двоичное каждую цифру представляют триадой в двоичном коде. Например, число 53278 переводится в двоичный код следующим образом:

т. е. 53278= 1010110101112.

В шестнадцатеричной системе счисления за основание системы принято число 16, поэтому в ней используется 10 цифр и 6 букв: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, А, В, С, D, E, F (буквы А, В, С, D, Е и F соответствуют числам 10, 11, 12, 13, 14 и 15 десятичной системы счисления). Эта система счисления используется для представления некоторых специфических видов информации в специализированных ЭВМ. Перевод шестнадцатеричных чисел в двоичные и наоборот подобен аналогичным преобразованиям чисел восьмеричной системы, с той разницей, что вместо двоичных триад используются тетрады. Например, число 1D9, Е516 переводится в двоичное следующим образом:

Если требуется двоичное число перевести в шестнадцатиричное, то его разбивают на тетрады влево и вправо от запятой, крайние неполные тетрады дополняют нулями, после чего каждую тетраду заменяют соответствующей цифрой шестнадцатеричной системы.

Вместо шестнадцатеричной системы часто применяется двоично-десятичная система, отличающаяся от шестнадцатеричной тем, что в ней каждая двоичная тетрада может принимать только значения 0, 1, 2, 3, 4, 5, 6, 7, 8 или 9. Перевод двоично-десятичного кода в двоичный осуществляется так же, как и перевод шестнадцатеричного числа. Однако перевод двоичного числа в двоично-десятичное отличается от его перевода в шестнадцате-ричное, поскольку значения тетрад двоичного числа могут быть равны десятичным числам от 10 до 15. Подобные тетрады не предусматриваются двоично-десятичным кодом и называются псевдотетрадами. Для исключения псевдотетрад осуществляют специальные операции по преобразованию двоичного кода в двоично-десятичный.

Двоично-десятичный код часто называют кодом 8421, в котором цифры 8, 4, 2 и 1 обозначают веса значащих двоичных цифр в коде (тетраде). Он применяется для представления входной, выходной и внутренней (для ЭВМ серии ЕС) информации.

РЕГИСТРЫ

Регистры — это устройства, которые предназначены для приема, хранения и передачи информации, представленной в виде двоичного кода (слова). Каждому разряду двоичного кода соответствует определенный разряд (ячейка памяти) регистра. С помощью регистров можно выполнять некоторые логические операции (поразрядное логическое сложение, умножение и др.), а также осуществлять операции преобразования информации из одного вида в другой (например, преобразовывать последовательный код в параллельный и т. п.).

Регистр представляет собой совокупность определенным образом соединенных триггерных ячеек с устройством управления входными и выходными сигналами. Число используемых в регистре триггеров определяет его разрядность. Каждый триггер регистра может иметь прямой и инверсный выходы, что позволяет снять записанный в нем код в прямом или инверсном виде.

Важнейшим признаком классификации регистров является способ ввода — вывода информации и характер представления вводимой и выводимой информации.

По способу ввода и вывода (приема и передачи) информации регистры подразделяются на параллельные, последовательные и параллельно-последовательные.

По характеру представления вводимой и выводимой информации регистры делят на однофазные и парафазные. В однофазных регистрах информация вводится в прямом или обратном (инверсном) кодах, а в парафазном — одновременно в прямом и обратном. Вывод информации из регистров обоих типов может осуществляться как в прямом, так и в обратном кодах.

Регистры можно классифицировать также по числу тактов управления при записи и по виду выполняемых операций над словами.

По числу тактов управления регистры подразделяются на однотактные, двухтактные и многотактные. Число тактов определяется типом используемых в регистре триггеров.

По виду выполняемых операций над словами различают регистры для приема, передачи и сдвига информации.

Параллельные регистры.В параллельных регистрах запись информации (слова) осуществляется параллельным кодом, т. е. одновременно во все разряды регистра. Записанная информация может многократно счнтываться и храниться в регистре сколь угодно длительное время. Поэтому такие регистры называют регистрами п ам яти.

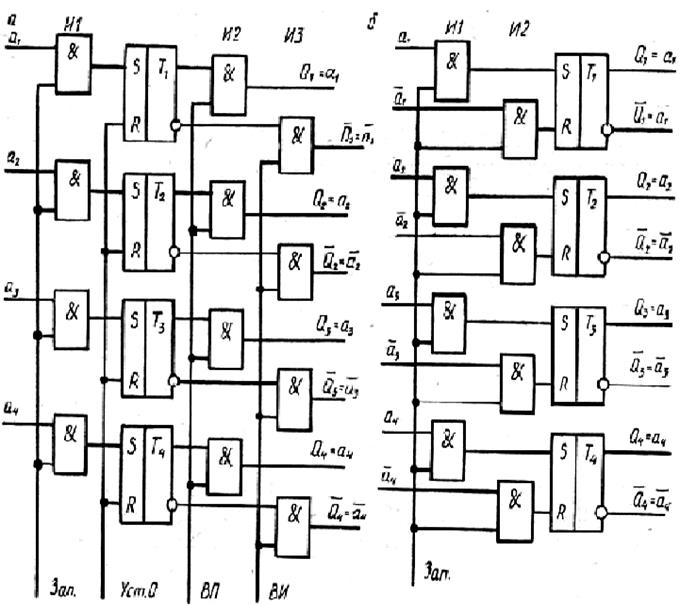

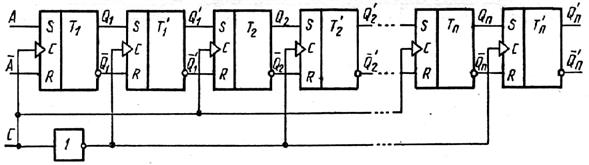

На рис. 13.1, а приведена схема четырехразрядного параллельного однофазного регистра на RS-триггерах.

Рис. 13.1. Схемы однофазного (а) и парафазного (6) параллельных регистров

Управление приемом (записью) и выдачей (считыванием) информации осуществляется соответственно элементами И1 и И2, ИЗ. Входы a1, а2, a3 и а4 соответствуют разрядам записываемого слова (числа).

Перед записью все триггеры регистра устанавливают в нулевое состояние подачей импульса Уст. 0на входы R. Запись информации a1... а4 в регистр осуществляется при поступлении импульса записи на шину Зап. При этом на выходах элементов И1 образуются сигналы установки триггеров в состояние 1 только в тех разрядах, в которых аi = 1. Остальные триггеры остаются в нулевом состоянии. Записанный в регистр код выдается в прямом (через элементы И2) или инверсном (через элементы ИЗ) виде при поступлении на входы ЛЭ И2 или ЛЭ ИЗ соответственно импульсов ВП или ВИ. Информация о записанном коде сохраняется в регистре до прихода следующего импульса Уст. 0.

Недостаток рассмотренного параллельного регистра заключается в том, что требуется время для его обнуления перед записью новой информации. Это снижает быстродействие регистра. Для увеличения быстродействия применяют парафазную запись информации. Парафазный регистр можно получить из однофазного, преобразовав устройство управления записью (рис. 13.1, б).Записываемое слово представляется в прямом (а1а2а3а4) и инверсном (а1а2а3а4) кодах и подается на входы элементов И1 и И2 соответственно. Запись в регистр производится при поступлении сигналов записи на шину Зап. При этом на входы S триггеров поступают прямые, а на входы R — инверсные значения разрядов записываемого слова, которые устанавливают триггеры в нужные состояния независимо от исходных состояний. Выдача информации осуществляется так же, как и в однофазном.

Недостаток рассмотренного параллельного регистра заключается в том, что требуется время для его обнуления перед записью новой информации. Это снижает быстродействие регистра. Для увеличения быстродействия применяют парафазную запись информации. Парафазный регистр можно получить из однофазного, преобразовав устройство управления записью (рис. 13.1, б).Записываемое слово представляется в прямом (а1а2а3а4) и инверсном (а1а2а3а4) кодах и подается на входы элементов И1 и И2 соответственно. Запись в регистр производится при поступлении сигналов записи на шину Зап. При этом на входы S триггеров поступают прямые, а на входы R — инверсные значения разрядов записываемого слова, которые устанавливают триггеры в нужные состояния независимо от исходных состояний. Выдача информации осуществляется так же, как и в однофазном.

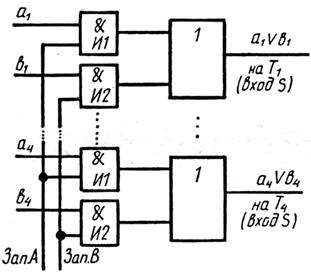

Рис. 13.2. Схема устройства управления записью двухкапналынго регистра

Рис. 13.3. Схема двухканалыюго n-разрядного регистра

Регистр, показанный на рис. 13.1, а, служит для записи, хранения и передачи одного слова A (а1а2а3а4)и является одноканальным. Путем изменения устройства управления его можно преобразовать в многоканальный. На рис. 13.2 показано устройство управления записью в регистр двух слов А (а1а2а3а4) и В (а1а2а3а4).Разряды слова А подаются по первому каналу через элементы И1, а слова В — по второму каналу через элементы И2. Запись по каналу А производится импульсом Зап. А, а по каналу В — импульсом Зап. В. При поступлении импульса записи на вход устройства управления значения разрядов числа А или В передаются через элементы И1 или И2 на входы ЛЭ ИЛИ, а с выходов элементов ИЛИ поступают на входы S триггеров соответствующих разрядов регистра. Считывание информации осуществляется так же, как и в одноканальном регистре.

Для построения регистров широко применяются D-триггеры, позволяющие уменьшать количество элементов. На рис. 13.3 приведена схема п-разрядного параллельного двухканального однофазного регистра (схема управления процессом считывания не приведена), выполненного на однофазных D-триггерах. Импульс Ту, поданный на вход Уст. 0, устанавливает в нуль все разряды регистра. Запись числа A (а1 ... ап) производится тактовым импульсом Та,поданным на вход Зап. А. При этом на выходах элементов И2 устанавливаются уровни а1 ... ап,которые через элементы ИЛИ передаются на выходы соответствующих D-триггеров.

Для построения регистров широко применяются D-триггеры, позволяющие уменьшать количество элементов. На рис. 13.3 приведена схема п-разрядного параллельного двухканального однофазного регистра (схема управления процессом считывания не приведена), выполненного на однофазных D-триггерах. Импульс Ту, поданный на вход Уст. 0, устанавливает в нуль все разряды регистра. Запись числа A (а1 ... ап) производится тактовым импульсом Та,поданным на вход Зап. А. При этом на выходах элементов И2 устанавливаются уровни а1 ... ап,которые через элементы ИЛИ передаются на выходы соответствующих D-триггеров.

Аналогичным образом производится запись числа В (b1 ... bп) при подаче тактового импульса на вход Зап. В.

Последовательные регистры.Наряду с записью и хранением информации последовательные регистры позволяют осуществить логическую операцию сдвига кода записанного числа на любое количество разрядов. Поэтому последовательные регистры называют также сдвигающими регистрами, или регистрами сдвига.

Сдвиг кода записанного числа в регистре применяется при выполнении операций умножения и деления. Так, например, сдвиг кода 0100 (числа 4) на один разряд влево дает код 1000 (число 8), что соответствует умножению на 21 =2. Сдвиг этого же кода 0100 на один разряд вправо дает код 0010 (число 2), что равносильно делению на 21 = 2.

Помимо выполнения операций умножения и деления, сдвигающие регистры применяются для преобразования параллельного кода в последовательный и наоборот, а также для построения счетчиков импульсов.

Последовательный регистр состоит из последовательно соединенных триггеров. Под действием тактовых импульсов состояние каждого триггера передается последующему, что равносильно сдвигу кода. В зависимости от числа последовательностей тактовых импульсов, осуществляющих сдвиг кода, сдвигающие регистры бывают однотактными, двух-, трех- и четырехтактными (в общем случае многотактными).

Триггеры сдвигающего регистра должны обладать свойствами запоминания. При использовании в сдвигающем регистре простых RS-триггеров каждый разряд, кроме основного, содержит дополнительный, триггер, используемый для промежуточного запоминания информации. Структура такого регистра показана на рис. 13.4.

Рис. 13.4. Схема последовательного регистра на синхронных RS-триггерах

Триггеры Т1, Т2, ..., Тnобразуют основной регистр, а триггеры Т’1, Т’2, ..., Т’n — дополнительный. Синхронизирующие импульсы С подаются одновременно на все разряды основного регистра и через ЛЭ НЕ на все разряды дополнительного регистра.

Запись информации (числа А) осуществляется последовательным парафазным кодом, поступающим на вход первого триггера основного регистра. Перед записью триггеры основного и дополнительного регистров устанавливаются в нулевое состояние подачей на синхронизирующий вход п импульсов при действии на прямом информационном входе нулевого сигнала. При этом первый синхронизирующий импульс С1устанавливает в нулевое состояние триггер Т1. Поскольку запись информации на триггеры дополнительного регистра при этом запрещена, не изменяются и состояния остальных триггеров (кроме первого) основного регистра. После окончания действия синхронизирующего импульса С1логический 0 с выхода Т1переписывается в дополнительный триггер Т’1.

Второй синхронизирующий импульс C2подтверждает нулевое состояние триггера Т1 и разрешает запись логического 0 с дополнительного триггера Т’1в триггер второго разряда Т2. После окончания действия импульса С2 логический 0 с триггера Т2переписывается в триггер Т’2. Третий синхронизирующий импульс С3 устанавливает в нулевое состояние триггер Т3, которое передается триггеру Т’3по окончании действия синхронизирующего импульса С3, и т. д.

Аналогичным образом осуществляется запись в регистр числа А. Разница состоит лишь в том, что состояние триггера Т1будет определяться значениями сигналов А и А на его входе во время действия синхронизирующих импульсов С. Записанный в регистр код может быть сдвинут вправо на один или несколько разрядов подачей соответствующего числа импульсов на вход С.

Аналогичным образом осуществляется запись в регистр числа А. Разница состоит лишь в том, что состояние триггера Т1будет определяться значениями сигналов А и А на его входе во время действия синхронизирующих импульсов С. Записанный в регистр код может быть сдвинут вправо на один или несколько разрядов подачей соответствующего числа импульсов на вход С.

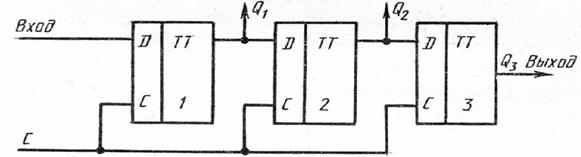

На рис. 13.5 показана схема последовательного сдвигающего регистра на двухступенчатых синхронных D-триггерах, имеющего три разряда.

Рис. 13.5. Схема трехразрядного последовательного регистра на D-триггерах

Запись информации в регистр осуществляется последовательным однофазным кодом, разряды которого поступают на вход первого триггера к моментам появления синхронизирующих импульсов на входе С. Этими же импульсами осуществляется и сдвиг записанного кода вправо. Во время действия синхронизирующего импульса на первые ступени второго и третьего триггеров переписываются значения состояния первого и второго D-триггеров, а на первую ступень первого D-триггера — значение информации, действующей на его входе. В паузах между синхронизирующими импульсами происходит изменение состояний вторых ступеней триггеров.

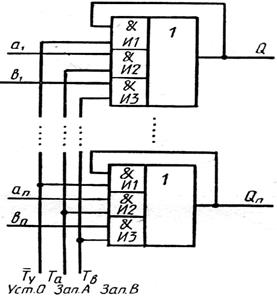

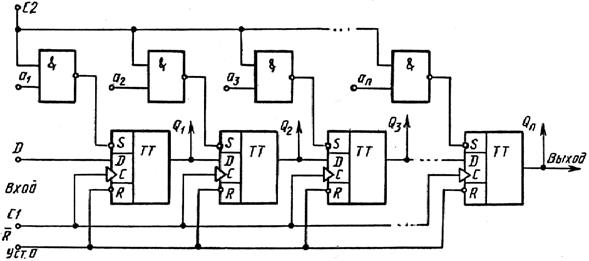

Параллельно-последовательные регистры.Параллельно-последовательный регистр на D-триггерах (рис. 13.6) позволяет осуществлять преобразование параллельного кода в последовательный и наоборот. Двухступенчатые D-триггеры имеют инверсные входы S и R для асинхронной установки нуля (входы R)и для записи n-разрядного числа A (a1, a2, ..., аn)в регистр параллельным кодом (входы S). Параллельная запись числа во все разряды регистра осуществляется импульсом С2 = 1. При этом

Параллельно-последовательные регистры.Параллельно-последовательный регистр на D-триггерах (рис. 13.6) позволяет осуществлять преобразование параллельного кода в последовательный и наоборот. Двухступенчатые D-триггеры имеют инверсные входы S и R для асинхронной установки нуля (входы R)и для записи n-разрядного числа A (a1, a2, ..., аn)в регистр параллельным кодом (входы S). Параллельная запись числа во все разряды регистра осуществляется импульсом С2 = 1. При этом

Рис. 13.6. Схема параллельно-последовательного регистра на D-триггерах

на выходах ЛЭ И образуются значения a1, a2, ..., аn,которые поступают на асинхронные входы S D-триггеров регистра и устанавливают их в состояния a1, a2, ..., аn. Преобразование параллельного кода в последовательный осуществляется подачей серии импульсов на вход С1. Первый импульс на входе С1 устанавливает каждый триггер в состояние, в котором находился до этого каждый предыдущий триггер. Если D = 0, то первый триггер после первого импульса на входе С1 установится в нулевое состояние. Происходит, таким образом, сдвиг записанного кода на один разряд вправо. Второй импульс на входе С1 вызывает сдвиг числа вправо еще на один разряд, а в состоянии логического нуля окажутся уже первый и второй разряды и т. д. Импульсами, поступающими на вход С1, записанный в регистр код как бы выталкивается поразрядно, а освобождающиеся разряды устанавливаются в нулевое состояние.

на выходах ЛЭ И образуются значения a1, a2, ..., аn,которые поступают на асинхронные входы S D-триггеров регистра и устанавливают их в состояния a1, a2, ..., аn. Преобразование параллельного кода в последовательный осуществляется подачей серии импульсов на вход С1. Первый импульс на входе С1 устанавливает каждый триггер в состояние, в котором находился до этого каждый предыдущий триггер. Если D = 0, то первый триггер после первого импульса на входе С1 установится в нулевое состояние. Происходит, таким образом, сдвиг записанного кода на один разряд вправо. Второй импульс на входе С1 вызывает сдвиг числа вправо еще на один разряд, а в состоянии логического нуля окажутся уже первый и второй разряды и т. д. Импульсами, поступающими на вход С1, записанный в регистр код как бы выталкивается поразрядно, а освобождающиеся разряды устанавливаются в нулевое состояние.

В данный регистр можно осуществить запись числа последовательным кодом. Последовательный код записываемого числа подается на вход D и импульсами, поступающими на вход С1, «проталкивается» в регистр. Через выходы Q1,Q2, ..., Qn число, записанное в регистр последовательным кодом, может быть считано прямым параллельным кодом.

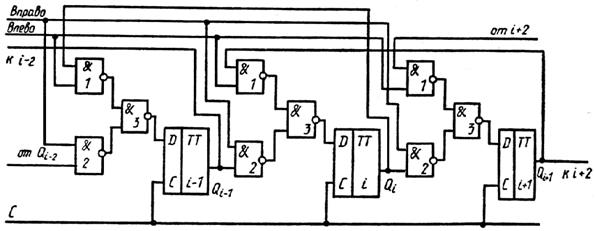

Реверсивные регистры.Регистры, которые позволяют осуществлять сдвиг записанного вних кода вправо или влево, называют реверсивными (рис. 13.7).

Реверсивный регистр отличается от сдвигающего (рис. 13.5) наличием перед каждой ячейкой устройства управления, выполненного на трех двухвходовых элементах И — НЕ.

Рис. 13.7. Фрагмент схемы реверсивного регистра сдвига

Для сдвига вправо необходимо одновременно с поступлением синхронизирующего импульса на вход С подать импульс на шину Вправо. При этом на входы D каждого последующего триггера поступает информация с выхода триггера предыдущего разряда (через ЛЭ И2 и ИЗ), которая будет переписана во вторую ступень каждого принимающего триггера после окончания действия импульса на входе С. Для сдвига последовательного кода влево одновременно с синхронизирующим импульсом С подается импульс на шину Влево. В этом случае на D-вход первой ступени каждого триггера поступает информация о состоянии последующего триггера (через ЛЭ И1 и ИЗ), которая переписывается во вторую ступень после окончания синхронизирующего импульса.