Параллельный регистр (пример 4 разрядного регистра на d-триггере)

В параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения выхода или приема, то есть цепи управления.

Сдвигающий регистр. (Пример 4 разрядного регистра на d-триггере).

Регистры сдвига представляют собой цепочку последовательно включённых D-триггеров или RS- и JK-триггеров, включённых в режим D-триггера. Появление импульса на тактовом входе регистра сдвига вызывает перемещение записанной в нём информации на один разряд вправо или влево. Как и другие регистры, регистры сдвига используются для записи, хранения и выдачи информации, но основным их назначением является преобразование последовательного кода в параллельный или параллельного в последовательный.

Схема 4-разрядного регистра сдвига приведена на рисунке. Схема работает следующим образом. Благодаря тому, что выход предыдущего разряда соединён со входом «D» последующего, каждый тактовый импульс устанавливает последующий триггер в состояние, в котором до этого находился предыдущий. Так осуществляется сдвиг информации вправо.

4-разрядный регистр сдвига

Вход «D» первого триггера служит для приёма в регистр входной информации DI в виде последовательного кода. С каждым тактовым импульсом на этот вход должен подаваться код нового разряда входной информации.

Запись параллельного кода информации может быть произведена через нетактируемые установочные входы  триггеров (на рисунке 55 не показаны).

триггеров (на рисунке 55 не показаны).

С выхода «Q4» последнего триггера снимается последовательный выходной код. Код на этом выходе регистра появляется с задержкой относительно входного последовательного кода на число периодов тактовых импульсов, равное числу разрядов регистра.

Параллельный выходной код можно снять с выходов Q1…Q4 всех триггеров регистра сдвига, снабдив их выходными ключами, подобными выходным ключам параллельного.

Сумматоры. Параллельного.

Параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование.

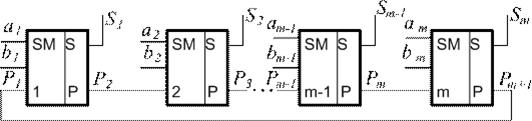

Параллельный сумматор в простейшем случае представляет собой n одноразрядных сумматоров, последовательно (от младших разрядов к старшим) соединённых цепями переноса. Однако такая схема сумматора характеризуется сравнительно невысоким быстродействием, так как формирование сигналов суммы и переноса в каждом i-ом разряде производится лишь после того, как поступит сигнал переноса с (i-1)-го разряда. Таким образом, быстродействие сумматора определяется временем распространения сигнала по цепи переноса. Уменьшение этого времени — основная задача при построении параллельных сумматоров.

При параллельном способе сложения необходимо иметь отдельные одноразрядные сумматоры для каждого разряда чисел. Параллельный сумматор может быть составлен из одноразрядных сумматоров путем соединения выхода, на котором получается сигнал переноса данного разряда, со входом для сигнала переноса соседнего, более старшего разряда. В зависимости от типа используемых одноразрядных сумматоров параллельные сумматоры могут быть комбинационными, накапливающими и комбинационно - накапливающими.

Простейшим является параллельный комбинационный сумматор с последовательным переносом, схема которого приведена на рис. 12.7:

Рис. 12.7

Здесь сигнал переноса, который возникает в каком либо разряде, распространяется к старшим разрядам по цепочке сумматоров, т.е. в таком сумматоре цепь переноса получается последовательной. Поэтому время сложения двух m-разрядных чисел будет равно m×tзр, где tзр – время задержки сигнала в цепях формирования переноса одноразрядного сумматора.

Если на таком сумматоре числа А и В складываются в обратном коде, то в схеме добавляется цепь циклического переноса, связывающая выход переноса старшего (знакового) разряда со входом переноса младшего разряда. Недостатком рассмотренного сумматора является его сравнительно низкое быстродействие. Для увеличения быстродействия в сумматорах применяют сквозной, одновременный или групповой переносы.

23. Сумматоры. Накапливающего (объяснить).

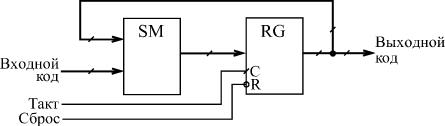

Первая схема известна как накапливающий сумматор, применяющийся, например, в цифровых генераторах аналоговых сигналов. В самом названии схемы отражена ее функция: она суммирует и накапливает результат. Накапливающий сумматор (рис. 8.7) состоит из сумматора и выходного регистра, охваченных обратной связью.

Рис. 8.7. Структура накапливающего сумматора

То есть на один вход сумматора подается код с выходов регистра, а на другой вход - входной код. В результате с каждым следующим фронтом тактового сигнала в регистр записывается код суммы входного кода с предыдущим содержимым регистра, с предыдущей суммой. Например, если входной код равен 3, а в регистре записан код 6, то в следующем такте в регистр будет записан код 9 (то есть 6 + 3), в следующем такте - код 12 (то есть 9 + 3) и т.д. Получается, что на выходе накапливающего сумматора формируется равномерно увеличивающийся двоичный код, и шаг этого увеличения можно менять. В данном случае удобно применять регистр со сбросом, например, ИР35.

Отметим три особенности накапливающего сумматора.

Во-первых, когда выходной код достигает максимальной величины (становится больше 2n, где n - количество разрядов регистра), происходит переполнение схемы и возобновление ее работы с минимальных значений кода. Однако совсем не обязательно в следующем цикле работы будут повторены те же значения кода, что и в предыдущем. Например, пусть n равняется 4, то есть максимальное число на выходе регистра равно 1111 в двоичном коде или 15 в десятичном коде. Пусть входной код равен 3. Тогда, после начального сброса регистра, выходной код будет нарастать так: 0, 3, 6, 9, 12, 15, 2, 5, 8, 11, 14, 1, 4, .… Это происходит потому, что суммирование чисел 15 и 3 даст 18 или, в двоичном коде, 10010, а так как мы работаем только с младшими четырьмя разрядами, у нас получится 0010 или 2.

Во-вторых, особенность накапливающего сумматора состоит в том, что при больших значениях входного кода (больших половины максимально возможной величины) он может рассматриваться как накапливающий вычитатель. Пусть, например, входной код 4-разрядного сумматора равен 15 (1111 в двоичном коде), а в регистре записано число 13 (1011 в двоичном коде). В следующем такте в регистр запишется сумма 1101 + 1111 = 11100, а без старшего разряда - 1100, то есть 12. То есть выходной код уменьшился на единицу.

Наконец, в-третьих, совсем не обязательно шаг нарастания выходного кода накапливающего сумматора должен быть целым числом (то есть 0, 1, 2, 3, ...). Если в качестве выходного кода берутся не все, а только старшие разряды регистра, то шаг нарастания вполне может быть дробным, например, 0,5, 1,25 или 3,75. Не вошедшие в выходной код разряды будут иметь вес 2-1 (то есть 0,5), 2-2 (то есть 0,25) и т.д. Правда результат суммирования в выходном коде будет представлен с точностью до целых чисел. При этом возможна ситуация, когда в течение нескольких тактов код на выходе не меняется, например, при входном коде 0,5 выходной код будет меняться один раз на два такта, а при входном коде 0,25 - один раз на четыре такта.

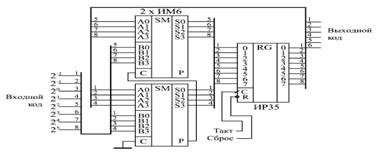

Рис. 8.8. Накапливающий сумматор

На рис. 8.8 показана схема 8-разрядного накапливающего сумматора на двух микросхемах сумматоров ИМ6 и одном регистре ИР35. В качестве выходного кода используется только 6 старших разрядов с выхода регистра, поэтому задание шага приращения возможно с точностью до 0,25. Максимально возможная частота тактового сигнала может быть определена по формуле T > tSM + tRG, где Т - период тактового сигнала, tSM - задержка 8-разрядного сумматора, а tRG - задержка регистра.