Схема кодопреобразователя

Кафедра цифровой и вычислительной техники и информатики

Курсовая работа

По дисциплине «Вычислительная техника и информационные технологии»

Вариант №1.

Выполнили: Студенты группы МТ-91

Любомирский Ю.А.

Суховерхов. А.

Руководитель: Неелова О.Л.

Санкт-Петербург

Цель работы.

Целью данной работы является практическое применение знаний, полученных по дисциплине «Вычислительная техника и информационные технологии»

Задание на курсовую работу.

Построить устройство, позволяющее получать арифметическую сумму двух 4-разрядных чисел, записанных в регистры R1 и R2 с внешнего порта. Сумма записывается в регистр R3. Запись в регистры данных с порта и сложение производится по сформированным командам. Команды должны содержать биты управления адресами порта и сумматора, а также адреса всех регистров. Устройство, подающее команды, описать как схему кодопреобразователя, управляемую счетчиком. Каждая команда ставится в соответствие с текущим состоянием счетчика. Все устройство работает со внутреннего генератора через понижающий счетчик с частотой 1Гц. Состояние регистров и бита переноса выводить на сегментные индикаторы макета. Внешние данные писать с тумблеров макета.

Построение устройства

1. Схема синхронного четырехразрядного регистра:

Программа декодера

library ieee;

use ieee.std_logic_l164.all;

entity dec is

port(

adr_i: in bit_vector (1 downto 0);

data_out: out bit_vector (3 downto 0)

);

end dec;

architecture BBB of dec is

begin

p0: process (adr_i)

begin

case adr_i is

when "00"=>data_out<="0001";

when "01"=>data_out<="0010";

when "10"=>data_out<="0100";

when "11"=>data_out<="1000";

end case;

end process;

end;

Программа 8-ми разрядного регистра

library ieee;

use ieee.std_logic_1164.all;

entity reg8 is

port(

data_i: in std_logic_vector(7 downto 0) ;

clk_i: in std_logic;

ena:in std logic;

ctrl: in std_logic;

data out: out std_logic_vector (7 downto 0)

);

end reg8;

architecture arch of reg8 is

signal regist: std_logic_vector(7 downto 0);

begin

process(clk_i)

begin

if(rising_edge(clk_i)) then

if(ena='1')then

regist <=data_i;

end if;

end if;

end process;

data_out <=regist when ctrl='1' else "00000000";

end arch;

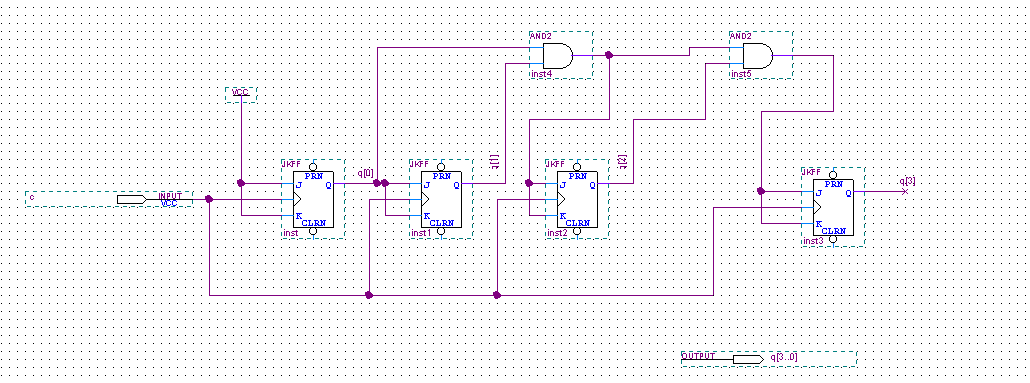

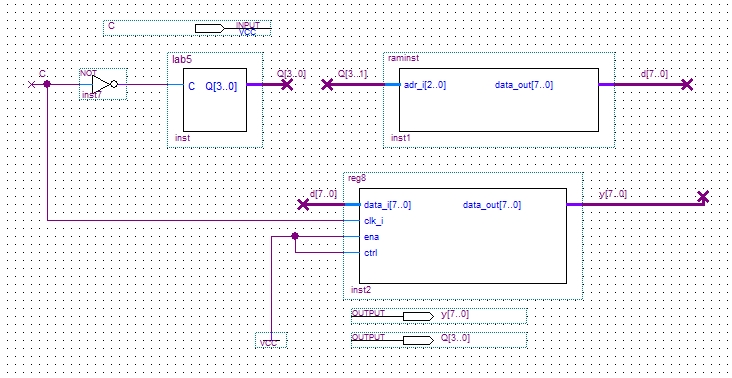

Схема кодопреобразователя

Кодопреобразователь состоит из счётчика, регистра и демультиплексора.

Счетчики – конечные автоматы, служащие для счета импульсов. Основа построения – триггеры переключательного типа. В синхронных счетчиках импульс синхронизации подается одновременно на все триггеры, а обратные связи устанавливаются с выходов на информационные входы. Для синтеза таких счетчиков используются JK-триггеры, так как они имеют возможность переключаться при J=K=1. Регистр – конечный автомат, служащий для хранения или для сдвига информации. Демультиплексор – устройство, распределяющее информацию с единственного входа на один из выходов, адрес которого указан на адресных выходах.

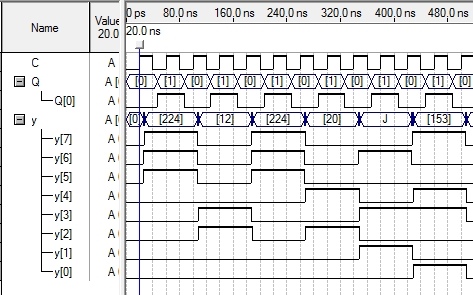

Временные диаграммы кодопреобразователя: