Устройство микросхемы статической памяти

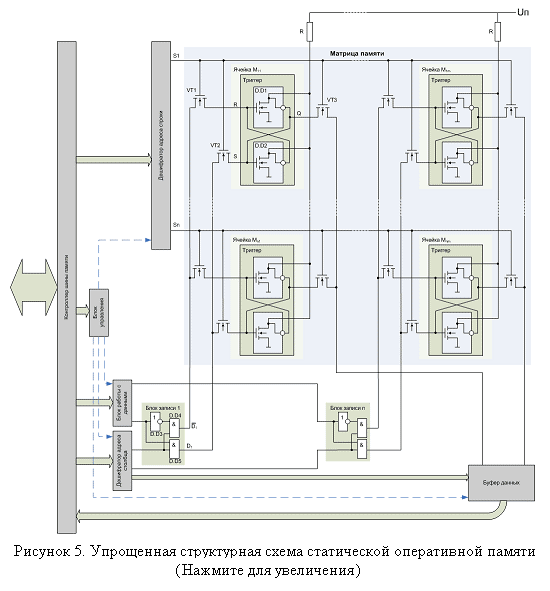

Давайте перейдем к следующему этапу изучения работы статической памяти и рассмотрим ее общую логику работы. Для этого обратимся к упрощенной структурной схеме статической памяти, изображенной на рисунке 5.

Начнем с записи данных в статическую память и рассмотрим случай записи единицы в ячейку М11.

В контроллер шины памяти от контроллера памяти, встроенного в северный мост материнской платы или в процессор, приходит адрес ячейки памяти и данные для записи. Адрес ячейки преобразуется на две составляющие – номер строки и номер столбца. Номер строки передается в «Дешифратор адреса строки», откуда на нужную строку подается напряжение.

Так как мы рассматриваем запись в ячейку М11, то напряжение с дешифратора адреса строки подается на первую строку. В результате, транзисторы VT1, VT2 и VT3 открываются. Аналогичные транзисторы других ячеек памяти, располагающихся в этой строке, также открываются.

Через транзистор VT3 первой ячейки и аналогичные транзисторы других ячеек памяти первой строки пойдет ток, соответствующий состоянию триггеров этих ячеек, в «Буфер данных». Однако «Буфер данных» получаемую информацию будет игнорировать, так как у него нет сигнала от «Блока управления» на сохранение считываемых данных.

Параллельно с подачей напряжения на строку матрицы памяти с «Блока работы с данными» будет выдано напряжение, соответствующее записываемым данным, в «Блоки записи 1 - m», а с «Блока дешифровки адреса столбца» на соответствующие столбцы будет выдано разрешение (напряжение, соответствующее логической единице) на запись данных.

Блоки записи используются для запрета выдачи тока в линии D и  при чтении данных и преобразования из входящих сигналов данных их инвертируемых сигналов для переключения состояния триггеров, в которые необходимо сохранить данные.

при чтении данных и преобразования из входящих сигналов данных их инвертируемых сигналов для переключения состояния триггеров, в которые необходимо сохранить данные.

В нашем случае, запись проводится в ячейку М11, и записывается единица. Соответственно, с «Блока работы с данными» будет выдана логическая единица в «Блок записи 1», и с «Блока дешифровки адреса столбца» будет выдана логическая единица в «Блок записи 1».

Рассмотрим работу «Блока записи 1» при таких входных сигналах. И так, на входе элемента D.D3 будет логическая единица, а на выходе – логический ноль, так как элемент D.D3 – инвертер (логический элемент «НЕ»). Соответственно, на входах элемента D.D4 (логический элемент «И») будут: логический ноль и логическая единица. В результате, на выходе этого элемента будет логический ноль.

На входах элемента D.D5 (логический элемент «И») будут две логические единицы, в результате, на выходе этого элемента будет логический ноль.

Следовательно, на выходе D1 «Блока записи 1» будет напряжение, соответствующее логическому нулю, а на выходе  1 будет напряжение, соответствующее логической единице. Эти напряжения будут поданы на все ячейки памяти первого столбца. Однако у всех ячеек, кроме первой, транзисторы, разрешающие запись, закрыты, а, следовательно, подаваемое напряжение попадет только на триггер первой ячейки и переведет его в состояние хранения единицы.

1 будет напряжение, соответствующее логической единице. Эти напряжения будут поданы на все ячейки памяти первого столбца. Однако у всех ячеек, кроме первой, транзисторы, разрешающие запись, закрыты, а, следовательно, подаваемое напряжение попадет только на триггер первой ячейки и переведет его в состояние хранения единицы.

После изменения состояния триггера первой ячейки напряжение с первой строки снимается, и транзисторы VT1, VT2 и VT3 закрываются, запрещая запись и чтение из ячейки.

При записи нуля в ячейку памяти все происходит по той же схеме, только с «Блока работы с данными» в «Блок записи 1» будет подано напряжение, соответствующее логическому нулю. Это значит, что на выходе D1 «Блока записи 1» будет напряжение, соответствующее логической единице, а на выходе  1 будет напряжение, соответствующее логическому нулю. Эти значения напряжений переведут триггер первой ячейки памяти в состояние хранения нуля.

1 будет напряжение, соответствующее логическому нулю. Эти значения напряжений переведут триггер первой ячейки памяти в состояние хранения нуля.

В установленном состоянии триггер первой ячейки останется, пока на него будет подаваться питание Uп.

Чтение записи происходит еще проще. От контроллера памяти приходит адрес ячеек памяти, с которых требуется считать данные, и команда на чтение.

В результате, адрес преобразуется в номер строки, и на соответствующую строку будет подано напряжение, которое откроет транзисторы разрешения/запрета чтения/записи.

Рассмотрим случай, когда данные считываются из первой ячейки. В этом случае напряжение с «Дешифратора адреса строки» будет подано в первую строку, что приведет к открытию транзисторов VT1, VT2 и VT3 ячейки М11 и всех остальных ячеек первой строки. Ток с триггера первой ячейки, через транзистор VT1, беспрепятственно пройдет в «Буфер данных». То же самое произойдет с остальными ячейками первой строки. Считанные с ячеек памяти первой строки данные сохранятся в «Буфере данных».

После того, как информация в «Буфере данных» будет сохранена, «Дешифратор адреса столбцов» выдаст номера столбцов, данные с которых необходимо считать, в «Буфер данных». Соответствующие данные будут переданы из микросхемы памяти в контроллер памяти, располагающийся в материнской плате или непосредственно в процессоре.

Для того чтобы при чтении данных не происходила запись в эти же ячейки, ведь транзисторы, разрешающие запись, открыты, блоки записи выдают в линии D и  всех столбцов матрицы памяти напряжение, соответствующее логическому нулю. Это происходит из-за того, что с блока дешифровки адреса столбцов выдается напряжение, соответствующее логическому нулю на все «Блоки записи».

всех столбцов матрицы памяти напряжение, соответствующее логическому нулю. Это происходит из-за того, что с блока дешифровки адреса столбцов выдается напряжение, соответствующее логическому нулю на все «Блоки записи».

Как видите, работа статической памяти очень похожа на работу динамической памяти, однако процесс записи и чтения гораздо быстрее, так как не тратится время на заряд и разряд конденсаторов и не требуется регенерация ячеек. Однако необходимо обратить внимание, что рассмотренная нами схема сильно упрощена, и на практике используют гораздо более сложные механизмы записи и чтения из памяти, повышающие надежность и скорость работы статической памяти. Однако описанный выше принцип работы позволяет понять основы функционирования статической памяти, ее недостатки и преимущества. Давайте попробуем сформулировать их (основные недостатки и преимущества).