Дешифраторы (демультиплексоры)

Дешифратором называют преобразователь двоичного n-разрядного кода в унитарный 2n-разрядный код, все разряды которого, за исключением одного, равны единице. Дешифраторы бывают полными и неполными. Для полного дешифратора выполняется условие

N = 2n,

где n – число входов (обычно 2, 3 или 4); N – число выходов. В неполных дешифраторах имеется n входов, но реализуется N < 2n выходов. Так, например, дешифратор, имеющий 4 входа и 10 выходов, будет неполным, а дешифратор, имеющий 2 входа и 4 выхода, будет полным.

На рис. 52 изображен дешифратор с n = 3.

Рис. 52

На входы x0, x1, x2 можно подать 8 комбинаций логических уровней:

000, 001, …,010, …,111. Схема имеет 8 выходов, на одном из которых формируется низкий потенциал (0), а на остальных – высокий (1). Номер этого единственного выхода, на котором формируется нулевой уровень, соответствует числу N, определяемому состоянием входов следующим образом:

N = 22 · x2 + 21 · x1 + 20 · x0.

В общем виде состояние выходного сигнала yi можно описать следующей системой уравнений:

0, если i = k;

Yi =  1, если i ≠ k;

1, если i ≠ k;

k = 22 · x2 + 21 · x1 + 20 · x0.

Помимо информационных входов x0, x1, x2 дешифраторы обычно имеют дополнительные входы управления Е. Сигналы на этих входах разрешают функционирование дешифратора или переводят его в пассивное (высокоимпедансное) состояние, при котором, независимо от сигналов на информационных входах, на всех выходах устанавливается уровень логической единицы.

Разрешающий вход дешифратора может быть прямым или инверсным.

У дешифратора с прямым разрешающим входом активным уровнем является уровень логической единицы, у дешифраторов с инверсным входом – уровень логического нуля. Дешифратор, представленный на рис. 52, имеет один инверсный вход управления.

Существуют дешифраторы с несколькими входами управления. Для таких дешифраторов функция разрешения S, как правило, представляет собой логическое произведение всех разрешающих сигналов управления. Например, для дешифратора КР555ИД7 с одним прямым входом управления S и двумя инверсными &1 и &2 функция S имеет вид:

E = S·  ·

·  .

.

Мультиплексоры

Мультиплексором называется комбинационная логическая схема, представляющая собой управляемый переключатель, который подключает к выходу один из информационных входов данных. Номер подключаемого входа равен числу, определяемому комбинацией логических уровней на адресных входах. Кроме информационных и адресных входов схемы мультиплексоров содержат вход разрешения, при подаче на который активного уровня “1” мультиплексор переходит в активное состояние. При подаче на вход разрешения пассивного уровня мультиплексор перейдет в пассивное состояние, для которого сигнал на выходе сохраняет постоянное значение не зависимо от значений информационных и адресных входов.

В зависимости от соотношения числа информационных n и числа адресных входов m мультиплексоры делятся на полные и неполные. Если выполняется условие n = 2 m , мультиплексор будет полным. Если это условие не выполняется, т. е. n < 2 m , то мультиплексор будет неполным.

Число информационных входов у мультиплексоров обычно 2, 4, 8 или 16 в 1. На рис. 53 представлен мультиплексор 4  1 с инверсным входом разрешения Е и прямым выходом У.

1 с инверсным входом разрешения Е и прямым выходом У.

Рис. 53

Выражение для выходной функции такого мультиплексора можно записать в виде

y = x0 ·(  ·

·  ) + x1 · (A0 ·

) + x1 · (A0 ·  ) + x2 · (

) + x2 · (  ·A1) + x3(A0 ·A1),

·A1) + x3(A0 ·A1),

где x0 , x1 , x2 , x3 – информационные входы мультиплексора; A0, A1 – адресные входы мультиплексора. В общем случае для полного мультиплексора, имеющего n управляющих (адресных) входов и 2m информационных входов, можно реализовать n входную логическую функцию.

Поскольку каждой комбинации управляющих входов соответствует единственный информационный вход, на него следует подавать требуемое значение логической функции, которое и будет передано на выход мультиплексора.

Микросхемы серий КМОП

Описанные в предыдущем разделе цифровые микросхемы ТТЛ-серий – К155, КР1533, К555 (74, 74LS) – обеспечивают построение самых различных цифровых устройств, работающих на частотах до 80 МГц, однако их существенный недостаток – большая потребляемая мощность. Микросхемы этих серий изготовляются по технологии комплементарных транзисторов структуры металл – диэлектрик – полупроводник (КМДП). В качестве диэлектрика использовали окисел кремния, поэтому сокращенным обозначением этих микросхем было КМОП.

Основная особенность микросхем КМОП – ничтожное потребление тока в статическом режиме – 0,1…100 мкА. При работе на максимальной рабочей частоте потребляемая мощность приближается к потреблению наименее мощных микросхем ТТЛ.

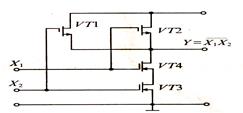

В ИМС, выполненных по технологии КМОП, в качестве базового элемента используются ключевые схемы, построенные на комплементарных МОП – транзисторах. На рис. 54, а приведена схема логического элемента «И – НЕ». Эта схема состоит из двух групп ключей на полевых транзисторах VT1, VT2

p-канальных; VT3, VT4 n-канальных. Каждая группа управляется одним сигналом X1 или X2.

При подаче сигналов X1 = X2 = «1» ключи на транзисторах Т1 и Т2 размыкаются, а ключи Т3 и Т4 замыкаются. В результате сигнал на выходе

Y =

.

.

Применение полевых транзисторов с изолированным затвором обеспечивает высокое входное сопротивление микросхем КМОП. Благодаря малой входной емкости и высокому сопротивлению микросхемы КМОП чувствительны к статическому электричеству. Пробой изоляции под затвором происходит при напряжении около 30 В, в результате транзистор повреждается. Защита входов ИМС КМОП осуществляется с помощью встроенных диодов или стабилитронов, подключенных к линиям питания ИМС.

Достоинством ИМС КМОП являются малая потребляемая мощность и высокая помехозащищенность в сочетании с высоким быстродействием и нагрузочной способностью. Питание таких ИМС производится от источника напряжения +5…+15 В. По сравнению с ИМС ТТЛ микросхемы имеют следующие достоинства:

– малая потребляемая мощность в диапазоне частот до 3 МГц (мощность в статическом режиме не превышает 1 мкВт);

– большой диапазон напряжения питания (от 3 до 15 В);

– очень высокое входное сопротивление (больше 1 Мом);

– большая нагрузочная способность (коэффициент разветвления больше 50).

К недостаткам ИМС КМОП относятся:

– большое время задержки (до 100 нс);

– повышенное выходное сопротивление (до 1 кОм);

– значительный разброс параметров.

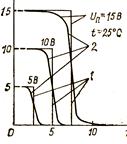

Уровни выходных сигналов зависят от напряжения питания. Уровень логической «1» равен примерно 0,8(2/3)UПИТ, а уровень логического «0» – от 0,3(1/3)UПИТ – 0,3 до 2,5 В.

а) б)

Рис. 54. Схема ЛЭ «ИЛИ – НЕ» (а); передаточная характеристика (б)

Для построения элементов с функцией «ИЛИ – НЕ» транзисторы с каналом р-типа соединяют последовательно, а n-каналом – параллельно. Инвертор КМОП в статическом состоянии ток питания не потребляет, поскольку разомкнуты транзисторы VT1, VT2, либо VT3, VT4, поэтому сквозного тока нет. В этом – замечательное свойство микросхем КМОП: они не потребляют ток питания, если входные сигналы не изменяются. Чем больше частота сигнала, тем больше ток, потребляемый инвертором. Динамический импульс тока потребления складывается из двух частей: во-первых, сквозной ток через VT1 (VT2) и VT3 (VT4), когда один из них «полузакрыт», а другой «полуоткрыт», во-вторых, ток заряда паразитных емкостей.

Сравнив осциллограммы входного напряжения UВХ и импульсов потребляемого тока IПОТ.ДИН, можно сделать вывод, что логический элемент потребляет ток только во время фронта и среза UВХ. Максимальный ток потребления

IПОТ = IПОТ.ДИН будет наблюдаться на такой частоте, когда импульсы тока как бы «слипнутся» (1..3 МГц; импульсы тока следуют в два раза чаще).

Для переключения синхронных микросхем КМОП необходимо, чтобы фронт и срез тактового импульса были бы достаточно крутыми (быстрее, чем 5..15 мкс). Пологий фронт импульса долго держит инвертор в линейном режиме, поэтому течет чрезмерный ток потребления.