Интерфейсы, применение, параметры цифроаналоговых преобразователей

Важную часть цифроаналогового преобразователя составляет цифровой интерфейс, т. е. схемы, обеспечивающие связь управляющих входов ключей с источниками цифровых сигналов. Структура цифрового интерфейса определяет способ подключения ЦАП к источнику входного кода, например, микропроцессору или микроконтроллеру. Свойства цифрового интерфейса непосредственно влияют и на форму сигнала на выходе ЦАП. Так, в случае параллельного интерфейса неодновременность поступления битов входного слова на управляющие входы ключей преобразователя приводит к появлению узких выбросов, «иголок», в выходном сигнале при смене кода.

При управлении ЦАП от цифровых устройств с жесткой логикой управляющие входы ключей ЦАП могут быть непосредственно подключены к выходам 4 1 0 цифровых устройств, поэтому во многих моделях ИМС ЦАП, особенно ранних (572ПА1, 594ПА1,1108ПА1, AD565 и др.), развитая цифровая часть отсутствует. Если же ЦАП входит в состав микропроцессорной системы и получает входной код от шины данных, то он должен быть снабжен цепями, позволяющими адресовать ЦАП, принимать входное слово от шины данных, коммутировать в соответствии с этим словом ключи ЦАП и хранить его до получения следующего слова. Для управления процессом загрузки входного слова ЦАП должен иметь соответствующие управляющие входы и схему управления. В зависимости от способа загрузки входного слова в ЦАП различают преобразователи с последовательным и параллельным интерфейсами входных данных.

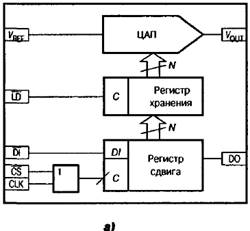

2.1. ЦАП с последовательным интерфейсом Такой преобразователь помимо собственно ЦАП содержит на кристалле дополнительно последовательный регистр загрузки, параллельный регистр хранения (буферный регистр) и управляющую логику (Рис. 10).

Рис. 10. ЦАП с последовательным интерфейсом:

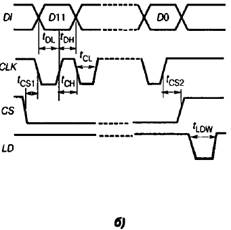

а — функциональная схема, б — временная диаграмма

При активном уровне сигнала CS (в данном случае нулевом) входное слово длины N (равной разрядности ЦАП) загружается по линии D1 в регистр сдвига под управлением тактовой последовательности CLK. После окончания загрузки, выставив активный уровень на линию LD, входное слово записывают в регистр хранения, выходы которого непосредственно управляют ключами ЦАП. Для того чтобы иметь возможность передавать по одной линии данных входные коды в несколько ЦАП, последний разряд регистра сдвига соединяется с выводом D0 ИМС. Этот вывод подключается к входу D1 следующего ЦАП и т. д. Коды входных слов передаются начиная с кода самого последнего преобразователя в этой цепочке.

В качестве примера на Рис. 8.30б представлена временная диаграмма, отражающая процесс загрузки входного слова в ЦАП AD7233. Минимально допустимые значения обозначенных на эпюрах интервалов времени указываются в технической документации на ИМС. Для данной ИМС все они близки к 50 нс.

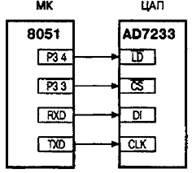

На Рис. 11 приведен вариант схемы подключения преобразователя с последовательным интерфейсом к микроконтроллеру (МК) типа МС551.

Рис. 11. Подключение ЦАП с последовательным

интерфейсом к микроконтроллеру семейства MCS51

На время загрузки входного слова в ЦАП через последовательный порт микроконтроллера, к которому могут быть также подключены и другие приемники, на вход CS (выбор кристалла) подается активный уровень с одной из линий ввода-вывода МК. После окончания загрузки МК меняет уровень на входе CS, как это показано на Рис. 10б, и, выставив активный уровень на входе LD ЦАП, обеспечивает пересылку входного кода из регистра сдвига ЦАП в регистр хранения.

Время загрузки зависит от тактовой частоты МК и обычно составляет единицы микросекунд. В случае если колебания выходного сигнала ЦАП во время загрузки допустимы, вход LD можно соединить с общей точкой схемы. В зависимости от состава схемы управления ЦАП возможна организация двухпроводного последовательного интерфейса (совместимого с интерфейсом 12С) с последовательной передачей данных при каскадно-соединенных линиях данных ЦАП, а также трехпроводного SPI/QSPI, MICROWIRE-совместимого интерфейса с адресацией кристалла так, как это показано на Рис. 7.10, 7.11.