Особенности программирования под CPLD и FPGA

Принципиальные различия заключаются в том, что в CPLD содержатся укрупненные ЛБ(логические блоки) на основе элементов 2И-НЕ, 2ИЛИ-НЕ, а в FPGA в структуре содержатся более компактные ЛБ на основе таблицы истинности, количество ячеек FPGA превышает кол-во ячеек в CPLD на 1-2 порядка. Алгоритмы программирования интегральных схем заключается в переносе конфигурации матрицы соединения на память интегральной схемы. CPLD содержит энергонезависимую память, поэтому при старте системы ее не надо каждый раз загружать, она сохраняется, а в FPGA при включении каждый раз надо заново загружать конфигурацию.

Протокол JTAG. Структура TAP.

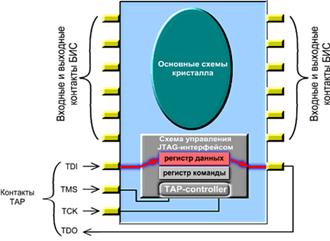

Протокол JTAG создавался для тестирования, так как с ростом степени интеграции БИС, плотности монтажа и появлением многослойных печатных плат, методы диагностики, основанные на подключении к контрольным точкам платы и выводам микосхем, становились все более сложными в использовании и неэффективными. Программирование явилось частным случаем тестирования схемы внутри кристалла. Cтандарт JTAG определяет:

- интерфейс, через который осуществляется обмен тестовыми инструкциями и данными между ведущим устройством и встроенными средствами тестирования (TAP – Test Access Port);

- минимальный набор средств тестирования, встраиваемых в БИС (средства поддержки метода граничного сканирования). В основу стандарта положена идея внедрения в компоненты цифрового устройства средств, обеспечивающих унифицированный подход к решению следующих задач:

1.тестирование связей между интегральными схемами после того, как они были смонтированы на печатной плате или другой основе;

1.тестирование связей между интегральными схемами после того, как они были смонтированы на печатной плате или другой основе;

2.наблюдение за работой компонент без вмешательства в их нормальную работу, или непосредственное управление одним или более компонентом;

3.обеспечение стандартизованного доступа к произвольным средствам самотестирования, встраиваемым в БИС.

В процессе обмена информацией через TAP ведущее устройство воспринимает БИС как сдвиговый регистр, при этом

- TDI – вход сдвигового регистра;

Рис. П1.2. Структура ТАР- TDO – выход сдвигового регистра;

- TCK – сигнал сдвига;

В зависимости от состояния автомата TAP-контроллера в канал может быть включен либо регистр данных, либо регистр команды.

Регистр команды в JTAG-контроллере всегда один.

Регистров данных в JTAG-контроллере может быть сколько угодно. Какой именно регистр данных будет выбран для подключения, как правило, определяется загруженной командой.

TAP-контроллер имеет граф из 16 состояний. Переход из одного состояния в другое зависит от

сигнала TMS.

Протокол JTAG. Структура BSC.

Регистр данных – сдвигающий регистр, состоящий из цепочки ячеек граничного сканирования –BSC (boundary scan cell).Такой регистр называется регистром граничного сканирования (Boundary Scan Register).

Регистр данных – сдвигающий регистр, состоящий из цепочки ячеек граничного сканирования –BSC (boundary scan cell).Такой регистр называется регистром граничного сканирования (Boundary Scan Register).

Вариант схемы отдельной ячейки

34. Протокол JTAG. Режимы работы ячейки граничного сканирования.

Можно выделить несколько режимов в работе ячейки:

- режим сдвига, когда в триггере Т1 по сигналу «захват» сохраняется состояние аналогичного триггера предыдущей ячейки. В этом режиме ведущее устройство последовательно выдвигает текущее состояние ячеек и вдвигает новое;

- режим наблюдения («Sample»). В этом режиме по импульсу текущее состояние вывода фиксируется в триггере и может в дальнейшем быть считанным ведущим устройством. При этом в процессе обмена данные, получаемые от ведущего устройства, фиксируются в триггере. При необходимости, в режиме тестирования (EXTEST) эти данные могут быть выведены на внешний вывод;

- режим тестирования ( EXTEST, – Executing Test ). В этом режиме на выход подается логическое значение, которое находится в триггере T2.