Исследование системы прерываний и таймеров ядра ЦСП семейства C28х

Цель работы: изучить систему прерываний процессоров семейства С28х, а также таймеры ядра ЦСП. Научиться создавать программы, использующие прерывания.

Теоретические сведения

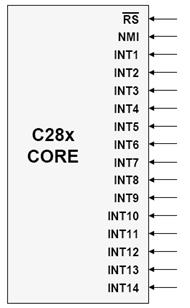

Система прерываний ядра процессора C28x содержит

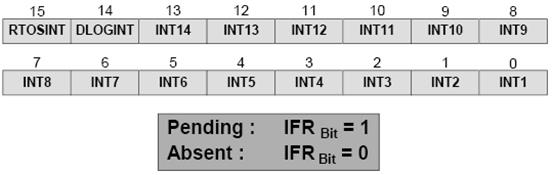

16 линий прерываний (рис. 3.1). Два из них – немаскируемые (RS, NMI). Пользователь не может запретить данные прерывания. Остальные 14 прерываний – маскируемые, т.е. пользователь может разрешить/запретить прерывания от них программно соответственно установкой /сбросом соответствующих бит в регистре IER (Interrupt Enable Register). Регистр IFR (Interrupt Flag Register) – регистр флагов прерываний. При обнаружении прерывания соответствующий бит регистра IFR защелкивается в единичном состоянии, а после обслуживания прерывания – сбрасывается. Так же, когда аппаратное прерывание обслужено, или когда выполнена инструкция INTR, сбрасывается соответствующий бит регистра IER.

|

Рис. 3.1. Линии прерываний ядра C28х

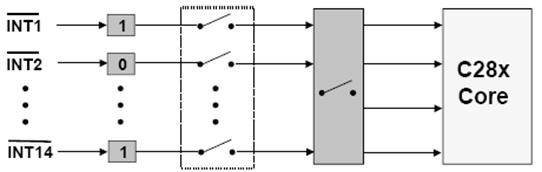

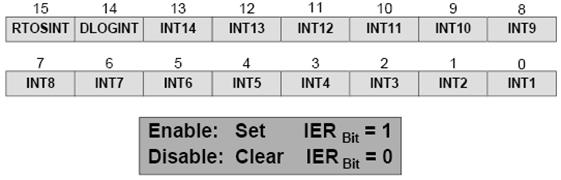

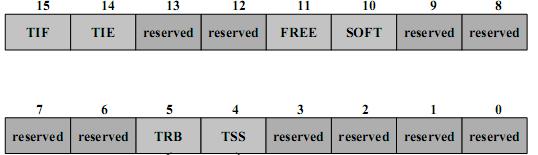

Общая структура прерываний ядра C28x показана на рис. 3.2, а форматы регистров IER и IFR – на рис. 3.3. Следует отметить, что программная установка одного из битов в регистре IFR приведет к обработке данного прерывания ядра таким же образом, как и в случае возникновения соответствующего прерывания. INTM – младший бит в статусном регистре ST1, служит для общего разрешения/запрета маскируемых прерываний ядра.

Рис. 3.2. Общая структура прерываний ядра C28x

|

|

Рис. 3.3. Форматы регистров IER и IFR

Все 16 прерываний однозначно связаны в памяти с таблицей векторов прерываний ядра BROM vector (см. рис. 2.2), содержащей 22-битные адреса (на каждое прерывание – 16 бит в ячейке с младшим адресом и 6 бит в ячейке со старшим адресом), по которым должны располагаться стартовые адреса подпрограмм обработки соответствующих прерываний. Всего данная область памяти содержит 32 таких вектора, т.к. к 16 прерываниям ядра добавлены прерывания DLOGINT, RTOSINT, Illegal (недопустимая инструкция), 12 программных прерываний USER1…USER12 и один резервный вектор (Reserved).

Подача активного сигнала на вход сброса (на вывод /RS) вызовет его сброс и перезапуск программы с начального адреса. Сброс отличается от остальных прерываний тем, что программа затем не возвращается в исходную точку, а регистры сбрасываются в начальное состояние. Сброс может происходить как от внешнего источника, так и от сторожевого таймера (WDT). Сброс внешних схем при сбросе ядра процессора от WDT осуществляется через вывод /RS, который является двунаправленным.

Особенностью ЦСП семейства C28x является возможность запуска программ как из внутренней памяти (микроконтроллерный режим), так и из внешней (микропроцессорный режим). Режим определяется состоянием вывода XMP/MC (см. рис. 2.2). Соответственно, после сброса программа переходит либо к начальному адресу

0x3F FFC0 внутренней памяти (при XMP/MC=0), либо к тому же адресу внешней памяти (при XMP/MC=1), а режим запоминается с помощью флага XMP/MC в регистре XINTCNF2, который может быть впоследствии обработан программно.

После сброса в режиме микроконтроллера запускается служебная программа Bootloader, которая анализирует выводы порта GPIOF (GPIOF2, GPIOF3, GPIOF4 и GPIOF12) и, исходя из комбинации сигналов на них, выполняет один из переходов, перечисленных в табл. 3.1 и условно показанных на рис 3.4.

В отладочном стенде ezDSP2812, используемом в лабораторных работах, программа загружается в H0 SARAM (ОЗУ), а прочие возможные режимы загрузки могут быть заданы при помощи переключателей (джамперов). Следует отметить, что память программ и данных имеют единое адресное пространство, программа может выполняться как из ОЗУ, так и из FLASH, или ПЗУ (ОТР).

Таблица 3.1. Режимы запуска программы Bootloader

| Выводы GPIO | Режим запуска | |||

| F4 | F12 | F3 | F2 | |

| x | x | x | Передать управление FLASH-памяти по адресу 0x3F 7FF6 | |

| Передать управление H0 SARAM-памяти по адресу 0x3F 8000 | ||||

| Передать управление OTP-памяти по адресу 0x3D 7800 | ||||

| x | x | Загрузить программу из внешнего EEPROM во внутреннюю память через SPI-порт | ||

| Загрузить программу во внутреннюю память через SСI-А порт | ||||

| Загрузить программу во внутреннюю память через параллельный порт GPIOВ |

Рис. 3.4. Режимы запуска программы Bootloader

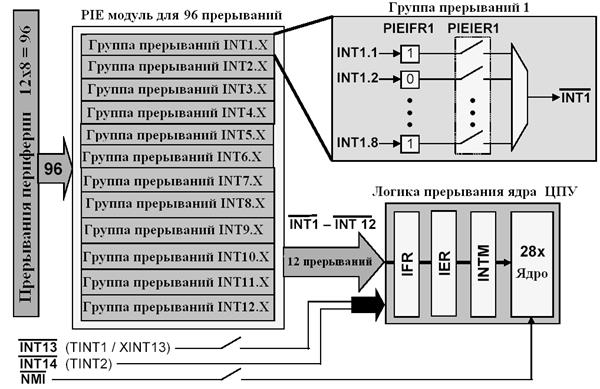

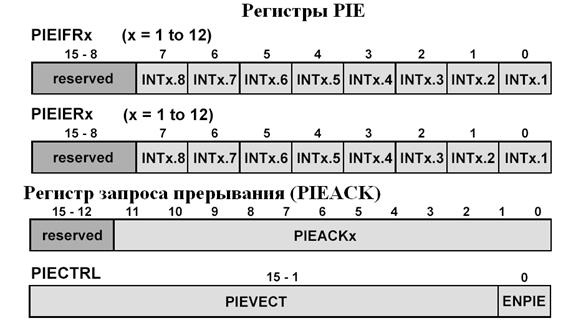

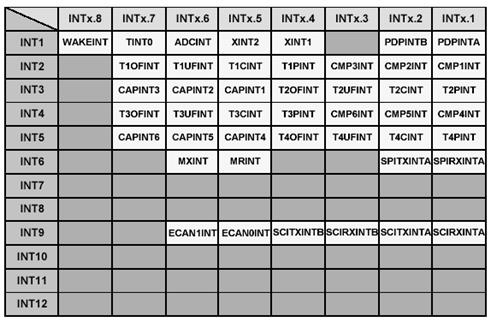

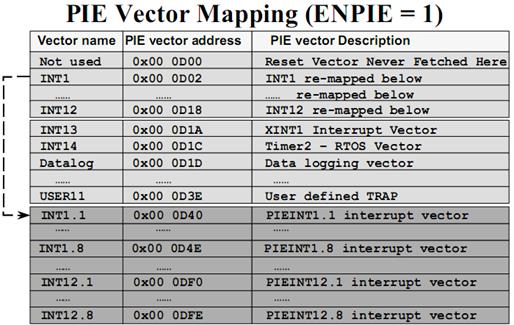

ЦСП имеет большое количество источников прерываний – 96, но только 16 линий прерываний ядра. Для возможности обслуживания всех прерываний для линий INT1…INT12 применяется мультиплексирование (рис. 3.5). Т.к. программный поиск конкретного прерывания в линии при обработке программно занял бы длительное время, то применяется специальный аппаратный модуль – Peripheral Interrupt Expansion (PIE), или расширитель прерываний периферии. При работе с PIE происходит перенос области векторов: каждому из 96 прерываний соответствует свой 32-битный адрес в адресном пространстве – таблице векторов прерываний расширителя (PIE vector, адреса

0x00 D000…0x00 DFFF, см. рис. 2.2 и 3.9). Прерывания сгруппированы по 8 источников на линию (см. рис. 3.8). Для разрешения/запрета каждого прерывания используются биты в регистрах PIEIERx (x может принимать значения от 1 до 12), для индикации прерываний – биты в регистрах PIEIFRx. Соответствующий бит в регистре подтверждения PIEACK (активный уровень – 0) определяет номер активного прерывания для ядра CPU внутри группы. В результате каждая группа мультиплексируется в одно из прерываний ядра INT1…INT12 (рис. 3.6).

Форматы регистров модуля расширителя прерываний PIEIERx и PIEIFRx показаны на рис. 3.7, данные регистры содержат по 8 информационных бит, т.е. по числу прерываний в группе. В регистре PIECTRL биты 15-1 (PIEVECT) показывают адрес в пределах таблицы векторов PIE vector, из которой был извлечен вектор. Младший значащий бит игнорируется и показываются биты адреса от 1 до 15 (т.е. только четные адреса), что позволяет при чтении из регистра однозначно определить, какое прерывание генерировалось. ENPIE – бит разрешения извлечения векторов из таблицы PIE-контроллера. Если ENPIE=1, все вектора извлекаются из таблицы векторов PIE vector, а если ENPIE=0, PIE-контролер запрещен, и вектора извлекаются из таблицы CPU-векторов (BROM vector, см. рис. 2.2).

Рис. 3.3. Модуль прерываний С28х.

Рис. 3.5. Логика работы регистров PIEIFRx, PIEIERx, PIEACKx

Рис. 3.6. Общая структура расширения прерываний ЦСП С28х

Рис. 3.7. Формат регистров модуля расширителя прерываний ЦСП С28х

Таблица векторов прерываний приведена на рис. 3.8.

Примеры векторов прерываний:

- прерывание от встроенного АЦП (ADCINT) – INT1.6;

- прерывание от CPU-таймера 0 (TINT0) – INT1.7.

- прерывание от CPU-таймера 0 (TINT0) – INT1.7.

Рис. 3.8. Таблица источников прерываний в PIE

Рис. 3.9. Таблица векторов прерываний при ENPIE=1: вектор

0x00 0D00 не активен, первичные вектора прерывания ядра по адресам 0x00 0D02 по 0x00 0D1C переадресовываются в область

0x00 0D40…0x00 0DFE с учетом конкретного источника прерывания периферии; вектор извлекается за 9 шагов (машинных циклов ЦСП).

|

Рис. 3.10. Полная процедура обработки прерываний при ENPIE=1: шаг 1 – генерация прерывания от периферии; шаг 2 – установка флага PIEIFRx.y = 1; шаг 3а – проверка одновременного наличия двух условий: PIEIERx.y = 1 и PIEACKx=0; шаг 3б – установка в «1» бита PIEACKx для подтверждения прерывания от группы x;

шаг 4 – формирование импульса прерывания по линии INTx на ядро (PIEACKx продолжает оставаться в единичном состоянии и требует программного сброса для возможности приема прерывания ядром по линии INTx в дальнейшем); шаг 5 – установка флага IFRx = 1;

шаг 6 – проверка условия IERx = 1; шаг 7 – проверка условия

INTM = 1, подготовка адреса возврата и данных к сохранению в стеке; шаг 8 – процессор определяет адрес вектора прерывания в области PIE Vector Mapping (адреса с 0x00 0D02 по 0x00 0D1C); шаг 9 – процессор определяет первичный адрес вектора прерывания в области PIE Vector Mapping с учетом текущего значения регистров PIEIER и PIEIFR (адреса с 0x00 0D40 по 0x00 0DFE).

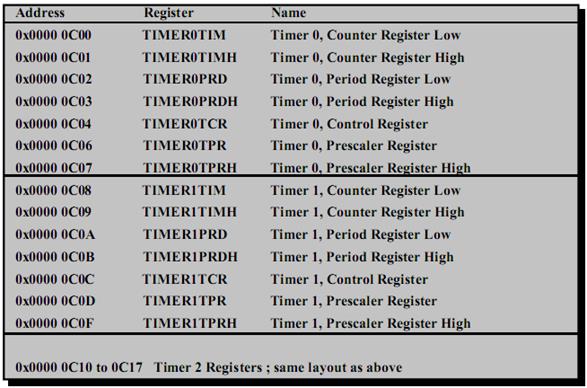

В сигнальных процессорах семейства С28х имеется три

32-битных таймера ядра (CPU timers) с одинаковой структурой. Схема одного таймера приведена на рис. 3.11. Работа таймера разрешается сбросом бита TCR.4. Таймер имеет 16-битный предварительный делитель (прескалер) PSCH: PSC, который формирует счетный импульс вычитания из основного 32-битного счетчика TIMH: TIM. По достижении счетчиком TIMH: TIM нуля формируется сигнал прерывания /TINT, поступающий на ядро. 16-битный регистр TDDRH: TDDR используется для перезагрузки прескалера таймера. Регистр

PRDH: PRD содержит значение основного 32-битного счетчика, перезагружаемое в него при очередном переопустошении. Данная каскадная структура позволяет получить очень широкий диапазон коэффициентов деления частоты: от 22 до 248.

Таймеры 1 и 2, как правило, используются для операционной системы реального времени «DSP/BIOS», в то время как таймер 0 используется для пользовательских приложений. Данные таймеры интегрированы в ЦСП, не следует их путать с таймерами менеджеров событий (EvA и EvB). Необходимо отметить, что после сброса разрешается работа всех трех таймеров ядра.

Рис. 3.11. Схема таймера ядра ЦСП семейства C28x (жирной линией показано прохождение тактового сигнала с делением частоты на выход)

Полный набор программно доступных регистров, относящихся к таймерам ядра, показан на рис. 3.12.

Счетчик-предделитель TIMERxPSC и регистр-делитель TIMERxTDDR программно доступны как один 16-разрядный регистр TIMERxTPR (см. рис. 3.13).

Аналогично, регистры TIMERxPSCH и TIMERxTDDRH, программно представляют собой единый 16-битный регистр TIMERxTPRH.

Рис. 3.12. Регистры таймеров ядра ЦСП семейства C28x

Рис. 3.13. Формат регистров-прескалеров TIMERxTPR (x = 0, 1, 2)

Функции управления каждым из таймеров реализованы в регистрах управления TIMERxTCR, формат которых показан на рис. 3.14.

Сигналы прерываний, формируемые CPU-таймерами, связаны с прерываниями ядра, как показано на рис. 3.15. Прерывание таймера 0 происходит через PIE, а таймеров 1 и 2 – попадают напрямую на ядро через соответствующие линии.

|

Рис. 3.14. Формат регистров управления таймерами ядра (TIMERxTCR)

|

Рис. 3.15. Сигналы прерываний от CPU-таймеров

Ход работы

Использование таймера позволяет более эффективно использовать ресурсы процессора. Наиболее простые задачи для таймера – вызывать на выполнение периодические задачи либо инкрементировать глобальную переменную. Данная переменная будет пропорциональна машинному времени, прошедшему с момента запуска таймера.

Для выполнения данной работы следует использовать файл с программой из предыдущей работы. Но вместо программной задержки в этот раз будем использовать аппаратную задержку, формируемую таймером 0 ядра ЦСП. Данный таймер использует систему расширения прерываний (PIE).

1. Создание нового проекта.

1. Создание нового проекта.

В Code Composer Studio создаем новый проект Lab3.pjt. В поле Project Name записываем название проекта «Lab3». В поле Location указывается путь, по которому будет находиться проект – E:\DspUser\Lab3.

1.1. Открываем файл с программой формирования бегущих огней из лабораторной работы №2 Lab2.с и сохраняем его под именем Lab3.с. Затем добавляем файл Lab3.с в проект: Project → Add files to Project.

Структура исходного текста программы показана на рис. 3.16.

1.2. Добавляем в проект управляющий файл линкера, командные файлы, библиотеки, необходимые внешние программные модули (рекомендуется для исключения ошибок пути к файлам, указанные ниже, копировать в диалоговое окно «Add files to Project»):

C:\tidcs\c28\dsp281x\v100\DSP281x_common\cmd\F2812_EzDSP_RAM_lnk.cmd

C:\tidcs\c28\dsp281x\v100\DSP281x_headers\cmd\DSP281x_Headers_nonBIOS.cmd

C:\CCStudio_v3.3\C2000\cgtools\lib\rts2800_ml.lib

C:\tidcs\c28\dsp281x\v100\DSP281x_headers\source\DSP281x_GlobalVariableDefs.c

C:\tidcs\c28\dsp281x\v100\DSP281x_common\source\DSP281x_PieCtrl.c

C:\tidcs\c28\dsp281x\v100\DSP281x_common\source\DSP281x_PieVect.c

C:\tidcs\c28\dsp281x\v100\DSP281x_common\source\DSP281x_DefaultIsr.c

C:\tidcs\c28\dsp281x\v100\DSP281x_common\source\DSP281x_CpuTimers.c

2. Настройка параметров проекта.

2.1. Включаем в проект заголовочные файлы, для этого выбираем Project → Build Options,в закладке Compiler выбираем Preprocessor и в поле Include Search Path (-i) вводим:

C:\tidcs\C28\dsp281x\v100\DSP281x_headers\include;..\include

2.2. Добавление библиотек и создание стека.

Подключаем Си-библиотеки:

Project → Build Options → Linker → Libraries → Search Path: C:\CCStudio_v3.3\C2000\cgtools\lib

Project → Build Options → Linker → Libraries → Search Path Linker → Incl. Libraries: rts2800_ml.lib

Задаем глубину стека 0х400:

Project → Build Options → Linker → Basic → Stack Size (-stack): 0x400

//##################################################################

// Имя файла: Lab3.c

//

// Описание: С помощью 8 светодиодов, подключенных к линиям

// порта GPIOB0 - GPIOB7, формируются "бегущие огни".

// Направление движения справа - налево и наоборот

//#####################################################################

#include "DSP281x_Device.h" // Включение заголовочного файла

|

void delay_loop(long);

void delay_loop(long);

void Gpio_select(void);

void InitSystem(void);

void InitSystem(void);

void main(void)

{

unsigned int i;

unsigned int LED[8]= {0x0001,0x0002,0x0004,0x0008,

0x0010,0x0020,0x0040,0x0080};

InitSystem(); // Инициализация регистров ЦСП

Gpio_select(); // Инициализация линий ввода/вывода

Gpio_select(); // Инициализация линий ввода/вывода

while(1)

{

for(i=0;i<14;i++)

{

if(i<7) GpioDataRegs.GPBDAT.all = LED[i];

else GpioDataRegs.GPBDAT.all = LED[14-i];

else GpioDataRegs.GPBDAT.all = LED[14-i];

delay_loop(?);

delay_loop(?);

}

}

}

|

//#####################################################################

// Подпрограмма: delay_loop

//

// Описание: Формирование временной задержки горения светодиодов

//#####################################################################

void delay_loop(long end)

void delay_loop(long end)

{

long i;

for (i = 0; i < end; i++);

for (i = 0; i < end; i++);

EALLOW; // Сброс сторожевого таймера

SysCtrlRegs.WDKEY = 0x?;

SysCtrlRegs.WDKEY = 0x?;

EDIS;

}

//#####################################################################

// Подпрограмма: Gpio_select

//

// Описание: Настройка линий порта GPIO B15-8 на ввод, а линий B7-0

// на вывод. Настройка всех линий портов A, D, F, E, G на

// ввод. Запрещение работы входного ограничителя

//#####################################################################

void Gpio_select(void)

{

EALLOW;

GpioMuxRegs.GPAMUX.all = 0x?; // Настройка линий ввода/вывода на

GpioMuxRegs.GPBMUX.all = 0x?; // работу в качестве портов

GpioMuxRegs.GPDMUX.all = 0x?;

GpioMuxRegs.GPFMUX.all = 0x?;

GpioMuxRegs.GPEMUX.all = 0x?;

GpioMuxRegs.GPGMUX.all = 0x?;

GpioMuxRegs.GPADIR.all = 0x?; // Настройка портов А, D, E, F, G на ввод

GpioMuxRegs.GPBDIR.all = 0x?; // Настройка линий 15-8 на ввод,

GpioMuxRegs.GPDDIR.all = 0x?; // а линий 7-0 на вывод

GpioMuxRegs.GPEDIR.all = 0x?;

GpioMuxRegs.GPFDIR.all = 0x?;

GpioMuxRegs.GPGDIR.all = 0x?;

GpioMuxRegs.GPAQUAL.all = 0x?; // Запрещение входного ограничителя

GpioMuxRegs.GPBQUAL.all = 0x?;

GpioMuxRegs.GPDQUAL.all = 0x?;

GpioMuxRegs.GPEQUAL.all = 0x?;

EDIS;

}

//#####################################################################

// Подпрограмма: InitSystem

//

// Описание: Настройка сторожевого таймера на работу,

// предделитель = 1. Выработка сброса сторожевым

// таймером. Внутренняя частота работы ЦСП 150 МГц.

// Запись в предделитель высокоскоростного таймера

// коэффициента деления 2, а в предделитель

// низкоскоростного таймера - 4. Запрещение работы

// периферийных устройств

//#####################################################################

|

void InitSystem(void)

{

EALLOW;

EALLOW;

SysCtrlRegs.WDCR= 0x?; // Разрешение работы сторожевого // таймера, предделитель = 64

// или запрещение работы сторо-

// жевого таймера, предделитель = 1

SysCtrlRegs.SCSR = ?; // Конфигурирование сброса ЦСП от WDT

SysCtrlRegs.PLLCR.bit.DIV = ?;// Настройка блока умножения частоты

SysCtrlRegs.HISPCP.all = 0x?; // Задание значений высокоскоростного SysCtrlRegs.LOSPCP.all = 0x?; // и низкоскоростного предделителей

SysCtrlRegs.PCLKCR.bit.EVAENCLK=?; // Запрещение работы

SysCtrlRegs.PCLKCR.bit.EVBENCLK=?; // периферийных устройств

SysCtrlRegs.PCLKCR.bit.SCIAENCLK=?;

SysCtrlRegs.PCLKCR.bit.SCIBENCLK=?;

SysCtrlRegs.PCLKCR.bit.MCBSPENCLK=?;

SysCtrlRegs.PCLKCR.bit.SPIENCLK=?;

SysCtrlRegs.PCLKCR.bit.ECANENCLK=?;

SysCtrlRegs.PCLKCR.bit.ADCENCLK=?;

EDIS;

}

| |||

|

Рис. 3.16. Структура исходного текста программы

3. Редактирование программы.

3.1. В программе Lab3.c объявляем подпрограмму обработки прерываний от CPU-таймера 0:

interrupt void cpu_timer0_isr(void);

Место вставки – область 1 на рис. 3.16.

Далее в основной программе добавляем вызов подпрограммы:

InitPieCtrl();

Место вставки – область 2 на рис. 3.16.

Данная подпрограмма описана в файле DSP281x_PieCtrl.c, добавленном в проект. Она позволяет очистить флаги и запретить все прерывания, что удобно при написании программ. Просмотреть и проанализировать содержимое данного файла можно, открыв его в другом окне редактора CCS. Аналогичным образом рекомендуется далее ознакомиться и с программами, хранящимися в прочих программных модулях, подключенных к проекту (файлы *.c).

3.2. Непосредственно после вызова подпрограммы

«InitPieCtrl();» добавляем еще один вызов подпрограммы:

InitPieVectTable();

Данная подпрограмма инициализирует область векторов PIE в начальное состояние. Она использует предварительно заданную таблицу прерываний «PieVectTableInit()», которая определена в файле DSP281x_PieVect.c, и копирует эту таблицу в глобальную переменную «PieVectTable», которая связана с областью памяти процессора PIE area. Также, для использования подпрограммы

InitPieVectTable, в проект добавлен файл DSP281x_DefaultIsr.c, который добавляет в проект подпрограммы обработки прерываний.

3.3. Необходимо переопределить имя подпрограммы обработки прерываний от CPU-таймера 0 на нашу подпрограмму. Для этого в основную программу сразу после вызова подпрограммы

«InitPieVectTable();» добавляем вызов следующих подпрограмм:

EALLOW;

PieVectTable.TINT0 = &cpu_timer0_isr;

EDIS;

Здесь EALLOW и EDIS – подпрограммы, используемые соответственно для разрешения и запрета доступа к системным регистрам процессора, а «cpu_timer0_isr» – имя подпрограммы обработки прерываний, описанной в программе ранее.

3.4. Инициализируем CPU-таймер 0. В основную программу необходимо добавить вызов подпрограммы (место вставки – сразу после команд, указанных в п. 3.3):

InitCpuTimers();

Для возможности работы этой подпрограммы в проект добавлен файл DSP281x_CpuTimers.c. После этого таймер будет инициализирован и остановлен.

3.5. Необходимо настроить CPU Timer0 для генерации временных интервалов в 50 мс при тактовой частоте 150 МГц. Для этого сразу после вызова подпрограммы «InitCpuTimers();» добавляем вызов подпрограммы:

ConfigCpuTimer(&CpuTimer0, 150, 50000);

Выполнение данной подпрограммы реализует файл DSP281x_CpuTimers.c.

3.6. Настраиваем прерывания от CPU-таймера 0. Необходимо настроить три уровня прерывания.

Первый уровень – модуль PIE, группа PIEIER1 (т.к. прерывания от CPU-таймера 0 относятся именно к данной группе, см. рис. 3.8):

PieCtrlRegs.PIEIER1.bit.INTx7 = 1;

Второй уровень – разрешение прерываний линии 1 ядра ЦПУ. Для этого необходимо настроить регистр IER (см. рис. 3.2 и 3.3).

IER = 1;

Третий уровень – разрешить глобальные прерывания. Следует разрешить глобальные прерывания, добавив в программу команды:

EINT;

ERTM;

Вызов данных подпрограммы следует произвести сразу вслед за конфигурацией таймера, произведенной в п. 3.6.

3.7. Затем необходимо добавить команду запуска CPU Timer0:

CpuTimer0Regs.TCR.bit.TSS = 0;

3.8. Сразу после основной программы (область 3 на рис. 3.16) необходимо добавить подпрограмму обработки прерываний от CPU-таймера 0 «cpu_timer0_isr». Подпрограмму и обращение к ней мы уже внесли в программу. Теперь необходимо написать саму подпрограмму. Подпрограмма будет иметь общий вид:

interrupt void cpu_timer0_isr(void)

{

…

(текст подпрограммы)

…

}

Подпрограмма должна выполнять следующие действия:

- инкрементировать глобальную переменную «CpuTimer0.InterruptCount», описываемую (начальное значение = 0) в подключаемом файле DSP281x_CpuTimers.c. Данная переменная будет показывать истечение интервала времени 50 мс с момента запуска таймера;

- сбросить в «0» бит 1 регистра PIEACK, что необходимо для разрешения последующих прерываний. Это действие выполняет команда:

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

3.9. После настройки таймера и прерываний корректируем основную программу. Для этого удаляем (либо добавляем в начале строки признак комментария «//») вызов подпрограммы

«delay_loop(?);» (см. область 4 на рис. 3.16). Также удаляем объявление этой подпрограммы (см. область 5 на рис. 3.16), и заключаем в скобки комментария саму подпрограмму

«void delay_loop(long end)». Скобки комментария открываются парой символов «/*» и закрываются парой символов «*/».

Затем необходимо программно реализовать цикл ожидания для формирования задержки длительностью 150 мс, с учетом того, что переменная «CpuTimer0.InterruptCount» однократно инкрементируется в подпрограмме «interrupt void cpu_timer0_isr(void)» каждые 50 мс. Место вставки цикла ожидания – область 4

на рис. 3.16. После цикла ожидания необходимо сбросить переменную «CpuTimer0.InterruptCount» в 0.

3.10. Разрешаем работу Watchdog timer (WDT). См. область 6 на рис. 3.16.

3.11. Добавляем обслуживание WDT. Для этого необходимо последовательно записать в регистр WDKEY коды «0x55» и «0xAA», аналогично тому, как это выполнялось в программе к лабораторной работе № 2 (см. область 7 на рис. 3.16). Отличием является то, что данную процедуру вместе с макросами EALLOW и EDIS необходимо перенести внутрь подпрограммы обработки прерывания от CPU-таймера 0 «interrupt void cpu_timer0_isr(void)». Поскольку прерывание от таймера происходит циклично с периодом

50 мс, сброс ЦСП от WDT не происходит.

4. Компиляция, компоновка и загрузка выходного файла в отладочный модуль ЦСП.

4.1. Компилируем программу: Project → Compile File. При наличии ошибок, исправляем их.

4.2. Компонуем проект: Project → Build. При наличии ошибок, исправляем их.

4.3. Загружаем выходной файл: File → Load Program → Debug\ lab3.out (в случае, если данная функция сконфигурирована для выполнения автоматически, выполнять данный пункт не нужно).

Содержание отчета:

Отчет должен содержать цель работы, краткие теоретические сведения по теме работы, тексты исследуемых программ, результаты их выполнения, выводы.

Контрольные вопросы:

1. Маскируемые и немаскируемые прерывания.

2. Сброс ЦСП.

3. Обработка прерываний ядра ЦСП семейства C28x.

4. Назначение и структура модуля расширения прерываний (PIE) ЦСП семейства C28x.

5. Расположение векторов прерываний ЦСП семейства C28x в режимах ENPIE=0 и ENPIE=1.

6. Процедура обработки прерываний при ENPIE=1.

7. Назначение и структура CPU-таймеров ЦСП семейства C28x.

8. Регистры CPU-таймеров ЦСП семейства C28x.

9. Какие изменения необходимо внести в исходный текст, чтобы программа «бегущие огни» выполнялась с движением «горящих» светодиодов:

- в 1,7 раз быстрее?

- в 2,45 раз медленнее?

10. Какие изменения необходимо внести в исходный текст, чтобы программа «бегущие огни» выполнялась:

- с замедлением движения «горящих» светодиодов в 2 раза на каждом шаге движения?

- с ускорением движения «горящих» светодиодов в 3 раза на каждом шаге движения?

Содержание

| стр | |

| Лабораторная работа № 1. Аппаратные и программные средства отладки eZDSP F2812 и Code Composer Studio …………..……… | |

| Лабораторная работа № 2. Изучение карты памяти, структуры цифровых портов ввода/ вывода и системы тактирования ЦСП TMS320F2812………………………………………………………. | |

| Лабораторная работа № 3. Исследование системы прерываний и таймеров ядра ЦСП семейства C28х ………………….…………. |