Моделирование преобразователя кода

Преобразователи кодов находят широкое применение в аппаратуре передачи данных для защиты передаваемой информации от ошибок, а также для аппаратного шифрования каких-либо сведений. Преобразователем кода называется цифровой узел с mвходами и nвыходами, преобразующий один параллельный код в другой. Моделирование преобразователя кода имеет своей целью выполнить проверку синтезированной схемы на предмет соответствия таблицы истинности преобразованного кода с сигналами на выходах моделируемой схемы. Ниже описываются особенности моделирования уже синтезированного преобразователя кода 8-4-2-1 в дополнительный код.

Задание 3

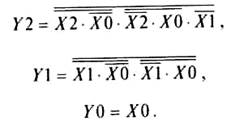

1. Создав новый файл, выполните графический ввод схемы преобразователя кода, осуществляющего преобразование входного сигнала по следующим выражениям для переменных Y2, Y1, Y0:

Входной код задан следующей таблицей (код 8—4—2—1).

Таблица 2-5.

Код 8-4-2-1

| Х2 | X1 | Х0 |

Из анализа выражений и таблицы видно, что в качестве входных используются три сигнала Х0, X1и Х2. Поэтому в схеме необходимо будет использовать три источника сигнала с различной частотой следования импульсов.

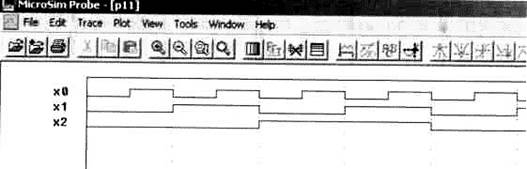

Для создания таких сигналов введите в схему три компонента DigClock (библиотека SOURCE.slb). Задайте для первого источника сигнала Х0параметры ONTIME (длительность импульса) = 0,5 мкс и OFFTIME (длительность паузы) = 0,5 мкс. Аналогичным образом введите в схему и задайте параметры источников сигналов X1(ONTIME = 1 мкс и OFFTIME = 1 мкс) и Х2(ONTIME = 2 мкс и OFFTIME = 2 мкс). На рис. 2-23 показаны временные диаграммы сигналов Х0,X1,Х2.

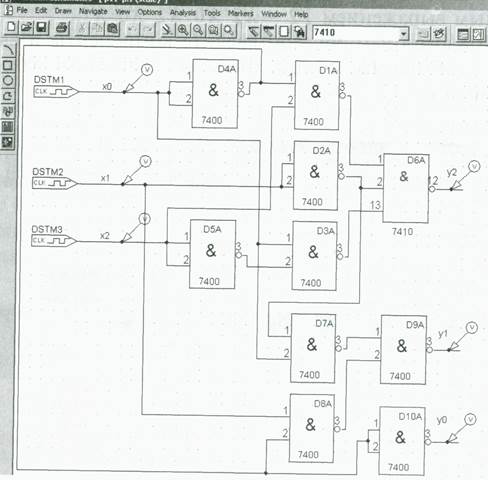

2. Для реализации логического выражения, в соответствии с которым осуществляется преобразование кода, необходимо ввести логические элементы и соответствующим образом выполнить соединения. Из анализа выражения Y2видно, что для схемной реализации такой логической операции необходимо использовать следующие элементы:

- двухвходовый элемент И-НЕ для операций  ,

,  (компонент 7400);

(компонент 7400);

- трехвходовый элемент И-НЕ для результирующей операции (компонент 7410).

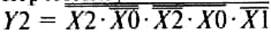

Введем последовательно такие компоненты и выполним соответствующие соединения. Для реализации логической операции  необходимо ввести два компонента 7400.

необходимо ввести два компонента 7400.

Для этого нажмите кнопку выбора компонентов и в раскрывшемся окне Part Browser Basic кнопку Libraries (библиотеки), в поле Libraryвыберите библиотеку EVAL.slb, а в поле Part — компонент 7400, после чего нажмите кнопки ОК, затем Place & Close (ввести компонент и закрыть диалоговое окно).

Рис. 2-23. Временные диаграммы сигналов Х0,X1, Х2

Соединим выход источника сигнала Х0с входами компонента D4A (в результате на выходе получим значение  , выход которого и сигнал Х2необходимо

, выход которого и сигнал Х2необходимо

завести на входы компонента D1A. Позиционные обозначения логических элементов могут отличаться от приводимых, что связано с последовательностью ввода и размещением на схеме самих элементов.

Затем выполним ввод еще двух компонентов и необходимые соединения для реализации операции  :соединим выход источника сигнала Х2с входами компонента D5A, выход которого и сигнал Х0необходимо завести на входы компонента D3A. Для реализации последней операции (объединение по трем входам с отрицанием) введем компонент 7410 (получит имя D6A). Соединим входы компонента D2A с сигналом X1(получим

:соединим выход источника сигнала Х2с входами компонента D5A, выход которого и сигнал Х0необходимо завести на входы компонента D3A. Для реализации последней операции (объединение по трем входам с отрицанием) введем компонент 7410 (получит имя D6A). Соединим входы компонента D2A с сигналом X1(получим  ) выходы D1A, D2A, D3A с входами D6A. Получим фрагмент схемы, реализующий выходную переменную Y2в соответствии с заданным выражением

) выходы D1A, D2A, D3A с входами D6A. Получим фрагмент схемы, реализующий выходную переменную Y2в соответствии с заданным выражением  .

.

Рис. 2-24. Схема, обеспечивающая реализацию логического выражения

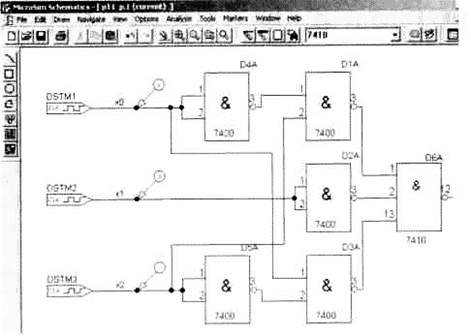

Аналогичным образом введите компоненты и выполните необходимые соединения для реализации выходных переменных Y1,Y0.

3. Для удобства анализа результатов моделирования обозначьте выходы источников сигналов как Х2, X1, Х0, а выходы компонентов, реализующих схемные функции, как Y2, Y1, Y0.Для этого дважды нажмите на соответствующем проводнике, исходящем от компонента, и в появившемся

3. Для удобства анализа результатов моделирования обозначьте выходы источников сигналов как Х2, X1, Х0, а выходы компонентов, реализующих схемные функции, как Y2, Y1, Y0.Для этого дважды нажмите на соответствующем проводнике, исходящем от компонента, и в появившемся

диалоговом окне введите соответствующее обозначение.

4. Расположите на обозначенных проводниках Х2, X1, Х0 и Y2, Y1, Y0маркеры для измерения сигналов, используя команду Markers/Mark Voltage и расставляя маркеры в указанной последовательности.

5. Сохраните схему.

Задайте необходимые параметры директивы моделирования переходных процессов(Analysis Setup/Transient): конечное время анализа (Final Time = 20u), временной шаг расчета характеристик (Step Ceiling = 50n) и интервал между точками отсчета при выводе результатов моделирования (Print Step = 50n). Закрыв окно Analysis Setup, запустите режим моделирования командой Analysis/Simulate или нажатием клавиши F11.

Рис. 2-25. Схема преобразователя кода 8-4-2-1 в дополнительный код

7. В окне программы Probe по графикам входного и преобразованного кодов проверьте соответствие полученных результатов и таблицы истинности (таблица 2-6). Для этого, включите режим привязки курсора к построенному графику (кнопка  ), щелкните левой кнопкой мыши на графике и в дискретные моменты времени, соответствующие изменению входных переменных Х2, X1, Х0,определите значения выходных переменных Y2, Y1, Y0.

), щелкните левой кнопкой мыши на графике и в дискретные моменты времени, соответствующие изменению входных переменных Х2, X1, Х0,определите значения выходных переменных Y2, Y1, Y0.

Для проверки работоспособности схемы преобразователя кода приводится таблица истинности первичного и преобразованного кодов.

Таблица 4.6.

Таблица соответствия кода 8-4-2-1 и дополнительного кода

| Код 8-4-2-1 | Дополнительный код | ||||

| х2 | x1 | х0 | у2 | y1 | у0 |

В рассмотренном примере использованы простейшие логические элементы, при этом возможно моделирование цифровых схем в другом элементном базисе, что определяется составом библиотек цифровых компонентов системы DesignLab.