При наборе переменных (0, 1, 1) будет ложь, а при наборе (1, 0, 1) — истина

Булевая алгебра позволяет не только проводить анализ ЛС, описываемых логическими выражениями или таблицами истинности, но и синтез их из более простых, т.е. решать в комплексе структурно-аналитические вопросы ЛС. Анализ ЛС состоит в установлении ее выходных значений по значениям логических входов,тогда как, соединяя известные ЛС в новую схему на основе описывающего ее логического выражения, производим синтез новых ЛС на основе уже имеющихся.

Элементарные ЛС, используемые при создании средств ЦВТ, называются вентилями (gates). В настоящее время существует целый ряд базовых вентилей, на основе которых строится современная ВТ; некоторые из них рассматриваются ниже. Так как набор {И, .ИЛИ, НЕ} логических операций является универсальным. (функционально полным), т.е. на его основе можно представлять любую логическую функцию, то соответствующий ему набор вентилей также будет универсальным:

На основе базовых вентилей может быть построена любая ЛС; при этом вентили (а, б) могут иметь любое число входов, определяемое количеством переменных логического выражения, описывающего ЛС. Из математической логики известно, что наряду с (И, ИЛИ, НЕ) функционально полными являются и другие простые наборы базовых операций: (И, НЕ), {ИЛИ, НЕ} и другие.

С помощью логических схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у них бывают от двух до восьми входов и один или два выхода. Входные и выходные сигналы, соответствующие двум логическим состояниям в логических элементах — 1 и 0, имеют один из двух установленных уровней напряжения. Например, +5 Вольт и 0 Вольт. Высокий уровень обычно соответствует значению «истина» («1»), а низкий — значению «ложь» («О»).

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию. Работу логических элементов описывают с помощью таблиц истинности.

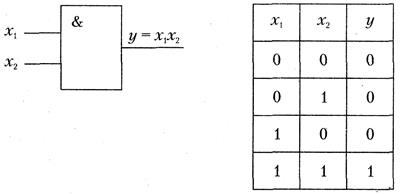

Схема И.Эта схема реализует конъюнкцию двух или более логических значений. Условное обозначение на структурных схемах и таблица истинности схемы И с двумя входами представлены на рис. 4.4.

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль. Связь между выходом уэтой схемы и входами х1и х2 описывается соотношением: у = x1 x2 (читается как x1 и х2). Операция конъюнкции на структурных схемах обозначается знаком & (читается как «амперсэнд»), являющимся сокращенной записью английского слова «and».

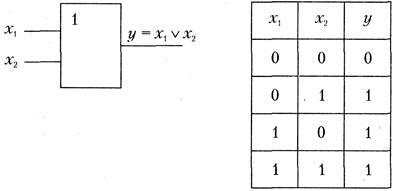

Схема ИЛИ.Эта схема реализует дизъюнкцию двух или более логических значений. Когда хотя бы на одном входе схемы ИЛИ будет единица, на ее выходе также будет единица.

Условное обозначение на структурных схемах и таблица истинности схемы ИЛИ с двумя входами представлены на рис. 4.5. Знак 1 на схеме соответствует обозначению, т. е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1. Связь между выходом у этой схемы и входами x1 и х2 описывается соотношением: у = x1 х2 (читается как х1 или х2).

Рис. 4.4. Условное обозначение и таблица истинности схемы И

Рис. 4.5. Условное обозначение и таблица истинности схемы ИЛИ

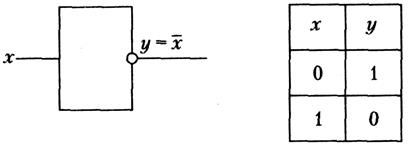

Схема НЕ.Схема НЕ (инвертор) реализует операцию отрицания. Связь между входом х этой схемы и выходом у можно записать соотношением у = ¯х , где ¯х читается как «не x» или «инверсия x».

Если на входе схемы 0, то на выходе 1. Когда на входе 1, то на выходе 0. Условное обозначение и таблица истинности инвертора представлены на рис. 4.6.

Рис. 4.6. Условное обозначение и таблица истинности схемы НЕ

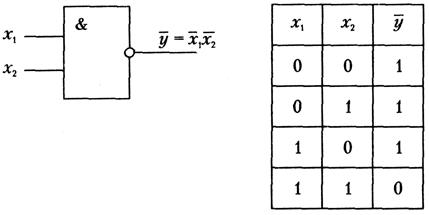

Схема И—НЕ.Схема состоит из элемента И и инвертора и осуществляет отрицание результата схемы И. Связь между выходом у и входами x1 и х2 схемы записывают следующим образом: у =  1

1  2, где

2, где  1

1  2 читается как «инверсия x1 и х2».Условное обозначение на структурных схемах и таблица истинности схемы И—НЕ с двумя входами представлены на рис. 4.7.

2 читается как «инверсия x1 и х2».Условное обозначение на структурных схемах и таблица истинности схемы И—НЕ с двумя входами представлены на рис. 4.7.

Рис. 4.7. Условное обозначение и таблица истинности схемы

И—НЕ

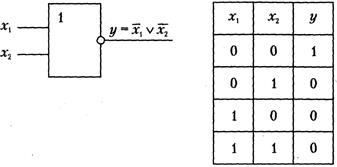

Схема ИЛИ—НЕ.Схема состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата схемы ИЛИ. Связь между выходом у и входами x1 и х2 схемы записывают следующим образом: у=  1

1  2, где

2, где  1

1  2, читается как "инверсия x1 или х2". Условное обозначение на структурных схемах и таблица истинности схемы ИЛИ—НЕ с двумя входами представлены на рис. 4.8.

2, читается как "инверсия x1 или х2". Условное обозначение на структурных схемах и таблица истинности схемы ИЛИ—НЕ с двумя входами представлены на рис. 4.8.

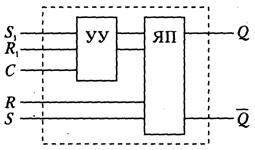

Триггер (от англ. trigger—защелка, спусковой крючок) — электронное устройство с двумя устойчивыми состояниями равновесия, чередующимися под воздействием внешних сигналов, предназначенных для записи и хранения 1 бита данных.

Рис. 4.8. Условное обозначение и таблица истинности схемы ИЛИ—НЕ

Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает «хлопанье».

В отличие от рассмотренных выше логических схем, триггеры — это логические устройства с памятью. Выходные сигналы триггеров в общем случае зависят не только от их входных сигналов, действующих в настоящий момент, но и от сигналов, действовавших на входы до этого (рис. 4.9).

Рис. 4.9. Функциональная схема триггера

Триггер функционирует следующим образом. Устройство управления (УУ) преобразует входные сигналы так, что ячейка памяти (ЯП) принимает одно из двух устойчивых состояний в зависимости от входных сигналов. Входные сигналы поступают на входы S1 и R1 преобразуются устройством управления (УУ) и поступают на внутренние входы ячейки памяти (ЯП). В общем случае устройство управления может отсутствовать. Тогда сигналы подаются непосредственно на входы R и S ячейки памяти.

В триггерах также может осуществляться синхронизация приема информации с помощью входа С. При наличии входа С триггер называют синхронным, в противном случае — асинхронным.

В асинхронных триггерах информация может записываться непрерывно. В этом случае она определяется информационными сигналами, действующими на входах в данный момент времени, т. е. изменение состояния ячейки памяти происходит мгновенно после изменения состояния информационных входов.

В синхронном (или тактируемом) триггере информация заносится только в момент действия так называемого синхронизирующего сигнала. Синхронизация триггера может осуществляться как импульсом (потенциалом), так и фронтом (перепадом потенциала). В схемотехнике приняты следующие обозначения входов триггеров:

— прямой выход триггера;

— прямой выход триггера;

— инверсный выход триггера;

— инверсный выход триггера;

S — раздельный вход установки в единичное состояние (напряжение высокого уровня на прямом выходе Q);

R — раздельный вход установки в нулевое состояние (напряжение низкого уровня на прямом выходе Q);

D — информационный вход (на него подается информация, предназначенная для занесения в триггер);

С — вход синхронизации;

Т — счетный вход.

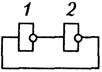

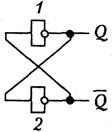

В основе любого триггера находится кольцо из двух инверторов (рис. 4.10). Это кольцо принято изображать в виде так называемой защелки (рис. 4.11).

Однозначную запись 1 бита информации в защелку можно осуществить, если снабдить ее цепями управления и запуска.

Схемы триггеров делятся на несколько типов: RS-, Т-, D-, JK-триггер и др. Состояние триггера определяется выходным Q(Q)'-сигналом, а правила его функционирования задаются таблицами переходов. Схема RS-триггера составляет основу для построения других типов триггеров.

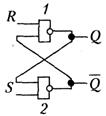

Самый распространенный тип триггера — RS-триггер. Принципиальная схема RS-триггера (рис. 4.12) содержит защелку (два элемента И—НЕ или ИЛИ—НЕ), а также два раздельных статических входа управления. В зависимости от используемых элементов можно получить триггеры с прямыми входами (за активный логический уровень принимают уровень логической единицы) — элемент ИЛИ—НЕ — или с инверсными входами (за активный уровень принимается уровень логического ноля). Эти входы управления называют R (reset — сброс) и S (set — установка).

Рис. 4.10. Кольцо инверторов

Рис. 4.11. Элемент-защелка

Рис. 4.12. Принципиальная схема RS-триггера

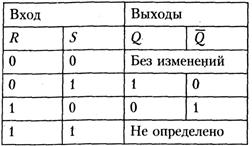

По сути дела, RS-триггер, изображенный на рис. 4.12, это триггер без устройства управления. Для триггера с прямыми входами подача на вход S-триггера логической единицы, а на вход R — логического ноля приведет к тому, что на выходе триггера Q установится сигнал единицы, и наоборот - при подаче на R единицы, а на S — ноля на выходе Q установится сигнал ноля. Таким образом, таблица истинности для данного триггера будет иметь вид, показанный в табл. 4.3.

Таблица 4.3

Как видно из табл. 4.3, комбинация R = 1 и S = 1 является запрещенной. После нее состояние выходов триггерастановится неопределенным. На выходе Q может установиться как состояние логического ноля, так и состояние логической единицы.

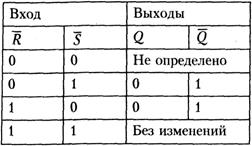

Иногда режим работы триггера, при котором R = 1, a S = 0, называют режимом очистки, при R =0, S = 1 — режимом записи, а при R = 0, S = 0 — режимом хранения, так как информация на выходе триггера в этом случае не изменяется. Для триггера с инверсными входами таблица истинности имеет вид, представленный в табл. 4.4.

Таблица 4.4

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно восемь триггеров, для запоминания килобайта соответственно 8 ´ 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

В качестве важных последовательностных схем, выполняемых на одной ИС, можно отметить счетчики, сдвиговые регистры, элементы памяти и др.

Организация машины

Архитектура ЭВМ – это многоуровневая иерархия аппаратно-программных средств, из которых строится ЭВМ. Каждый из уровней допускает многовариантное распределение (построение) и применение. Конкретная реализация уровней определяет особенности структурного построения ЭВМ.

Архитектура – это наиболее общие принципы построения ЭВМ, реализующие программное управление работой и взаимодействием основных ее функциональных узлов.

ЭВМ – это устройство, выполненное на электронных приборах, предназначенное для автоматического преобразования информации под управлением программы.

Со времени появления в 40-х гг. XX в. первых электронных цифровых вычислительных машин технология их производства была значительно усовершенствована. В последние годы благодаря развитию интегральной технологии существенно улучшились их характеристики, значительно снизилась стоимость. Однако несмотря на успехи, достигнутые в области технологии, существенных изменений в базовой структуре и принципах работы вычислительных машин не произошло. Так, в основу построения подавляющего большинства современных компьютеров положены общие принципы функционирования универсальных вычислительных устройств, сформулированные еще в 1945 г. американским ученым Джоном фон Нейманом.

Согласно фон Нейману, для того чтобы ЭВМ была универсальным и эффективным устройством обработки информации, она должна строиться в соответствии со следующими принципами: