Опишите назначение кэш-памяти. Перечислите виды и способы организации кэш-памяти. Приведите схему иерархии памяти в ЭВМ

Кэш — это память с большей скоростью доступа, предназначенная для ускорения обращения к данным, содержащимся постоянно в памяти с меньшей скоростью доступа ( «основной памяти»). Кэширование применяется ЦПУ, жёсткими дисками, браузерами, веб-серверами, службами DNS и WINS.

Кэш состоит из набора записей. Каждая запись ассоциирована с элементом данных или блоком данных (небольшой части данных), которая является копией элемента данных в основной памяти. Каждая запись имеет идентификатор, определяющий соответствие между элементами данных в кэше и их копиями в основной памяти.

Когда клиент кэша (ЦПУ, веб-браузер, операционная система) обращается к данным, прежде всего исследуется кэш. Если в кэше найдена запись с идентификатором, совпадающим с идентификатором затребованного элемента данных, то используются элементы данных в кэше. Такой случай называется попаданием кэша. Если в кэше не найдена запись, содержащая затребованный элемент данных, то он читается из основной памяти в кэш, и становится доступным для последующих обращений. Такой случай называется промахом кэша. Процент обращений к кэшу, когда в нём найден результат, называется уровнем попаданий или коэффициентом попаданий в кэш.

Уровни кэша

Кэш центрального процессора разделён на несколько уровней. В универсальном процессоре в настоящее время число уровней может достигать 3. Кэш-память уровня N+1 как правило больше по размеру и медленнее по скорости доступа и передаче данных, чем кэш-память уровня N.

Самой быстрой памятью является кэш первого уровня — L1-cache. По сути, она является неотъемлемой частью процессора, поскольку расположена на одном с ним кристалле и входит в состав функциональных блоков. В современных процессорах обычно кэш L1 разделен на два кэша, кэш команд (инструкций) и кэш данных (Гарвардская архитектура). Большинство процессоров без L1 кэша не могут функционировать. L1 кэш работает на частоте процессора, и, в общем случае, обращение к нему может производиться каждый такт. Зачастую является возможным выполнять несколько операций чтения/записи одновременно. Латентность доступа обычно равна 2−4 тактам ядра. Объём обычно невелик — не более 384 Кбайт.

Вторым по быстродействию является L2-cache — кэш второго уровня, обычно он расположен на кристалле, как и L1. В старых процессорах — набор микросхем на системной плате. Объём L2 кэша от 128 Кбайт до 1−12 Мбайт. В современных многоядерных процессорах кэш второго уровня, находясь на том же кристалле, является памятью раздельного пользования — при общем объёме кэша в nM Мбайт на каждое ядро приходится по nM/nC Мбайта, где nC количество ядер процессора. Обычно латентность L2 кэша, расположенного на кристалле ядра, составляет от 8 до 20 тактов ядра.

Кэш третьего уровня наименее быстродействующий, но он может быть очень внушительного размера — более 24 Мбайт. L3 кэш медленнее предыдущих кэшей, но всё равно значительно быстрее, чем оперативная память. В многопроцессорных системах находится в общем пользовании и предназначен для синхронизации данных различных L2.

Схема иерархии памяти в ЭВМ:

· Сверхоперативное ЗУ – регистры

· Быстродействующее буферное ЗУ – кэш

· Оперативное (основное) ЗУ

· Внешнее ЗУ – массовая память

3. Работа с клавиатурой. Представление символов и управляющих кодов в памяти компьютера. Буфер клавиатуры. Управление клавиатурой с помощью контроллера: регистры контроллера, их назначение, общая схема посылки команд клавиатуре.

Система представления символов в персональных компьютерах базируется на Американском стандартном коде для обмена информацией (American Standard Code for Information Interchange), который был введен в 1963 году и ставил в соответствие каждому символу семиразрядный двоичный код, обеспечивающий представление 128 символов. ASCII-код включал две группы символов:

• управляющие символы, используемые в коммуникационных протоколах для передачи команд периферийным устройствам;

• символы пишущей машинки — цифры, буквы и специальные знаки.

Управляющие символы имеют коды с номерами от 0 до lAh. К управляющим относится также символ с кодом 7Fh. Каждый управляющий символ выполняет строго определенную функцию. Функции и кодовые обозначения управляющих символов описаны в табл. 1.1. Все остальные символы относятся к алфавйтно-цифровой группе (группе символов пишущей машинки).

Таблица 1.1. Управляющие символы ASCII-кода

Код символе Мнемоническое обозначение Назначение символа

00h NUL Пустой символ

01h SOH Начало заголовка

02h STX Начало текста

03h ETX Конец текста

04h EOT Конец передачи

05h ENQ Запрос подтверждения

06h ACK Подтверждение

07h BEL Звонок (звуковой сигнал)

08h BS Забой (возврат на одну

позицию влево)

09h HT Горизонтальная табуляция

OAh LF Перевод строки

OBh VT Вертикальная табуляция

OCh FF Перевод формата (переход к

новой странице)

ODh CR Возврат каретки

OEh SO Переход на нижний регистр

OFh SI Переход на верхний регистр

10h DLE Завершение сеанса связи

11h DC1 Управление устройством № 1

12h DC2 Управление устройством № 2

13h DC3 Управление устройством № 3

14h DC4 Упрааление устройством № 4

15h NAK Ошибка передачи

16h SYN Холостой ход передатчика

17h ETB Конец передачи блока

18h CAN Отмена

19h EM Конец носителя данных

1Ah SUB Подстановка (замена символа)

1Bh ESC Переход

1Ch FS Разделитель файлов

4. 1Dh GS Разделитель групп

1 Eh RS Разделитель записей

1 Fh US Разделитель элементов

7Fh DEL Удаление символа

Буфер клавиатуры имеет объем 32 байта и располагается в памяти начиная с адреса 0040:001E. Он может накапливать до 15 нажатий на клавишу, независимо от того, являются ли они однобайтными кодами ASCII или двухбайтными расширенными кодами - буфер отводит по два байта для каждого нажатия клавиши (последнее нажатие, которое может быть максимально 16-м по счету, зарезервировано для клавиши <Enter>, которая разрешает исполнение введенной с клавиатуры команды для командного процессора COMMAND.COM). Для однобайтных кодов первый байт содержит код ASCII, а второй - скан-код клавиши. Для расширенных кодов первый байт содержит 0, а второй номер расширенного кода. Этот номер обычно совпадает со скан-кодом клавиши, но не всегда, поскольку некоторые клавиши могут комбинироваться с клавишами сдвига для генерации различных кодов.

Буфер устроен как циклическая очередь, которую называют также буфером FIFO (первый вошел - первым ушел). Однако не имеется определенной ячейки памяти, в которой находилось бы всегда начало строки в буфере. Вместо этого два указателя хранят позиции головы и хвоста строки символов, находящейся в буфере в текущий момент. Указатель головы указывает на позицию, занятую первым символом в буфере, а указатель хвоста - на позицию, следующую за последним символом (т.е. на первую свободную). Новые нажатия клавиш запасаются в позициях, на которые указывает указатель хвоста (в более старших адресах памяти), и соответственно обновляется указатель хвоста. После того, как израсходованы старшие адреса в буфере, новые символы начинают вставляться в самые младшие ячейки буфера; поэтому возможны ситуации, когда хвост буфера имеет меньший адрес, чем голова.

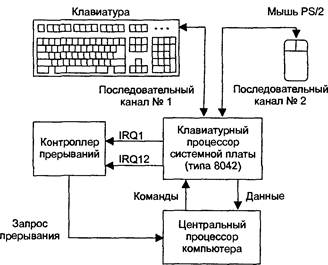

Для управления работой клавиатуры в машинах типа IBM AT и PS/2 использовался микроконтроллер Intel 8042. Кроме клавиатуры, этот контроллер управлял также координатным устройством, в качестве которого обычно использовалась мышь типа PS/2. С целью обеспечения совместимости нового аппаратного обеспечения со старыми программами все современные наборы микросхем, предназначенные для изготовления системных плат (так называемые чипсеты), вынужденно повторяют в своей структуре особенности контроллера i8042 [57, 69, 70, 79, 98].

Управление работой контроллера и обмен данными с мышью и клавиатурой осуществляются при помощи трех регистров: регистра состояния, регистра команд и регистра данных. Кроме того, при поступлении информации от клавиатуры контроллер i8042 вырабатывает прерывание IRQ.1, а при приеме данных от мыши — IRQ12. Интерфейсы клавиатуры и мыши аналогичны, наборы команд управления также имеют некоторое сходство. Упрощенная схема подключения к компьютеру клавиатуры и мыши типа PS/2 показана на рис. 1.

Регистр данных доступен для записи и считывания через порт 60h. В режиме считывания он служит для приема информации от клавиатуры и мыши. В режиме записи регистр данных служит для передачи команд клавиатуре, координатному устройству (мыши PS/2-типа) и клавиатурному контроллеру системной платы i8042. Какого-либо особого формата данный регистр не имеет.

Регистр команд обеспечивает грубую установку режима работы клавиатуры и мыши. Кроме того, режимами работы также можно управлять, посылая в регистр определенные кодовые комбинации.

Рисунок 1

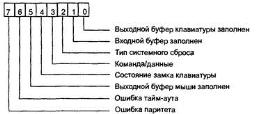

Регистр состояния доступен только для считывания через порт 64h. Формат регистра показан на рис. 2. Значение разрядов регистра следующее:

• бит 0 — признак наличия данных в выходном буфере (0 — буфер пуст, 1 — буфер заполнен);

• бит 1 — признак наличия данных во входном буфере (0 — буфер пуст, 1 — буфер заполнен);

• бит 2 — признак типа последнего общесистемного сброса (0 — сброс по включении питания, 1 — программный сброс);

• бит 3 — признак записи команды (0 — последняя операция записи являлась операцией записи данных, 1 — записи команды);

• бит 4 — состояние «замка» клавиатуры (0 — клавиатура блокирована, 1 — не блокирована);

• бит 5 — признак ошибки тайм-аута передачи в АТ-режиме (0 — нормальное завершение передачи, 1 — произошла ошибка); признак наличия данных в выходном буфере мыши в PS/2-режиме (0 — буфер пуст, 1 — буфер заполнен);

• бит 6 — признак ошибки тайм-аута приема в АТ-режиме (0 — нормальное завершение приема, 1 — произошла ошибка); общий признак ошибки тайм-аута при приеме или передаче данных в PS/2-режиме (0 — нормальное завершение операции, 1 — произошла ошибка);

• бит 7 — признак возникновения ошибки паритета при приеме или передаче данных (0 — нет ошибки, 1 — обнаружена ошибка по четности).

5.

Рисунок 2

ЭКЗАМЕНАЦИОННЫЙ БИЛЕТ № 9

Приведите полную схему вычисления физического адреса при использовании конфликтов в конвейерной обработке. Приведите типы конфликтов. Дайте подробную характеристику структурных конфликтов и назовите способы их устранения.

НЕПРАВИЛЬНЫЙ ВОПРОС!!