Популярные семейства 8-разрядных мк

Число различных модификаций 8-разрядных МК, представленных на мировом рынке столь велико, что лишь одно их перечисление может занять несколько десятков страниц Поэтому кратко охарактеризуем лишь те семейства МК, которые получили широкое распространение в России на протяжении последних десяти лет.

В первую очередь следует остановиться на МК с ядром MCS-51. Начало мощному I клану с ядром MCS-51 положила фирма «Intel», выпустив в 1980 г. МК 8051 АН. Его аналог получил в России распространение под именем 1816ВЕ51. Для своего времени М* 8051 АН был очень сложным изделием - на кристалле размещалось 128 тыс. транзисторов. Этот микроконтроллер содержал процессорное ядро MCS-51, резидентные ПЗУ объемом 4 Кбайта, ОЗУ в 128 байт, 4 порта ввода/вывода, 2 таймера и асинхронный порт. Быстродействие центрального процессора MCS-51 в МК 8051АН по нынешним меркам было невелико. Частота внутренней шины составляла 1 МГц. Однако само ядро MCS-5' оказалось настолько удачным, что на два десятилетия стало стандартом «де-факто» в области 8-разрядных МК.

Фирма «Intel» непрерывно совершенствовала МК с архитектурой MCS-51:

• частота внутренней шины в последних моделях возросла до 3 МГц;

• появились модели с объемом памяти программ 8, 16 и 32 Кбайта;

• в составе МК появились новые периферийные модули (АЦП, программируемый счетный массив, сторожевой таймер).

Одновременно ряд других фирм разработали МК, программно совместимые с MCS-51, обладающие современными типами памяти программ и данных (Flash и EEPROM), имеющие расширенный набор периферийных модулей, работающие в расширенном диапазоне напряжения питания. Фирма «Intel» постепенно свернула производство 8-разрядных МК. В результате основными производителями в мире 51-го семейства оказались фирмы «Philips», «Infineon», «Atmel», «Dallas Semiconductor», «Temic». В 1999 г. фирма «Analog Devices» представила совершенно новый МК Adu812 на основе 51-го ядра. Отличия в технических характеристиках встроенных модулей ЦАП и АЦП этого изделия столь велики, что семейство AduSxx было названо семейством интеллектуальных преобразователей или микроконверторами.

Одновременно с первым МК семейства MCS-51 появился первый МК популярного до настоящего времени семейства НС05 фирмы «Motorola». В рамках этого семейства фирма «Motorola» провозгласила и успешно реализует стратегию «заказных» МК. Многие модели этого семейства своим рождением обязаны крупным потребителям, которые заказывали конфигурацию МК под конкретную продукцию. Сейчас семейство НС05 насчитывает около 180 различных МК, начиная с простейшего 68HC05KJ1 в корпусе DIP16 и заканчивая 128-выводным бескорпусным 68HC05L10 со встроенным контроллером управления 960 сегментами ЖКИ. На протяжении всего своего еще не оконченного периода жизни семейство НС05 является сильным и успешным оппонентом семейству MCS-51. Выполненное на основе принстонской архитектуры в противовес MCS-51 с гарвардской архитектурой, это семейство демонстрирует, во-первых, многообразие возможных технических решений даже для очень несложных задач управления, во-вторых, успех стратегии полного удовлетворения технических требований пользователя без избыточности в архитектуре и производительности. Долгое пребывание семейства НС05 на столь динамичном рынке МК определяется отнюдь не сверхбыстродействием (частота внутренней шины для большинства моделей равна 2 МГц) или уникальным набором команд. Причина успеха кроется в очень точной ориентации на различные сектора рынка массового потребления. Широчайшее разнообразие периферийных модулей при неизменном, очень простом ядре НС05 позволяет разработчику для каждой задачи найти МК практически без избыточных ресурсов архитектуры, что обусловливает низкую стоимость изделия.

В дополнение к дешевым «заказным» МК семейства НС05 фирма «Motorola» еще в 1980-х гг. предложила семейство универсальных и более производительных МК семейства НС11. Это семейство насчитывает около 40 моделей. Процессорное ядро семейства НС11 отличается от НС05 возможностью выполнения операций над 16-разрядными операндами, наличием дополнительных методов адресации, повышенной частотой внутренней шины (до 4 МГц). МК семейства НС11 выгодно отличает наличие трех типов памяти на кристалле: однократно программируемого ПЗУ программ, статического ОЗУ данных и электрически программируемого и электрически стираемого ПЗУ данных.

В конце 1990-х годов фирма «Motorola» представила новое 8-разрядное семейство НС08, которое должно постепенно заменить МК семейства НС05 и стать новым «промышленным стандартом» 8-разрядных МК фирмы. Отличительные особенности и направления развития семейства НС08 перечислены ниже:

• Высокопроизводительное 8-разрядное АЛУ. Увеличение производительности достигается повышением частоты обмена внутренней шины до 8,0 МГц, совмещением цикла исполнения и цикла выборки следующей команды, введением специальных команд просмотра таблиц и организации циклов, расширением числа способов адресами» операндов. Указанные меры позволили повысить производительность центрального процессора НС08 в 6 раз по сравнению с процессором семейства НС05.

• Программная совместимость «снизу вверх» как на уровне исходного текста, так и на

уровне объектных кодов с процессорным ядром семейства НС05.

• Переход к FLASH-технологии для ПЗУ программ пользователя. Для большинства типов

МК проектируется создание двух моделей с возможностью замены «корпус в корпус»

Эти МК полностью идентичны по функциональному составу и различаются только тех-

нологией занесения информации в ПЗУ программ (maskROM или FLASH).

• Библиотека периферийных модулей имеет расширенный набор контроллеров последова- тельного обмена. Кроме стандартных для МК фирмы «Motorola» портов асинхронного (SCI) и синхронного (SP!) обмена, разработаны контроллеры для работы в промышленных сетях с протоколом CAN и для перспективной шины вычислительной техники USB

• Существенно улучшены возможности отладки МК. Встроенный монитор и специальный

порт позволяют производить отладку прикладных программ управления непосредствен-

но на плате конечного изделия без использования дорогостоящих схемных эмуляторов

• МК с памятью программ типа FLASH позволяют реализовать режим программирова-

ния в системе, при котором прикладная программа заносится в память МК, который

стационарно расположен на плате изделия. Коды программы передаются по последо-

вательному интерфейсу от персонального компьютера.

• Специальные схемотехнические решения повышают надежность работы МК в услови-

ях электромагнитных помех и неблагоприятной внешней среды.

Архитектура МК семейства НС08 рассмотрена в п. 4.3.

В конце 1980-х годов фирма «Microchip» выпустила МК PIC16C5X, которые основали ныне широко распространенное семейство PIC16. Благодаря высокой производительности, малому потреблению и низкой стоимости это семейство с RISC-архитектурой составило серьезную конкуренцию производимым в то время 8-разрядным МК с CISC-архитектурой. В основу концепции PIC была положена RISC-архитектура с системой простых однословных команд. Система команд базового семейства Р1С16С5х содержит только 33 команды. Все команды, кроме команд перехода, выполняются за один машинный цикл перекрытием по времени выборок команд из памяти и их исполнения. Производительность Р1С16С5х при частоте тактирования в 20 МГц составляет 5 MIPS. В настоящее время фирма «Microchip» выпускает пять семейств МК с RISC-архитектурой:

1) Р1С15С5х включает недорогие контроллеры с минимальным набором периферии

2)Р1С12Сххх включает МК в миниатюрном 8-выводном корпусе со встроенным такто-

вым генератором; однако «миниатюрность» не мешает некоторым моделям этого семей-

ства иметь встроенный модуль 8-разрядного АЦП;

3) Р1С16х/7х/8х/9х объединяет МК с развитой периферией; в число периферийных

модулей входят таймеры-счетчики с опциями захвата/сравнения, широтно-импульсные

модуляторы, аналоговые компараторы, АЦП, контроллеры различных последователь-

ных интерфейсов;

4)Р1С17С4х/5хх включает высокопроизводительные МК с расширенной системой ко-

манд и обширной периферией; МК этого семейства имеют встроенный аппаратный умно-

житель 8x8, выполняющий операцию умножения за один машинный цикл;

5) Р1С18Сххх - новое семейство с оптимизированным под использование Си-

компилятора RISC-ядром и частотой внутренней шины до 10 МГц.

В1997 г. фирма « Atmel» представила первые МК семейства AVR. Семейство AVR ATS объединяет мощный гарвардский RISC-процессор с раздельным доступом к памяти m грамм и данных, 32 регистра общего назначения и развитую систему команд.Последние версии семейства AVR имеют в составе АЛУ аппаратный умножитель. Базовый набор команд AVR содержит 120 инструкций. Большинство команд выполняется за один машинный цикл, производительность ряда моделей составляет 20 MIPS. Периферия AVR MK включает параллельные порты, таймеры-счетчики, различные последовательные интерфейсы, АЦП, аналоговые компараторы. MK AVR подразделяются на три серии:

1)tiny AVR - MK в 8-выводном корпусе низкой стоимости;

2)classic AVR - основная линия МК с производительностью до 16 MIPS, Flash память программ объемом до 8 Кбайт и статическим ОЗУ данных 128. ..512 байт;

3)mega AVR - МК для сложных приложений, требующих большого объема памяти

(Flash ПЗУ до 128 Кбайт), ОЗУ до 4 Кбайт, производительностью до 6 MIPS.

Приведенная краткая аннотация семейств 8-разрядных МК является далеко не полной, 8-разрядные МК выпускают также фирмы «ST-Microelectronics» (семейства ST6, ST7 и ST9), «National Semiconductor» (семейство СОР8), «Zilog», NEC, «Mitsubishi», «Hitachi», «Toshiba», «Scenix» и др. Продукция этих фирм постепенно появляется на российском рынке, но пока не получила широкого распространения.

ПРОЦЕССОРНОЕ ЯДРО МК

Процессорное ядро представляет собой неразрывное единство трех составляющих его технического решения:

1)архитектуры центрального процессора с присущими ей набором регистров для

хранения промежуточных данных, организацией памяти и способами адресации операндов в пространстве памяти, системой команд, определяющей набор возможных действий

над операндами, организацией процесса выборки и исполнения команд',

2)схемотехники воплощения архитектуры, которая определяет последовательность

перемещения данных по внутренним магистралям МК между регистрами, арифметическо-логическим устройством и ячейками памяти в процессе выполнения каждой команды;

3)технологии производства полупроводниковой БИС МК, которая позволяет разместить схему той или иной сложности на полупроводниковом кристалле, определяет допустимую частоту переключений в схеме и энергию потребления.

Эти три составляющие неразрывно связаны друг с другом и, в конечном счете, определяют важнейший параметр процессорного ядра МК - его производительность.

Ядро современных 8-разрядных МК реализуют как на основе CISC-архитектуры - это МК семейств НС05, НС11, НС08 фирмы «Motorola», семейства MCS-51 фирм «Intel», «Atmel», «Philips», MK семейства С500 фирмы «Infineon», -так и на основе RISC-архитектуры - семейства PIC16, PIC17, Р1С18фирмы «Microchip», семейство AVR фирмы «Atmel», семейство SX фирмы «Scenix».

В приложении к 8-разрядным МК микропроцессор с CSIC-архитектурой имеет одно

байтовый, двухбайтовый и трехбайтовый (редко четырехбайтовый) формат команд. Выборка команды из памяти осуществляется побайтно в течение нескольких машинных

циклов. Время выполнения каждой команды с учетом времени выборки в большинстве

случаев составляет от 1 до 10 циклов. Длительность машинного цикла равна периоду частоты тактирования внутренних магистралей микроконтроллера fBUS. Максимально допустимое значение частоты fBUS является одной из важнейших характеристик процессорного ядра, так как чем больше fBUS, тем выше его производительность. Следует особо обратить внимание, что для МК с CISC архитектурой частота тактирования внутренних магистралей МК fBUS всегда в несколько раз меньше предельно допустимой частоты кварцевого резонатора, который используется в качестве времязадающего элемента встроенного генератора.

Микроконтроллер с RISC-архитектурой имеет формат команды фиксированной длины: например, 12,14 или даже 16 бит для МК с 8-разрядным форматом обрабатываемого слова. Выборка из памяти и исполнение подавляющего большинства команд осуществляются за один машинный цикл МК, т. е. один период fBUS— одна команда. Однако и для МК с RISC-архитектурой частота fBUS не всегда совпадает с частотой подключаемого кварцевого резонатора.

Производительность микропроцессоров и МК в том числе принято оценивать числом элементарных операций, которые могут быть выполнены в течение одной секунды. Единица измерения производительности - миллион операций в секунду (MIPS). Для расчета численного значения производительности в MIPS принято использовать время выполнения команды пересылки «регистр-регистр». Эта команда присутствует в перечне инструкций Ассемблера любого микропроцессора и имеет минимальное время выполнения.

Производительность (MIPS) = 1/t команды (мкс).

На практике в качестве косвенного параметра для оценки производительности МК используют предельную частоту тактирования, т. е. частоту времязадающего элемента генератора синхронизации fXCLK. Именно эта частота обычно указана в справочных данных 8-разрядного МК. Однако использовать ее для прямого расчета производительности в большинстве случаев нельзя. Дело в том, что длительность машинного цикла центрального процессора определяется частотой обмена по внутренним магистралям адреса и данных fBUS . Соотношение fXCLK и fBUS индивидуально для каждого процессорного ядра МК. Так для «Intel» MSC-51 fXCLI/fgus - 12, для «Microchip» PIC16 fXCLI/fBUS = 4, для AVR «Amtel» fXCL/fBUS = 1. В МК «Motorola» HC08 тактирование осуществляется с использованием умножителя частоты и fBUS > fXCLK Поэтому при сравнении производительности различных МК следует сопоставлять максимальную частоту тактирования межмодульных магистралей fBUS, а не приведенную в паспортных данных fXCLK. Численные значения fgus для популярных семейств 8-разрядных МК приведены в табл. 4.1.

По определению МК с RISC-архитектурой должны иметь более высокую производительность по сравнению с CSIC МК при одной и той же частоте внутренней магистрали fBUS так как первые выполняют каждую команду за один машинный цикл, а последние -за несколько. Для МК с RISC-архитектурой время выполнения любой операции составляет 1/ fBUS следовательно, их производительность (в MIPS) равна fBUS(B МГц). Например, производительность МК PIC16 составляет 5 MIPS, МК AVR - 20 MIPS. В МК с CISC-архитектурой число циклов выполнения операции «регистр-регистр» составляет от 1 до 3, что снижает производительность.

Однако такая оценка производительности является общей. Она не учитывает особенности алгоритмов управления, используемых в каждой конкретной области применения. Так, при реализации быстродействующих регуляторов основное внимание следует уделять времени выполнения операций умножения и деления, которые требуются при реализации уравнений различных передаточных функций. А при реализации кнопочной станции кабины лифта следует оценивать время выполнения только логических функций, которые используются при опросе клавиатуры и при генерации протокола последовательного интерфейса связи с контроллером управления движения, который оптимизирует перемещение между этажами сразу нескольких кабин лифта. В задачах оптимального управления по таблицам, которые характерны для устройств силовой электроники, на первый план выходит возможность быстрого перебора больших таблиц данных. Поэтому в критических ситуациях, связанных с требованиями высокого быстродействия, следует оценивать производительность на основе тех операций, которые преимущественно используются в алгоритме управления и имеют ограничение по времени выполнения.

В задачах управления объектом в реальном времени существует еще один очень важный фактор производительности, который никак не отображается числом операций в секунду. Это время перехода на подпрограмму прерывания по запросу внешнего устройства или периферийного модуля. В процессе перехода на подпрограмму прерывания каждый МК должен:

• распознать запрос на прерывание;

• дождаться завершения выполнения текущей команды;

• сохранить программный счетчик PC и некоторые регистры центрального процессора

в стеке, загрузить вектор прерывания;

• выполнить некоторые вспомогательные команды;

• и лишь затем приступить к выполнению алгоритма обслуживания устройства, которое вызвало это прерывание;

Суммарное время перехода на подпрограмму прерывания определяется архитектурой процессорного ядра МК и частотой его тактирования.

4.1.4. РЕЗИДЕНТНАЯ ПАМЯТЬ МК

Закрытая архитектура современных 8-разрядных МК стала реализуемой лишь при условии интеграции на кристалл МК модулей памяти двух типов: энергонезависимого запоминающего устройства для хранения кодов прикладных программ (ПЗУ) и оперативного запоминающего устройства для хранения промежуточных результатов вычислений (ОЗУ). С момента появления МК технология энергонезависимых запоминающих устройств претерпела множество изменений, которые позволили не только повысить информационную емкость, быстродействие, надежность хранения информации, но и привели к появлению принципиально новых технологий программирования резидентной памяти МК. С точки зрения пользователей МК следует различать пять типов энергонезависимой резидентной памяти.

1. ПЗУ масочного типа - Mask-ROM.Содержимое ячеек ПЗУ этого типа записывается на заводе-изготовителе МК с помощью масок и не может быть заменено или «допрограммировано» в области ранее не использованного сегмента памяти.. Первые образцы масочных ПЗУ появились в начале 1960-х гг., но даже сегодня ПЗУ масочного типа - самое дешевое и эффективное решение при больших объемах выпускаемой аппаратуры. Использование МК с масочным ПЗУ экономически становится рентабельным при партии в несколько десятков тысяч штук. Кроме благоприятных экономических аспектов решения с ПЗУ масочного типа имеют и другое преимущество. Они обеспечивают высокую надежность хранения информации по причине программирования в заводских условиях с последующим контролем качества. Недостатки ПЗУ масочного типа очевидны: любое изменение прикладной программы потребует новой серии ИС МК, что может оказаться весьма дорогостоящим.

2.ПЗУ, однократно программируемые пользователем - OTPROM (One-Time

Programmable ROM). В незапрограммированном состоянии каждая ячейка памяти модуля однократно программируемого ПЗУ при считывании возвращает код $FF. Программированию подлежат только те разряды, которые после программирования должны содержать «О». Если в процессе программирования некоторые разряды какой-либо ячейки памяти были установлены в «О», то восстановить в этих разрядах единичное значение уже невозможно. Поэтому рассматриваемый тип памяти и носит название «однократно программируемые ПЗУ». Однако те разряды, которые в процессе предшествующего сеанса программирования не изменялись, т. е. имеют единичные значения, могут быть подвергнуты программированию в последующем и «доустановлены» в «О». Число возможных сеансов программирования модуля однократно программируемого ПЗУ в составе МК не имеет ограничений. Технология программирования состоит в многократном приложении импульсов повышенного напряжения к элементарным ячейкам адресуемого байта памяти(т. е. к битам), подлежащим программированию. Уровень напряжения программирования, число импульсов и их временные параметры должны в точности соответствовать техническим условиям. В противном случае ячейки памяти могут восстановить единичное значение по прошествии некоторого времени (иногда нескольких лет) или при изменении условий работы. МК с однократно программируемым ПЗУ рекомендуется использовать в изделиях, выпускаемых небольшими партиями.

3.ПЗУ, программируемые пользователем с ультрафиолетовым стиранием – EPROM (Erasable Programmable ROM). ПЗУ данного типа допускают многократное программирование. Технология программирования близка к технологии однократно программируемых ПЗУ. Перед каждым сеансом программирования для восстановления единичного значения ранее запрограммированных ячеек памяти весь модуль ПЗУ должен быть подвергнут операции стирания при помощи ультрафиолетового облучения. Для этого корпус МК выполнен со специальным стеклянным окном, внутри которого расположена пластина ИС МК. Но если некоторые разряды ячеек памяти должны быть «допрограммированы» с «1» на «О» при неизменном состоянии ранее запрограммированных разрядов, то операция стирания может быть пропущена. Число сеансов стирания/программирования ПЗУ данного типа ограничено и составляет 25 - 100 раз при условии соблюдения технологии программирования (напряжение, число и длительность импульсов программирования) и технологии стирания (волновой диапазон источника ультрафиолетового излучения). МК с ПЗУ данного типа имеют высокую стоимость, поэтому их рекомендуется использовать только в опытных образцах изделий.

4.ПЗУ, программируемые пользователем с электрическим стиранием - EEPROM

или E2PROM (Electrically Erasable Programmable ROM). Электрически программируемые и электрически стираемые ПЗУ совместили в себе положительные качества рас

смотренных выше типов памяти. Во-первых, ПЗУ типа EEPROM программируются

пользователем, во-вторых, эти ПЗУ могут быть многократно подвергнуты операции стирания, и, следовательно, многократно программируются пользователем, в-третьих, эти

ПЗУ дешевле ПЗУ с ультрафиолетовым стиранием. Максимальное число циклов стирания/программирования ПЗУ типа EEPROM в составе МК обычно равно 10000.

Для сравнения тот же тип памяти в автономном корпусе допускает 106 циклов стирания/программирования. Технология программирования памяти типа EEPROM позволяет реализовать побайтное стирание и побайтное программирование, для чего

к выбранной ячейке памяти должно быть приложено относительно высокое напряжение 10 -20 В. Однако допускается также одновременное стирание некоторого количества ячеек памяти с последовательными адресами, т. е. стирание блока памяти. Несмотря на очевидные преимущества, редкие модели современных МК используют ПЗУ типа

EEPROM для хранения программ. Виной тому два обстоятельства. Во-первых, ПЗУ типа

EEPROM имеют ограниченную емкость и могут использоваться в качестве резидентной

памяти программ только в мало выводных МК с небольшим объемом памяти. Во-вторых,

почти одновременно с EEPROM ПЗУ появились ПЗУ типа FLASH, которые обеспечивают близкие пользовательские характеристики, но при этом имеют более низкую стоимость.

5.ПЗУ с электрическим стиранием типа FLASH - FLASH ROM. Электрически программируемые и электрически стираемые ПЗУ типа FLASH были предназначены для заполнения «ниши» между дешевыми однократно программируемыми ПЗУ большой емкости и дорогими EEPROM ПЗУ малой емкости. ПЗУ типа FLASH сохранили преимущества, присущие EEPROM: возможность многократного стирания и программирования посредством приложения повышенного напряжения. Однако для увеличения объема памяти транзистор адресации каждой элементарной ячейки был удален, что не дает возможности программировать каждый бит памяти отдельно. Память типа FLASH стирается и программируется страницами или блоками. Страница, как правило, составляет 8, 16 или 32 байта памяти, блоки могут объединять некоторое число страниц, вплоть до полного объема резидентного ПЗУ МК (до 60 Кбайт). Упрощение декодирующих схем, произошедшее из-за уменьшения числа транзисторов, и, как следствие, снижение стоимости и размеров привело к тому, что МК с FLASH памятью программ в настоящее время становятся конкурентоспособными не только по отношению к МК с однократно программируемым ПЗУ, но и с масочным ПЗУ также.

Первый тип памяти (mask ROM) предполагает программирование МК только в заводских условиях. Второй и третий типы памяти (OTPROM и EPROM) могут программироваться непосредственно пользователем, но в режиме программирования требуют подключения источника повышенного напряжения к одному из выводов МК. Для их программирования используются специальные программаторы, в которых требуемая последовательность импульсов программирования с амплитудой 10 - 25 В создается внешними по отношению к МК средствами. Технология программирования памяти первых трех типов не предполагает изменения содержимого некоторых ячеек энергонезависимой памяти в процессе работы устройства под управлением прикладной программы

Память типа EEPROM и FLASH также требует в процессе стирания/программирования приложения повышенного напряжения. В ранних образцах МК (например, Microchip Р1С16С5хх) это напряжение должно было быть подано на один из выводов МК в режиме программирования. В новейших версиях МК (Motorola HC08, Microchip PIC16, Atmel AVR) модули FLASH и EEPROM ПЗУ содержат встроенные схемы усиления, которые называют генераторами накачки. Допускается включение и отключение генератора накачки под управлением программы посредством установки битов в регистрах специальных функций модулей памяти. Следовательно, появилась принципиальная возможность осуществить программирование или стирание ячеек памяти FLASH и EEPROM ПЗУ в процессе управления объектом, без останова выполнения прикладной программы и перевода МК в режим программирования. Вспомним разницу между EEPROM и FLASH ПЗУ в составе МК. EEPROM ПЗУ практически никогда не используется для хранения программ, но оно имеет режим побайтного программирования. Предоставленная техническая возможность программирования под управлением прикладной программы становится реализуемой, так как носителем программы в МК является другой модуль памяти. Следовательно, в процессе программирования повышенное напряжение не прикладывается к носителю программы алгоритма программирования, и эта программа может быть выполнена в обычном режиме. Данное обстоятельство сделало EEPROM память идеальным энергонезависимым запоминающим устройством для хранения изменяемых в процессе эксплуатации изделия настроек пользователя. В качестве примера достаточно вспомнить современный телевизор или музыкальный центр: настройки каналов сохраняются при отключении питания. Одной из тенденций совершенствования резидентной памяти 8-разрядных МК стала интеграция на кристалл МК сразу двух модулей энергонезависимой памяти: ОТР или FLASH -для хранения программ и EEPROM -для хранения перепрограммируемых констант.

Сложнее обстоит дело с возможностью программирования FLASH ПЗУ под управлением прикладной программы. Даже если модуль FLASH ПЗУ содержит встроенный генератор накачки, то попытка перевода модуля в режим программирования посредством установки битов режима приведет к невозможности дальнейшего считывания программы, которая в это FLASH ПЗУ записана. И МК «зависнет». Поэтому та часть программы, которая реализует программирование FLASH ПЗУ, должна быть обязательно расположена в памяти другого типа. Наиболее часто в качестве такой памяти выбирают ОЗУ МК. Поскольку, если в МК имеется EEPROM ПЗУ, то бессмысленно «допрограммировать» FLASH в процессе работы изделия, в противном случае другой памяти, кроме ОЗУ, в МК просто нет. Если МК допускает возможность выполнения программы, расположенной в ОЗУ, и имеет встроенный генератор накачки модуля FLASH ПЗУ, то такой МК становится «программируемым в системе» (англоязычный термин «In system programmable» -ISP). Для того чтобы возможность программирования в системе стала реализуемой, необходимо предусмотреть пути, по которым в ОЗУ МК будет передана программа алгоритма программирования FLASH ПЗУ, а затем порциями будут передаваться коды прикладной программы, которая должна быть занесена во FLASH ПЗУ. Не следует забывать, что объем сегмента программирования значительно превышает объем резидентного ОЗУ МК. В качестве такого «пути» разработчики МК назначают один из последовательных портов МК. Обслуживание порта реализует специальная программа монитора связи, которая расположена в резидентном масочном ПЗУ МК. Эта программа активизируется посредством установки определенных линий ввода/вывода МК в указанное в спецификации состояние при сбросе МК или простым обращением к ней. Способ активизации указан в техническом описании МК. По последовательному интерфейсу связи персональный компьютер загружает в ОЗУ МК сначала коды программы «программирования», а затем порциями коды прикладной программы для программирования. Возможны так же решения, при которых программа «программирования» сразу записана в память масочного типа и не требует загрузки в ОЗУ МК.

Рассмотренный режим «программирования в системе» в настоящее время все шире используется для занесения прикладной программы в МК, расположенный на плате конечного изделия. Специальный программатор в этом случае не нужен. Кроме того, надежность программирования гарантируется внутренними режимами МК и не зависит от схемных решений программатора. Однако режим «программирования в системе» отличается от режима «допрограммирования» нескольких байтов FLASH памяти под управлением прикладной программы в процессе работы системы. Теоретически возможно решение, при котором программа «программирования», хранящаяся во FLASH ПЗУ, сначала будет перенесена в ОЗУ под управлением прикладной программы, а затем выполнена из ОЗУ. Но при таком решении на время программирования потребуется запретить все прерывания МК, поскольку их обслуживание невозможно по причине недоступности векторов прерывания. Поэтому реализация описанного режима возможна далеко не всегда. В качестве одного из путей предлагается разбить модуль FLASH ПЗУ на два — с независимыми генераторами накачки и регистрами управления. Такое решение предложено в МК HC908AZ60 фирмы «Motorola». Тогда один из модулей может быть поставлен в режим программирования, в то время как программа «программирования» будет выполняться из другого модуля. Впрочем, следует надеяться, что в недалеком будущем проблема программирования FLASH памяти программой из FLASH памяти будет решена. А пока наиболее совершенные модели МК со свойством «программирования в системе» часто имеют в своем составе четыре типа памяти: FLASH ПЗУ программ, mask-ROM монитора связи, EEPROM ПЗУ для хранения изменяемых констант и ОЗУ промежуточных данных.

Технология резидентной FLASH памяти МК непрерывно совершенствуется. Одни из лучших показателей достигнуты в МК семейства НС08 фирмы «Motorola»:

• гарантированное число циклов стирания/программирования составляет 105;

• гарантированный период хранения записанной информации равен 10 годам, т. е. составляет жизненный цикл изделия;

• модули FLASH памяти работают и программируются при напряжении питания МК от 1,8 до 2,7 В;

• эквивалентное время программирования 1 байта памяти снижено до 60 мкс, что позволяет выполнить программирование МК с 32 Кб памяти в течение 2 с.

Перспективные технологии FLASH памяти предполагают увеличение скорости программирования до 1 Мбит/с.

Кроме ПЗУ в состав МК входит также и статическое оперативное запоминающее устройство (ОЗУ). Определение «статическое» выделено не случайно: современные 8-разрядные МК допускают снижение частоты тактирования до сколь угодно малых значений с целью снижения энергии потребления. Содержимое ячеек ОЗУ при этом сохраняется в отличие от динамической памяти. В качестве еще одной особенности следует отметить, что многие МК в техническом описании имеют параметр «напряжение хранения информации» - ustandby. При снижении напряжения питания ниже минимально допустимого уровня UDDMIN, но выше напряжения хранения USTANDBY программа управления микроконтроллером выполняться не будет, но информация в ОЗУ сохранится. Тогда при восстановлении напряжения питания можно будет выполнить сброс МК и продолжить выполнение программы без потери данных. Уровень напряжения хранения составляет = 1 В. Это позволяет в случае необходимости перевести МК на питание от автономного источника (батарейки или аккумулятора) и сохранить тем самым данные ОЗУ. Большого расхода энергии потребления в этом случае не будет, так как система тактирования МК может быть отключена. В последнее время появились МК, которые в корпусе имеют автономный источник питания, гарантирующий сохранение данных в ОЗУ на протяжении 10 лет (МК DS5000 фирмы «Dallas Semiconductor»).

ПОРТЫ ВВОДА/ВЫВОДА

Каждый МК имеет некоторое количество линий ввода/вывода, которые объединены в 8-разрядные параллельные порты ввода/вывода РТх («х»-имя порта, используемое в техническом описании). Порты обозначают либо цифрами (РТО, РТ1, РТ2 и т.д.), либо буквами латинского алфавита (РТА, РТВ, РТС и т. д.). В карте памяти МК каждый порт ввода/вывода представлен регистром данных порта DPTx. В режиме ввода логические уровни сигналов на линиях порта РТх отображаются нулями и единицами в соответствующих разрядах регистра DPTx. В режиме вывода данные, записанные под управлением программы в регистр DPTx, передаются на выводы МК, которые отмечены в качестве линий порта РТх. Обращение к регистру данных DPTx осуществляется теми же командами, что и обращение к ячейкам резидентной оперативной памяти. Кроме того, во многих МК отдельные разряды портов могут быть опрошены командами битового процессора.

С функциональной точки зрения различают следующие типы параллельных портов.

1.Однонаправленные порты, предназначенные в соответствие со спецификацией МК только для ввода или только для вывода информации.

2.Двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации системы.

3.Порты с альтернативной функцией. Отдельные линии этих портов связаны со встроенными в МК периферийными устройствами, такими как таймер, АЦП, контроллеры последовательных приемо-передатчиков. Если соответствующий периферийный модуль МК не используется, то его выводы можно задействовать как обычные линии ввода/вывода. Напротив, если модуль активизирован, то принадлежащие ему линии ввода/вывода автоматически конфигурируются в соответствии с функциональным назначением в модуле и не могут быть использованы в качестве линий ввода/вывода. Как однонаправленные, так и двунаправленные линии портов могут иметь альтернативную функцию.

Рассмотрим схемотехнические особенности буферов линий ввода/вывода МК. В специальной литературе выходные каскады линий ввода/вывода часто называют драйверами (не путать с аналогичным обозначением программных средств). Двунаправленные порты большинства современных МК выполнены с возможностью независимого задания направления передачи каждой линии, т. е. объединение групп линий в порты позволяет организовать обращение к ним как к ячейкам памяти, что удобно при организации обмена в параллельном формате. Но в случае необходимости каждая линия может быть сконфигурирована индивидуально и обслужена командами битового процессора независимо от других линий того же порта ввода/вывода. Учитывая это обстоятельство, схемотехника портов ввода/вывода рассматривается на уровне одной линии.

Различают следующие типы драйверов ввода/вывода:

1)двунаправленные линии, которые настраиваются на ввод или на вывод программированием бита в регистре направления передачи DDPTx; при работе в режиме ввода линия имеет высокое входное сопротивление;

2)двунаправленные линии, которые не требуют предварительной инициализации;

такие линии имеют некоторые особенности при считывании; в режиме ввода эти линии также имеют высокое входное сопротивление;

3)квазидвунаправленные линии; не требуют предварительной инициализации; в ре

жиме ввода драйвер автоматически подключает «подтягивающий» к напряжению питания резистор;

4)двунаправленные линии с возможностью программного подключения «подтягивающих» резисторов.

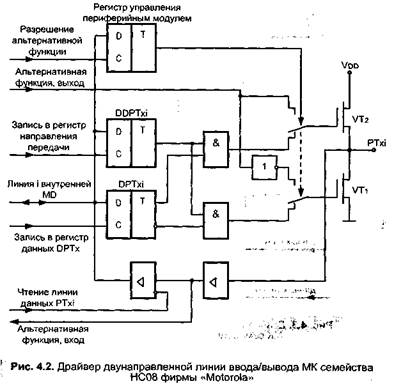

Примером драйверов 1-го типа могут служить линии ввода/вывода МК НС08 Motorola (рис. 4.2). Каждой линии порта поставлен в соответствие одноименный разряд регистра направления передачи DDPTx. Нулевое значение разряда конфигурирует линию на ввод, единичное - на вывод. После сброса МК все линии настроены на ввод. Из рис. 4.2 видно, что в режиме ввода состояние непосредственно в момент считывания логический уровень сигнала линии передается на внутреннюю магистраль данных, минуя регистр данных порта DPTx. В процессе чтения линии ее состояние не запоминается в регистре DPTX и, следовательно, каждое новое обращение к порту ввода может возвращать новое значение. В режиме ввода транзисторы VT1 и VT2 закрыты, буфер находится в высокоомном состоянии (Z-состояние). Значение, которое будет возвращать операция чтения неподключенного входа, в общем случае не определено. Однако на практике его «доопределяют» за счет различия эквивалентных сопротивлений плеча с VT1 и с VT2. Так, в МК семейства НС08 Motorola чтение неподключенного входа возвращает «О». Если в качестве источника сигнала для рассматриваемого высокоомного входа используется логический элемент с открытым коллекторным выходом, то входной сигнал не будет зависеть от состояния выходного транзистора элемента. Он всегда будет равен «О».

Для задания единичного логического уровня входного сигнала следует подключить внешний резистор, который обычно обозначают RPULLUP. При работе линии в режиме вывода транзисторы VT1 и VT2 драйвера управляются сигналом с выхода триггера регистра данных DPTx.

|

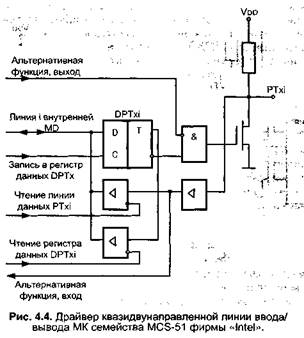

Примером драйверов двунаправленных портов, которые не требуют инициализации, могут служить драйверы порта РОМК 8051 АН фирмы «Intel» (рис. 4.3). Особенность этих драйверов заключается в том, что при считывании возвращаемое значение равно логическому произведению сигнала на линии и содержимого одноименного триггера регистpa данных порта DPTx. По этой причине те разряды порта, которые будут считываться, должны быть предварительно установлены в «1» командой записи в порт и лишь затем прочитаны. Порты с рассматриваемой схемотехникой не имеют регистра направления передачи и, следовательно, не должны инициализироваться. При работе в режиме ввода линия имеет высокое входное сопротивление, но при чтении неподключенного входа возвращается «1».

Квазидвунаправленные драйверы реализованы в портах Р1, Р2, и РЗ МК8051АН фирмы «Intel». Они отличаются от предыдущего драйвера тем, что вместо транзистора VT2 установлен внутренний «подтягивающий» резистор RPULLUP(pиc. 4.4). Поэтому входное сопротивление линии ввода не столь велико, как в двух предыдущих случаях, т. е. входной буфер линии не эквивалентен входу логического элемента. Поэтому драйвер с рассматриваемой схемотехникой и получил название квазидвунаправленного. Линии с этим типом драйвера не требуют инициализации, но для работы в режиме ввода так же как и в предыдущем случае, необходимо предварительно записать в соответствующий разряд регистра данных «1».

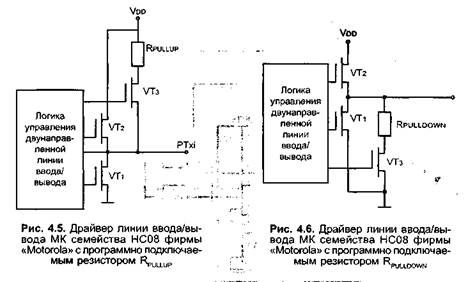

Драйверы линий с изменяемой схемотехникой могут быть выполнены двумя способами (рис. 4.5, 4.6). Однако преследуемая цель одна - сократить число навесных элементов платы МП контроллера.

В первом случае (рис. 4.5) драйвер каждой линии содержит «подтягивающим к 1» резистор (RPULLUP), который обеспечивает уровень логической единицы на входе при разомкнутом контакте. Во втором случае (рис. 4.6) драйвер дополнен «подтягивающим к О» резистором (RPULLDOUN), который способен служить нагрузочным резистором датчика, выходной каскад которого выполнен по схеме эмиттерного повторителя. Рассматриваемые драйверы часто используются в МК фирмы «Motorola». Логика управления встроенными «подтягивающими» резисторами одинакова для обоих типов драйверов:

• подключение «подтягивающих» резисторов допускается аппаратными средствами драй

вера только при конфигурировании линии порта на ввод;

• специальный бит регистра конфигурации МК разрешает программное подключение

«подтягивающих» резисторов на всех линиях ввода одновременно, но не выполняет

это подключение;

• коммутацией «подтягивающего» резистора каждой линии управляет одноименный бит

регистра входного сопротивления PTUEx; значение этого бита может многократно из

меняться в ходе выполнения прикладной программы, тем самым осуществляется динамическое управление входным сопротивлением линии порта ввода и током потребления этой линии.

Рассматривая особенности драйверов линий ввода/вывода, нельзя не остановиться на понятии нагрузочной способности линии. Различают линии с нормальной и

повышенной нагрузочной способностью. Если речь идет о нормальной нагрузочной способности, то следует ориентироваться на следующие цифры: I0вых=1,6+2,0 мА,

I1вых = 0,4+2,0 мА. Типовые значения повышенной нагрузочной способности: I0вых = I1вых =

= 25 мА. Предельное значение повышенной нагрузочной способности на сегодняшний

день составляет: I1вых =60 мА для Microchip PIC17. Следует заметить, что число выводов с повышенной нагрузочной способностью обычно ограничено. Кроме того, в справочных данных указан максимальный суммарный ток всех линий ввода/вывода, который ограничен теплоотводом корпуса МК.