Разработка аналоговой части

Начнём разработку принципиальной схемы устройства с разработки согласующего канала. Он будет состоять из усилителя и фильтра низких частот.

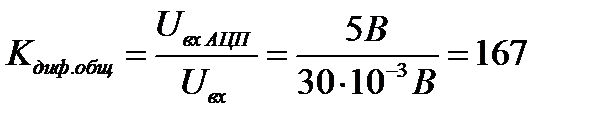

Разработаем усилитель сигнала. Он должен иметь входное сопротивление не менее 40 кОм. Рассчитаем коэффициент усиления дифференциального сигнала. Так как диапазон входных сигналов АЦП 0÷5 В, а сигнал с электродов имеет максимальную амплитуду 30 мВ, то  .

.

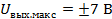

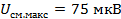

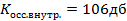

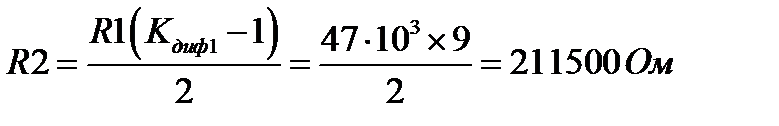

Реализуем усилитель по схеме инструментального усилителя на трёх ОУ. Первый каскад, состоящий из усилителей DA1 и DA2, усиливает дифференциальный сигнал в (1+ 2·R2/R1) раз, коэффициент передачи синфазного напряжения равен единице. Второй каскад, выполненный на DА3 в дифференциальном включении, усиливает дифференциальный сигнал в (R6/R4) раз [6]. Используем операционные усилители К140УД22. Их основные параметры:

1) напряжение питания

2) максимальное выходное напряжение

3) напряжение смещения нуля

4) ток потребления

5) коэффициент ослабления синфазного сигнала при разомкнутой цепи отрицательной обратной связи

Используем резисторы С2-29в точности 0,1%.

Пусть Кдиф1 = 10, Кдиф2 = 16,7. Тогда  .

.

Положим в схеме R2 = R3, R4 = R5, R6 = R7. Выберем R1 = 47 кОм из ряда E3 [9]; такой номинал сопротивления обеспечит требуемое входное сопротивление. Тогда  . Выберем R2 = R3 =

. Выберем R2 = R3 =  из ряда E96 [9].

из ряда E96 [9].

Кдиф2 = 16,7. Пусть R4 = R5 = 1 кОм.

Тогда R6 = R7 = Кдиф2·R4 = 16,7 кОм. Из ряда Е96 выбираем R6 = R7 = 16,5 кОм.

Рисунок 2 – Инструментальный усилитель на трёх ОУ

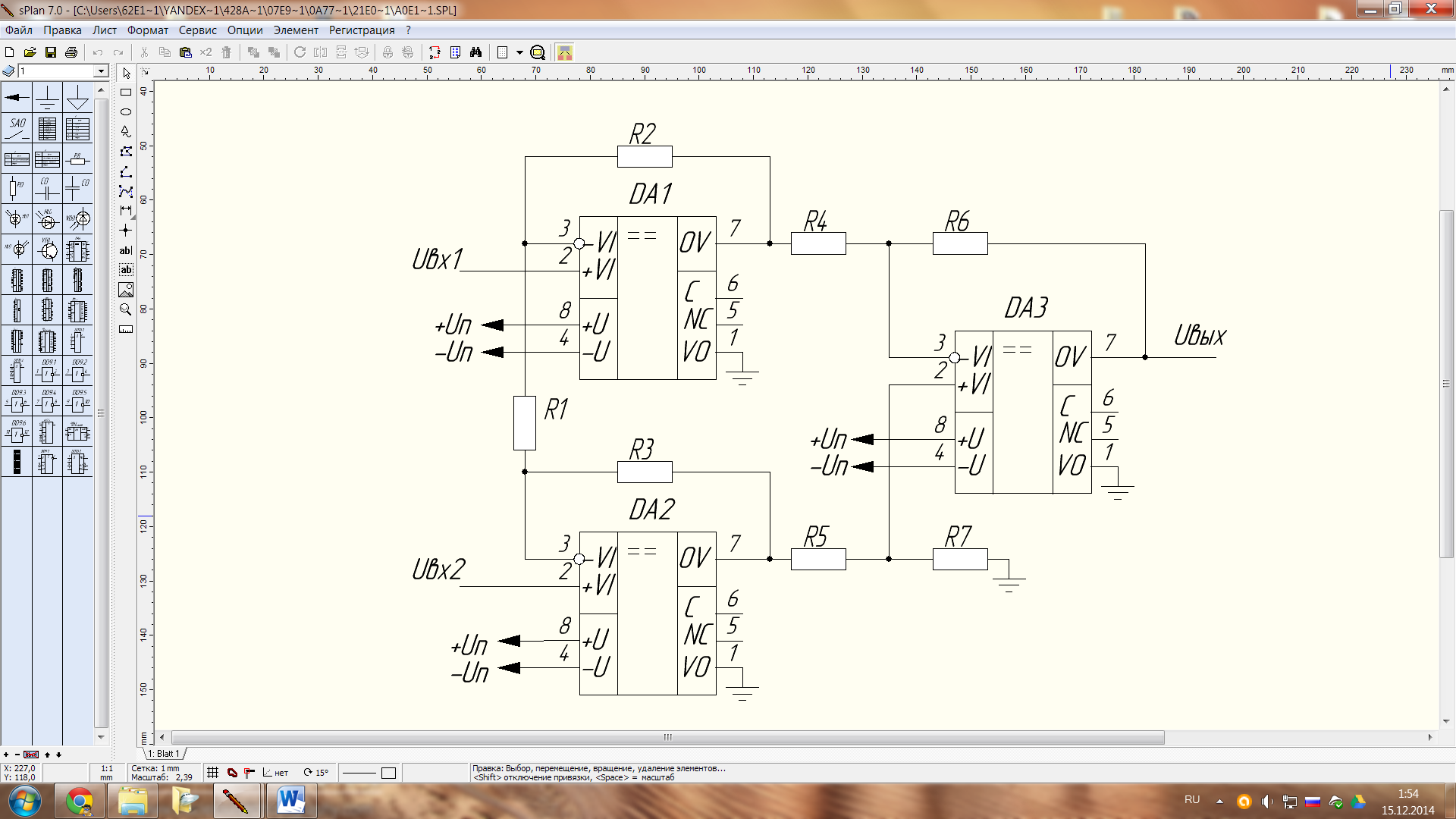

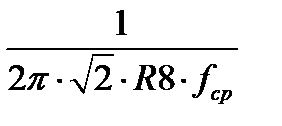

Разработаем ФНЧ. Фильтр нижних частот предотвращает пропускание шумов и сигналов с частотой выше самой высокочастотной информативной составляющей сигнала [6]. Для разрабатываемого прибора наиболее высокочастотная информативная составляющая сигнала равна fc макс = 100 Гц. Выберем частоту среза фильтра нижних частот с небольшим запасом fср = 110 Гц.

Согласно выводам, сделанным при расчёте функциональных параметров, используем фильтр Баттерворта 2-го порядка. В качестве схемной реализации фильтра Баттерворта 2-го порядка используем ФНЧ на повторителе.

Используем в качестве DA4 операционный усилитель К140УД22, резисторы С2-29 точности 1% и конденсаторы К10-17 точности 10%. Невысокая точность конденсаторов не окажет значительного влияния работу прибора, так как уход частоты среза на 10 процентов в любую из сторон не критичен.

Рисунок 3 – ФНЧ на повторителе

Зададим R8 = R9 = 47 кОм из ряда Е3. Тогда С2 =  = 22 нФ.

= 22 нФ.

Выберем С2 = 22 нФ из ряда Е6.

С1 = 2∙С2 = 44 нФ. Выберем С1 = 47 нФ из ряда Е6.

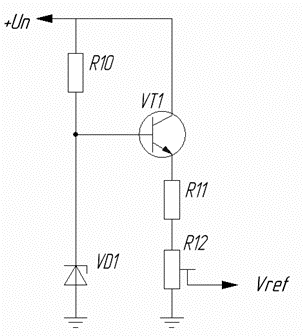

Для подачи опорного напряжения на АЦП необходимо реализовать стабилизатор напряжения. Эта необходимость связана с наличием помех на шине питания, вызванных переключениями режимов микросхем, наличием сетевых шумов и т. д. Используем схему стабилизатора напряжения на основе стабилитрона.

Рисунок 4 – Источник опорного напряжения

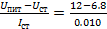

Выберем стабилитрон КС168В. Он имеет напряжение стабилизации 6,8 В при токе стабилизации 10 мА. Используем резисторы С2-29 точности 1%. Напряжение питания +Uп = 12 В. Для задания рабочего тока стабилитрона зададим R10 =  = 520 Ом. Выберем R10 = 510 Ом из ряда E24.

= 520 Ом. Выберем R10 = 510 Ом из ряда E24.

Резистор R11 необходим для ограничения максимального напряжения Vref, регулируемого с помощью резистора R12. Рассчитаем значения резисторов. Ограничим максимальное значение напряжения Vref.max = 5.5 В. Зададим ток эмиттера Iэ = 17 мА. Тогда R11 =  = 35 Ом, R12 =

= 35 Ом, R12 =  =

=  = 323 Ом. Выберем R11 модели С2-23 0,25 Вт 36 Ом 1%, резистор R12 модели СП5-16ВА 0,25 Вт 330 Ом 5%.

= 323 Ом. Выберем R11 модели С2-23 0,25 Вт 36 Ом 1%, резистор R12 модели СП5-16ВА 0,25 Вт 330 Ом 5%.

В качестве VT1 выберем n-p-n транзистор КТ315Б 20В 0,1А 0,15Вт.

Разработка цифровой части

Разработка делителя частоты.

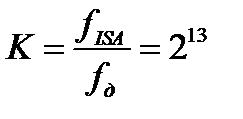

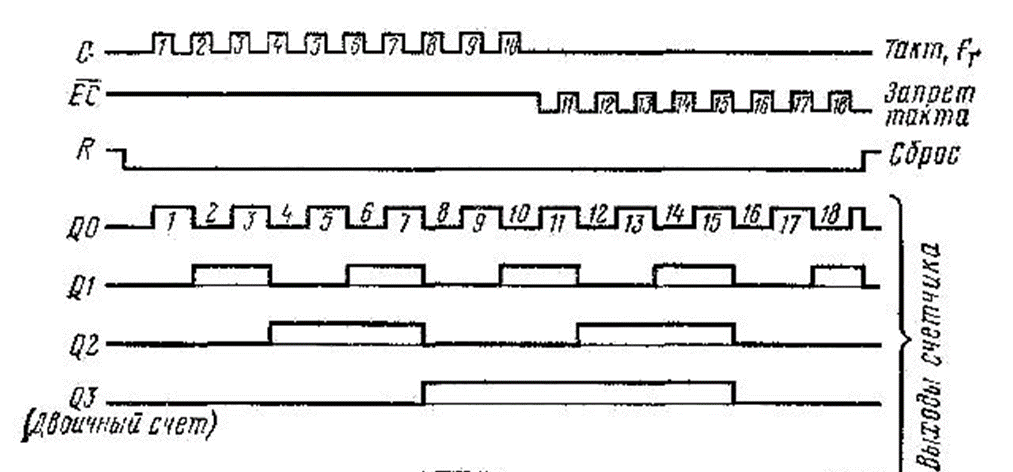

Начнём разработку цифровой схемы с генератора частоты дискретизации, им будет делитель тактовой частоты шины ISA на счётчике. Для рассчитанного ранее коэффициента деления  требуемая разрядность счётчика равна 13, для получения такой разрядности используем четыре четырёхразрядных счётчика, включённых каскадом. Выберем микросхему К1533ИЕ19, представляющую собой два четырёхразрядных синхронных двоичных счётчика, имеющих входы разрешения и асинхронного сброса.

требуемая разрядность счётчика равна 13, для получения такой разрядности используем четыре четырёхразрядных счётчика, включённых каскадом. Выберем микросхему К1533ИЕ19, представляющую собой два четырёхразрядных синхронных двоичных счётчика, имеющих входы разрешения и асинхронного сброса.

Рисунок 5 – Эпюры работы микросхемы К1533ИЕ19

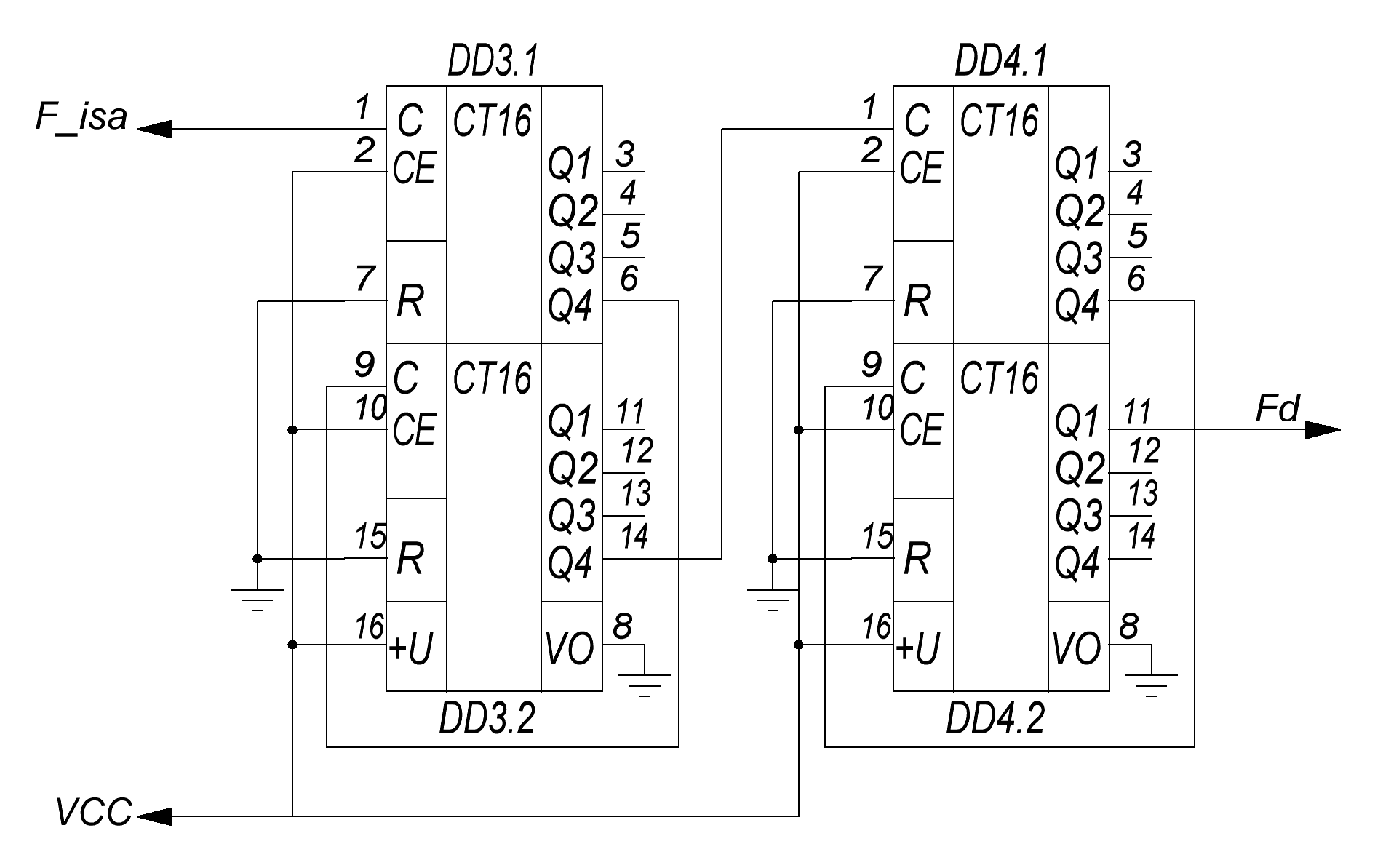

Составим принципиальную схему делителя частоты на двух микросхемах К1533ИЕ19 [8].

Рисунок 6 – Принципиальная схема делителя частоты

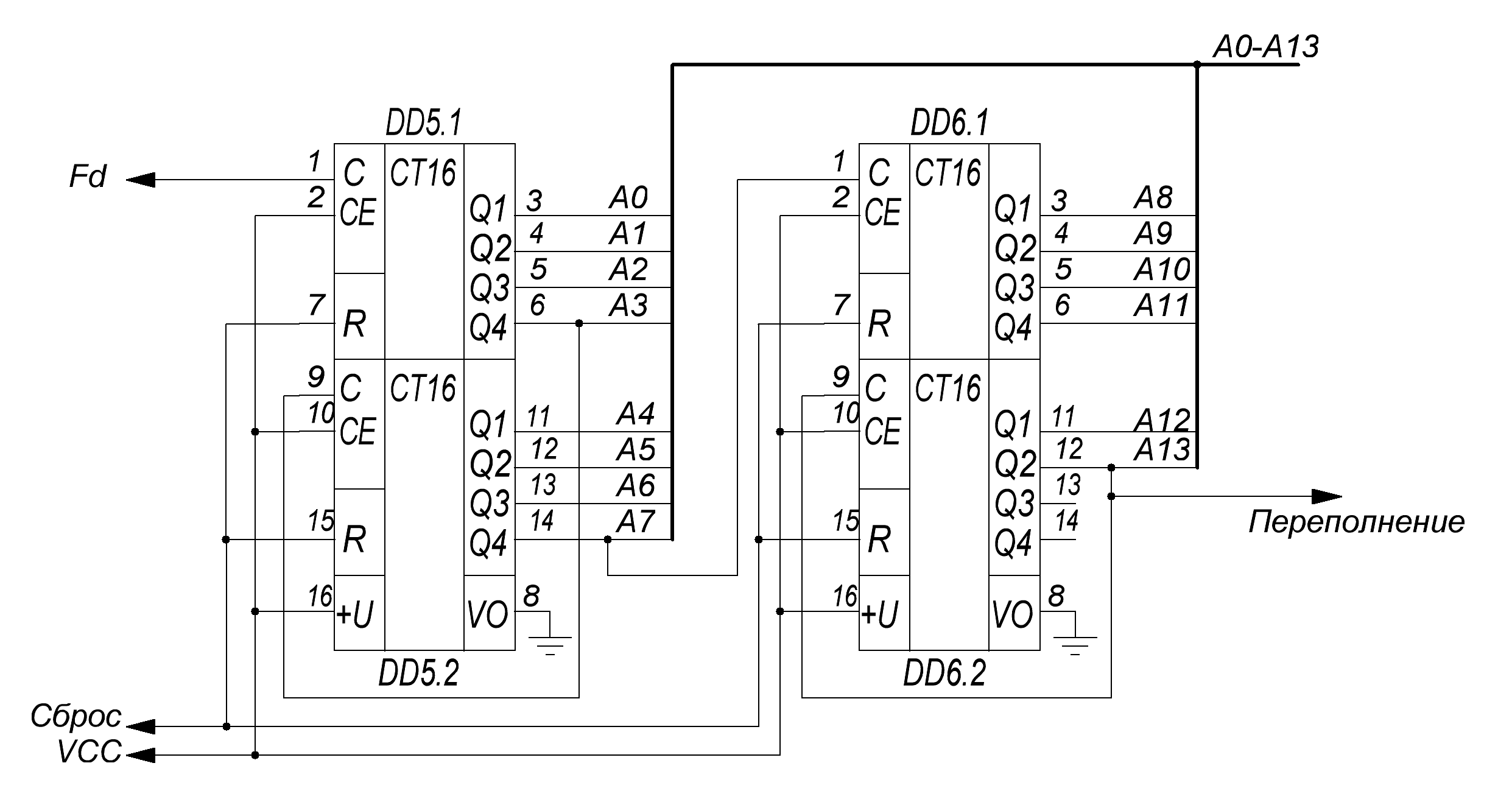

Разработка счётчика адреса.

Для разработки счётчика адреса воспользуемся также микросхемами К1533ИЕ19. Требуемая разрядность шины адреса 14 бит, значит потребуется две микросхемы К1533ИЕ19. Также требуется обеспечить возможность сброса счётчика для обнуления адреса и контроль переполнения счётчика. Для обеспечения контроля переполнения счётчика используем 13-й бит счётчика адреса.

Рисунок 7 – Принципиальная схема счётчика адреса

Выбор АЦП и БЗУ.

При выборе АЦП будем руководствоваться критериями, полученными ранее, а именно:

1. Разрядность АЦП: 8

2. Наличие входа запуска, входа опорного напряжения и выхода, сигнализирующего о состоянии АЦП, то есть о том, оцифровал ли он входные данные и готов ли он к новому запуску.

3. Напряжение питание должно быть равно либо 5 В, либо 12 В, что соответствует питающим напряжениям шины ISA.

Этим критериям соответствует микросхема АЦП AD7819. Время преобразования этого АЦП 4.5мкс, что позволяет использовать её на частотах до 200 кГц. Как ранее указывалось, в качестве опорного напряжения для АЦП зададим питающее напряжение шины ISA. Запускать АЦП будем с частотой дискретизации, формируемой делителем частоты Fd.

В качестве БЗУ выберем статическое ОЗУ, которое должно иметь объём 16 Кбайт. Этому требованию удовлетворяет ОЗУ W24129A, выпускаемое в 28-выводном DIP корпусе, требующая однополярное питание 5 В и имеющее выводы разрешения записи и чтения. Так как сигналы Qреж, ЧтВУ и сигнал разрешения записи инверсны, то есть активным уровнем является ноль, то для выполнения этого условия используем микросхему логического ИЛИ КР531ЛЛ1.

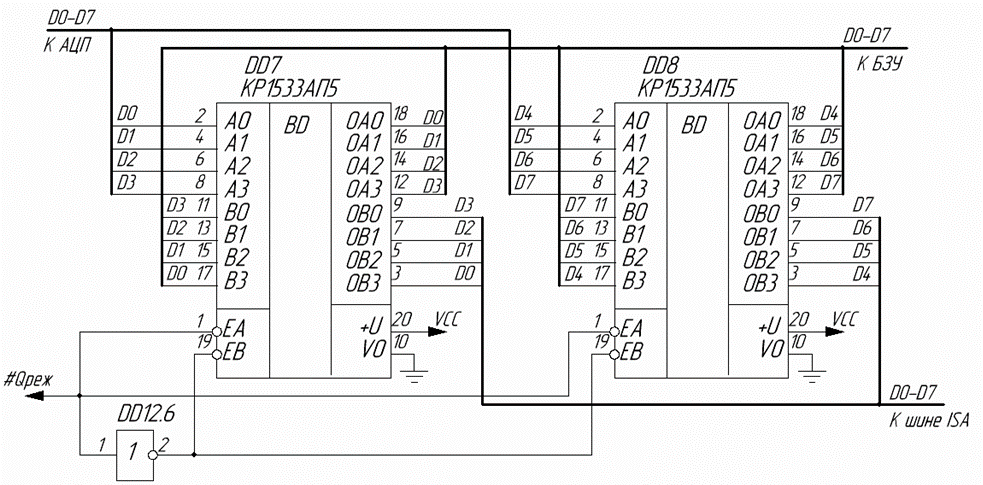

Разработка буфера данных.

Требуется разработать буферное устройство, осуществляющее передачу 8-ми битных данных в одном режиме работы из АЦП в БЗУ, а в другом режиме работы из БЗУ в ПК. Важным аспектом является присутствие Z-состояния на выходах, подключённых к шине ISA в первом режиме работы. В качестве буфера данных можно использовать две 8-х разрядных микросхемы шинного драйвера КР1533АП5.

Для реализации переключения направления передачи с помощью сигнала Qреж будем подавать его на входы EA неизменным, и на входы EB инвертированным с помощью микросхемы сшестерённого НЕ КР1533ЛН1.

Рисунок 8 – Принципиальная схема буфера данных

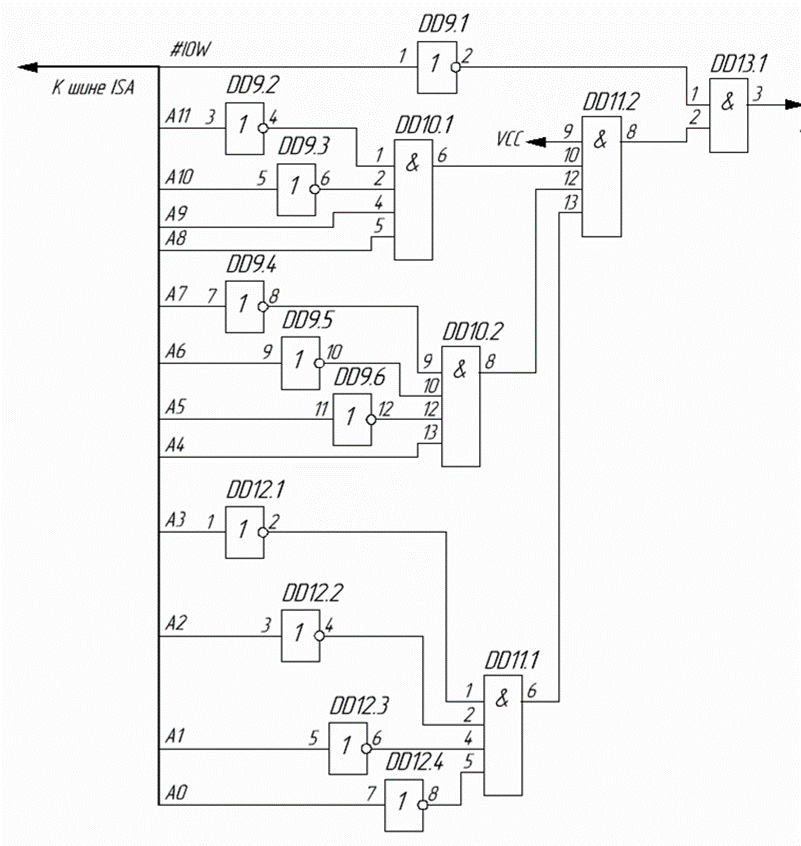

Кроме разработанных узлов необходимо использовать некоторую вспомогательную логику. Для формирования сигнала о завершении режима 2 – режима передачи данных в ПК, будем использовать селектор адреса. Пусть адрес 310h должен перевести адаптер в режим 1 – режим оцифровки. В двоичной системе этот адрес выглядит так 001100010000b. Тогда селектор адреса должен реализовывать следующую логическую функции:

у=  . Селектор адреса должен выдавать 1 только при активном сигнале шины #IOW.

. Селектор адреса должен выдавать 1 только при активном сигнале шины #IOW.

Для выполнения операции отрицания возьмем микросхемы сшестерённого НЕ КР1533ЛН1, для выполнения операции “И” – две микросхемы КР1533ЛИ6 сдвоенных четырехвходовых “И” и одну микросхему счетверенного И КР1533ЛИ8.

Рисунок 9 – Принципиальная схема селектора адреса

Для формирования сигнала о режиме работы системы Qреж используем RS-триггер, который сбрасываться сигналом с селектора адреса, а переводиться в единицу сигналом переполнения счетчика адреса. В качестве RS-триггера используем микросхему КР1533ТР2, содержащую четыре триггера.

Для передачи информации о режиме работы адаптера Qреж микропроцессорной системе по шине данных будем использовать шинный формирователь и линию D7 шины данных. Передача будет осуществляться выставлении на шину активного сигнала #IOR и при одновременном срабатывании селектора адреса. Задействуем один из каналов микросхемы КР1533АП5, микросхему “ИЛИ” КР531ЛЛ1 и “НЕ” КР1533ЛН1.

5 Расчёт погрешностей

Рассчитаем погрешность, вносимую усилителем. Первый каскад, состоящий из усилителей DA1 и DA2, усиливает дифференциальный сигнал в (1+ 2·R2/R1) раз, что составляет величину (1+ 2·210 кОм/47 кОм) = 9,94. Второй каскад, выполненный на DА3 в дифференциальном включении, усиливает сигнал в (R6/R4) раз, что составляет величину (16,5 кОм/1 кОм) = 16,5. Общий коэффициент усиления равен 9,94·16,5 = 164, в то время как в идеале он должен быть равен 167. При максимальном входном сигнале 30 мВ абсолютная погрешность составит (167–164) 30 мВ = 90 мВ. Относительная погрешность составит 90 мВ/(167·30 мВ) = 1,8%.

ФНЧ выполнен на повторителе, поэтому его коэффициент передачи в полосе пропускания можно с достаточной точностью принять равным 1.

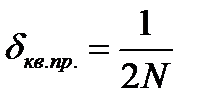

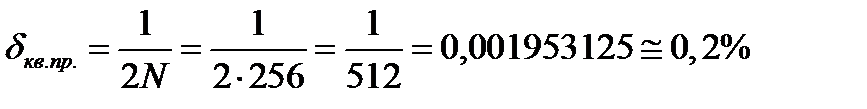

Согласно [10], приведённая погрешность квантования определяется как  , где N – число ступеней квантования АЦП. Для 8-разрядного АЦП N = 28 =256, откуда приведённая погрешность квантования составляет

, где N – число ступеней квантования АЦП. Для 8-разрядного АЦП N = 28 =256, откуда приведённая погрешность квантования составляет  . Абсолютная погрешность, вносимая нелинейностью функции преобразования, также не превышает половины ступени квантования [10]. Приведённая погрешность от нелинейности для 8-разрядного АЦП составляет δнелин.пр. = 0,2%. Максимальная погрешность, вызванная влиянием обоих факторов (квантование и нелинейность функции преобразования), есть алгебраическая сумма этих двух погрешностей: δАЦП = δнелин + δкв = 0,4%.

. Абсолютная погрешность, вносимая нелинейностью функции преобразования, также не превышает половины ступени квантования [10]. Приведённая погрешность от нелинейности для 8-разрядного АЦП составляет δнелин.пр. = 0,2%. Максимальная погрешность, вызванная влиянием обоих факторов (квантование и нелинейность функции преобразования), есть алгебраическая сумма этих двух погрешностей: δАЦП = δнелин + δкв = 0,4%.

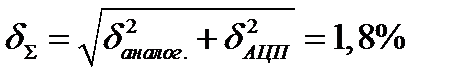

Суммарная погрешность не превысит  , что удовлетворяет требованиям технического задания.

, что удовлетворяет требованиям технического задания.

Заключение

Устройство, разработанное в данном курсовом проекте, может определить не только поражение мышцы, но и оценить, какие в ней произошли изменения, получить результат с необходимой точностью, записать его в память устройства и по запросу микропроцессорной системы отправить его на обработку в ПК по шине ISA. Погрешность измерения разработанного адаптера составляет 1,8%, что удовлетворяет требованиям технического задания.