Разработка структурной схемы сумматора-умножителя

Структурная схема сумматора-умножителя 1-го типа для алгоритма умножения “В” представлена на Схеме 1.

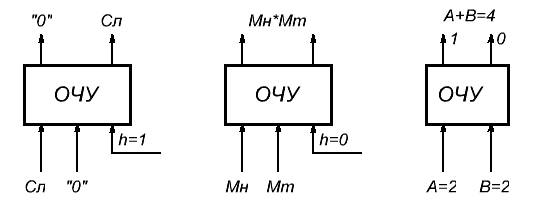

Если устройство работает как сумматор (на входе mul/sum – “1”), то оба слагаемых последовательно (за 2 такта) заносятся в регистр множимого, а на управляющий вход формирователя дополнительного кода (ФДК) F2 поступает «1». Следует учесть, что числа представлены в форме с плавающей запятой. Поэтому, прежде чем складывать мантиссы, необходимо выровнять порядки. В блоке порядков необходимо обеспечить сравнение порядков, используя сумматор порядков, и в зависимости от знака результата сдвигать первое или второе слагаемое. На выходах ФДК формируется дополнительный код одного из слагаемых с учетом знака. Это слагаемое может быть записано в регистр результата, при этом управляющие сигналы, поступающие на входы «h» всех ОЧУ, дают возможность переписать на выходы ОЧУ разряды слагаемого без изменений.При необходимости выравнивания порядков в регистре-аккумуляторе может выполняться сдвиг мантиссы первого слагаемого. Если на вход «h» поступает «0», то ОЧУ перемножает разрядыМн и Мт.

Одноразрядный четверичный сумматор предназначен для сложения двух двоично-четверичных цифр, подаваемых на его входы.

В ОЧС первое слагаемое складывается с нулем, так как на старших выходах ОЧУ будут формироваться только коды нуля. Затем первое слагаемое попадает в регистр-аккумулятор, который изначально обнулен. На втором такте второе слагаемое из регистра множимого через цепочку ОЧУ и ОЧС попадает в аккумулятор, где складывается с первым слагаемым. Таким образом, аккумулятор (накапливающий сумматор) складывает операнды и хранит результат. Разрядность аккумулятора должна быть на единицу больше, чем разрядность исходных слагаемых, чтобы предусмотреть возможность возникновения при суммировании переноса.

Если устройство работает как умножитель (на входе mul/sum – “0”), то множимое и множитель помещаются в соответствующие регистры, а на управляющий вход ФДК F2 поступает «0». Диада множителя поступает на входы преобразователя множителя (ПМ). Задачей ПМ является преобразование диады множителя в дополнительном коде. В регистре множителя в конце каждого такта умножения содержимое сдвигается на 2 двоичных разряда, и в последнем такте умножения регистр обнуляется. Выход 2 ПМ переходит в единичное состояние, если текущая диада содержит отрицание (01). В этом случае инициализируется управляющий вход F1 формирователя дополнительного кода (ФДК), и на выходах ФДК формируется дополнительный код множимого с обратным знаком (умножение на -1). Принцип работы ФДК в зависимости от управляющих сигналов приведен в табл.1.

Табл.1 Режимы работы формирователя дополнительного кода.

| Сигналы на входах ФДК | Результат на выходах ФДК | |

| F1 | F2 | |

| Дополнительный код множимого | ||

| Дополнительный код слагаемого | ||

| Меняется знакМн | ||

| Меняется знак слагаемого |

На выходах 2, 3 ПМ формируются диады преобразованного множителя, которые поступают на входы ОЧУ вместе с диадами множимого.

ОЧУ предназначен лишь для умножения двух четверичных цифр. Если в процессе умножения возникает перенос в следующий разряд, необходимо предусмотреть возможность его прибавления. Для суммирования результата

умножения текущей диадыМн · Мт с переносом из предыдущей диады предназначены ОЧС. Следовательно, чтобы полностью сформировать частичное произведение четверичных сомножителей, необходима комбинация цепочек ОЧУ и ОЧС. Частичные суммы формируются в аккумуляторе.На первом этапе он обнулен, и первая частичная сумма получается за счет сложения первого частичного произведения (сформированного на выходах ОЧС) и нулевой частичной суммы (хранящейся в аккумуляторе). Далее в аккумуляторе происходит сложение i-й частичной суммы с (i+1)-м частичным произведением, результат сложения сохраняется. Содержимое аккумулятора сдвигается на один четверичный разряд вправо в конце каждого такта умножения по алгоритму «В».

На четырех выходах ОЧУ формируется результат умножения диад

Мн·Мт. Максимальной цифрой в диаде преобразованного множителя является двойка, поэтому в старшем разряде произведения максимальной цифрой может оказаться только «1» :

3 · 2 = 1 2.

maxmaх

Мн Мт

Это означает, что на младшие входы ОЧС никогда не поступят диады цифр, соответствующие кодам «2» и «3», следовательно, в таблице истинности работы ОЧС будут содержаться 16 безразличных входных наборов. Частичные суммы хранятся в аккумуляторе и регистре множителя, так как алгоритм умножения «А» предполагает возможность синхронного сдвига этих устройств. Количество тактов умножения определяется разрядностью Мт.