Кафедра робототехнических систем

Кафедра робототехнических систем

ФУНКЦИОНАЛЬНЫЕ УЗЛЫ

ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

к выполнению лабораторных работ № 1-6

по дисциплине «Вычислительная техника»

для студентов специальности 220402

"Роботы и робототехнические системы"

очной формы обучения

Воронеж 2011

Составители: канд. техн. наук М.И. Герасимов,

канд. техн. наук Д.А. Ефремов,

Н.С. Лесных

УДК 681.3-181.48:621.865.8

Функциональные узлы вычислительной техники: методические указания к выполнению лабораторных работ № 1-6 по дисциплине "Вычислительная техника" для студентов специальности 220402 "Роботы и робототехнические системы" очной формы обучения / ГОУ ВПО «Воронежский государственный технический университет»; сост. М.И. Герасимов, Д.А. Ефремов, Н.С. Лесных. Воронеж, 2011. 80 с.

Методические указания содержат общие положения по организации лабораторных работ, теоретические сведения об устройстве и принципах работы исследуемых комбинационных и последовательностных узлов ВТ (шифраторов, коммутаторов, триггеров и счетчиков), предварительное и рабочее задания, определяющие порядок исследования, контрольные вопросы.

Предназначены для студентов 3 курса очной формы обучения.

Методические указания подготовлены в электронном виде в текстовом редакторе MS Word 2003 и содержатся в файле МУ_лаб_ВТ.doc.

Ил. 34. Библиогр.: 10 назв.

Рецензент канд. техн. наук, доц. Ю.С. Слепокуров

Ответственный за выпуск зав. кафедрой д-р техн. наук,

проф. А.И. Шиянов

Издается по решению редакционно-издательского совета Воронежского государственного технического университета

| |

ОБЩИЕ ПОЛОЖЕНИЯ

Данные методические указания выполнены в виде электронного документа с использованием аппарата гиперссылок и других средств повышения наглядности и удобства использования. Для совмещения на дисплее текста МУ и программы коммутации схем рекомендуется использовать режим «В окне» + «Веб-документ», при этом размер шрифта выбирать масштабом.

ОРГАНИЗАЦИЯ ЦИКЛА ЛАБОРАТОРНЫХ РАБОТ

Состав и задачи цикла работ

Программа дисциплины "Вычислительная техника" предусматривает проведение для студентов очной формы обучения шести лабораторных работ (34 часа).

| Наименование лабораторной работы | Кол-во часов |

| 1. Изучение лабораторного стенда, овладение навыками коммутации схем на стенде | |

| 2. Синтез комбинационного автомата | |

| 3. Синтез и исследование двоичных шифраторов | |

| 4. Исследование коммутаторов информационных потоков | |

| 5. Исследование триггеров | |

| 6. Исследование счетчика / делителя | |

| ВСЕГО |

В начале цикла проводится обучение студентов правилам безопасности, действующим в лаборатории, и правилам пользования лабораторным оборудованием (стендом, осциллографом и другими приборами). После получения инструктажа каждый студент дает обязательство строго соблюдать данные правила, расписываясь в соответствующем журнале. В случае нарушения правил студенты могут быть отстранены от работы и подвергнуты повторной сдаче зачета по технике безопасности.

Содержание цикла лабораторных работ – изучение свойств основных функциональных узлов ВТ, выполненных на цифровых микросхемах. В результате студент должен научиться читать принципиальные схемы узлов ВТ, а также синтезировать эти узлы, приобрести начальные навыки их экспериментального исследования.

Проведение каждой лабораторной работы включает этапы подготовки, выполнения работы, оформления и защиты отчета. Каждая лабораторная работа требует ориентировочно 2 часа на подготовку квыполнению и 2 часа на оформление отчета и подготовку к его защите. Это время предусмотрено в учебном плане как самостоятельная работа.

Подготовка к выполнению лабораторной работы

При подготовке к работе следует:

- изучить теоретические сведения, приведенные в методических указаниях и рекомендованной литературе;

- составить заготовку отчета с названием работы, планом эксперимента (в развернутой форме), заголовками подлежащих заполнению таблиц, диаграмм и т.п.

Основной стадией подготовки к работе является составление плана эксперимента (ПЭ) – в данном цикле для изучения лабораторного стенда либо исследования различных функциональных узлов и микросхем. Бригада, не подготовившая ПЭ, к выполнению работы не допускается. План должен включать:

- цель работы (приведена в методических указаниях к каждой работе).

- функциональный анализ исследуемого устройства (узла, микросхемы),

- перечень дополнительных элементов, необходимых для исследования (рекомендованы в МУ),

- принципиальную схему (схемы) эксперимента,

- перечень подлежащих выполнению процедур, названия и местонахождение анализируемых сигналов, методику измерений или исследований.

Функциональный анализ начинают с уяснения назначения устройства. Затем следует составить список его функций, изучив соответствующую литературу, ссылки на которую приведены в МУ к каждой работе. Если устройство имеет несколько функций, следует определить их взаимное влияние, в частности приоритеты. Для микросхемы следует соотнести каждый вход, выход, двунаправленный вывод и соответствующую функцию, объединив выводы в группы по признаку функциональной связанности (например, однородные выводы). Удобно при этом пользоваться структурными и функциональными схемами устройств, а при изучении микросхем – их условными графическими обозначениями. Уяснив назначение входов, следует определить, какое состояние должны иметь те из них, которые не исследуются на данной стадии эксперимента.

Далее следует выбрать дополнительные элементы, необходимые для исследования микросхемы (делитель частоты и т.п.), и составить принципиальную схему (схемы) эксперимента – схему соединения этих элементов, исследуемой схемы и полей стенда. Следует предусмотреть также подачу напряжений питания на все схемы, потенциалов "лог. 0" и "лог. 1" – на неиспытываемые входы (в частности, на прямые динамические входы рекомендуется подавать "лог. 1", а на инверсные – "лог. 0"), сигналов начальной установки и т.п. Внутри УГО каждой микросхемы следует отметить ее расположение на стенде (контактные колодки +1, +2, +3). Каждомупроводнику (линия связи между элементами) следует присвоить уникальное для схемы имя. Для входных и выходных цепей рекомендуется использовать имена, полученные из таблицы истинности, для промежуточных цепей – связанные с именем/номером выхода, подключенного к данной цепи (например, для выхода +2:8 удобно имя «28»), либо с функцией сигнала (например, «X2А2#» для сигнала X2 после логического умножения на А2 и инвертирования). Все элементы схемы следует пронумеровать по правилу, приведенному в /1/, в соответствии с правилом «слева – столбцами сверху вниз – направо». При разнесенном изображении нескольких одинаковых элементов (например, логических элементов), содержащихся в одном корпусе, им присваивают одно и то же обозначение, например DD12, дополняя его для каждого элемента порядковым номером через точку (DD12.1, DD12.2, DD12.3…) в соответствии с тем же правилом в пределах устройства.

Следующим этапом планирования является составление (на основе результатов функционального анализа устройства) перечня подлежащих выполнению процедур. В перечне следует определить вид подаваемых на входы сигналов и порядок их подачи, а также наименование входных, выходных и промежуточных сигналов, подлежащих выводу на индикацию. Рекомендуется разбить эксперимент на стадии, каждая из которых должна соответствовать исследованию одной функции, и дать им названия (например, по анализируемой функциональной группе входов). В состав эксперимента должно входить исследование функционирования устройства как при подаче стандартных комбинаций входных воздействий, так и при конфликтных ситуациях (для проверки приоритетов, защит и т.п.) Полученный перечень должен иметь наглядный вид и сопровождаться необходимым комментарием.

Меню и панель инструментов.

Для удобства использования программы основные операции продублированы на панели инструментов. Операции объединены в группы по назначению и сгруппированы в соответствующие пункты меню.

· «Файл»

o  «Новая схема» – предназначена для сброса программы в начальное состояние и очистки текущей схемы.

«Новая схема» – предназначена для сброса программы в начальное состояние и очистки текущей схемы.

o  «Открыть схему» – при нажатии отображается стандартное окно открытия файла.

«Открыть схему» – при нажатии отображается стандартное окно открытия файла.

Будьте внимательны! Сохраняйте чаще набранную вами схему. При выполнении команд «Новая схема» и «Открыть схему» все несохраненные данные будут утеряны.

o  «Сохранить» – сохраняет текущую схему в файл.

«Сохранить» – сохраняет текущую схему в файл.

o  «Сохранить как» – позволяет сохранить текущую схему под другим именем, при нажатии отображается стандартное окно сохранения файла.

«Сохранить как» – позволяет сохранить текущую схему под другим именем, при нажатии отображается стандартное окно сохранения файла.

o  «Выход» – завершение работы программы

«Выход» – завершение работы программы

· «Компонент» – режим редактирования компонентов используется только при пополнении базы данных на компоненты, поэтому в данных методических указаниях подробно не рассмотрен.

Внимание! Во избежание отказа работы программы, а также конфликта с преподавателем L, крайне не рекомендуется изменять компоненты и удалять их из программы.

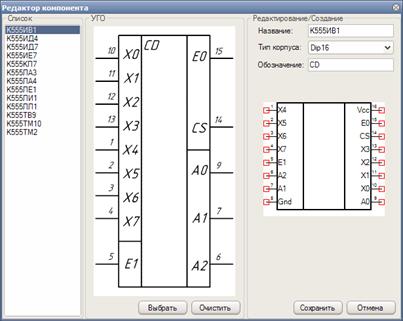

o  «Создать/Изменить» – открытие окна для редактирования компонентов (рис. 6).

«Создать/Изменить» – открытие окна для редактирования компонентов (рис. 6).

Рис. 6. Окно редактирования компонентов.

o

«Удалить» – открытие окна для удаления компонентов (рис. 7)

«Удалить» – открытие окна для удаления компонентов (рис. 7)

· «Устройство»

o  «Соединиться с устройством» – выполняется соединение компьютера со стендом (убедитесь при этом, что кабель для передачи данных подключен и питание стенда включено)

«Соединиться с устройством» – выполняется соединение компьютера со стендом (убедитесь при этом, что кабель для передачи данных подключен и питание стенда включено)

o  «Отсоединиться» – прерывание связи с устройством.

«Отсоединиться» – прерывание связи с устройством.

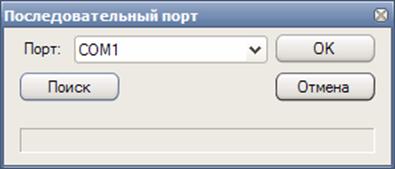

Внимание! В случае неготовности стенда или подключения его к другому COM-порту появится диалоговое окно, показанное на рис. 8. При нажатии на кнопку «Поиск» выбор подходящего COM-порта произойдет автоматически.

Рис. 8. Выбор COM-порта для связи с устройством

· «Справка»

o «Помощь»

o «О программе»

· «Генератор G1»:

o  Кнопка «Однократный импульс»;

Кнопка «Однократный импульс»;

o  «Запуск генератора G1» – запуск генератора тактовых импульсов ГТИ, подробнее описано ниже;

«Запуск генератора G1» – запуск генератора тактовых импульсов ГТИ, подробнее описано ниже;

o  «Остановка генератора G1» – остановка генератора тактовых импульсов ГТИ, подробнее описано ниже.

«Остановка генератора G1» – остановка генератора тактовых импульсов ГТИ, подробнее описано ниже.

· «Генератор G2» –  кнопка «Однократный импульс».

кнопка «Однократный импульс».

·  Кнопка «Стереть диаграмму».

Кнопка «Стереть диаграмму».

Диаграмма состояния выходов

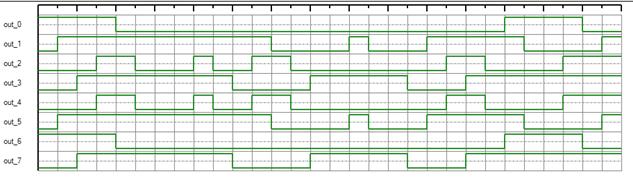

Диаграмма состояния выходов (рис. 9) отображает логический уровень сигналов (лог.0 или лог. 1), подключенных к выходам редактора принципиальной схемы. Сдвиг диаграммы происходит слева направо.

Рис.9. Диаграмма состояния выходов

Редактор принципиальной схемыпредназначен для построения схемы соединений. Вид редактора принципиальной схемы показан на рис. 10.

Рис. 10. Редактор принципиальной схемы

На рисунке обозначено:

1. Генератор тактовых импульсов (ГТИ) G1 – предназначен для получения последовательности импульсов заданной частоты. Частота импульсов задается вручную (от 1 Гц до 5 Гц), кроме того ГТИ может работать в ручном режиме выдачи однократного импульса.

2. Генератор одиночных импульсов (ГОИ) G2 – предназначен для получения импульсов при нажатии на кнопку тактирования, расположенную на верхней панели стенда, а также при нажатии на соответствующую кнопку на панели инструментов.

3. Поле констант (ввода), точки подключения которого предназначены для управления соответствующими входами исследуемых микросхем. Значения на входах (лог.0 или лог. 1) устанавливаются вручную щелчком мыши.

4. Поле разъема микросхемы 1

5. Поле разъема микросхемы 2

6. Поле разъема микросхемы 3

7. Поле индикации, точки подключения которого предназначены для присоединения к ним соответствующих выходов исследуемых микросхем. В соответствии с уровнями сигнала на выходах собранной схемы меняется диаграмма состояния выходов.

8. Виртуальный источник питания.

9. Виртуальная общая шина.

10. Список доступных библиотечных микросхем для разъема 3.

11. Список доступных библиотечных микросхем для разъема 2.

12. Список доступных библиотечных микросхем для разъема 1.

На схеме есть общие для всех элементов компоненты (рис. 11).

Рис. 11. Общее представление вывода для всех компонентов

Основой виртуальных цепей является вывод компонента – вход или выход. Имя вывода и номер вывода задаются в режиме редактирования элемента при создании вывода и не должны изменяться при наборе принципиальной схемы.

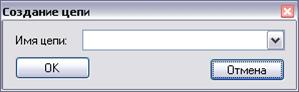

Точка подключения – это основа цепей. Неподключенная точка обозначается красным квадратом. При левом щелчке мыши на выводе выдается диалог создания или изменения имени цепи (рис. 12) со списком, в котором указаны существующие цепи.

Рис. 12. Создание или изменение имени цепи

В окне «Имя цепи» можно ввести новое имя или выбрать одно из существующих.

Для удаления цепи можно убрать ее имя из списка либо щелкнуть правой клавиши мыши на имени цепи в схеме.

Цепи, связывающие два и более выводов, обозначаются на схеме соединений синим цветом, незаконченные (подключенные только к одному выводу) – красным.

Будьте внимательны! Схема становится доступной для редактирования только после отключения лабораторного стенда от компьютера.

Пользователь может в любое время вызвать справку по работе с программой из главного меню.

Порядок исследования узла

1. Поместите в колодки выключенного стенда необходимые микросхемы (см. «Порядок установки микросхем») в соответствии с принципиальной схемой, включите питание, щелкните на панели программы ПК кнопку «Соединиться с устройством» или аналогичную (в верхней или нижней части экрана).

2. Подавая на схему входные сигналы от генераторов и/или источника констант согласно плану эксперимента, наблюдайте значения выходных сигналов в поле 7 редактора и на диаграммах. При необходимости используйте кнопку очистки диаграммы  и линейку прокрутки вперед-назад

и линейку прокрутки вперед-назад

под диаграммой.

под диаграммой.

2. Результаты сверяйте с заданием – таблицами истинности, диаграммами и т.п.

3. В случае несоответствующих ожиданиям результатов переходите к поиску неисправностей:

§ проверьте правильность установки значений входных сигналов;

§ еще раз проверьте правильность и полноту введенных связей;

§ проверьте правильность установки микросхем в колодках;

§ определите логически вид сигналов на входах последнего (выходного) элемента, выведите сигналы на этих входах в поле 7 редактора и проверьте соответствие;

§ обнаружив несоответствие, продвигайтесь от выхода ко входу, анализируя каждый переход сигнала между элементами до выяснения причины несоответствия;

§ при несоответствии функционирования какого-либо элемента его таблице истинности измерьте уровни логического нуля на входах и выходах и сделайте вывод об исправности элемента либо стенда, замените элемент (выключив питание) или стенд;

§ при отсутствии выявленных причин обратитесь к преподавателю.

Лабораторная работа № 1

ЦЕЛЬ РАБОТЫ

Изучить назначение, основные технические данные и характеристики, органы управления лабораторного стенда и освоить работу на нем. Для приобретения практических навыков провести исследование на стенде делителя частоты на триггере К555ТМ2.

КОНТРОЛЬНЫЕ ВОПРОСЫ

1. Перечислите, что нужно сделать при подготовке к каждой лабораторной работе.

2. Перечислите, какие разделы должен включать план эксперимента – исследования узла или микросхемы.

3. Перечислите процедуры, выполняемые в ходе функционального анализа исследуемого узла (микросхемы).

4. Перечислите процедуры, выполняемые в ходе составления и оформления принципиальной схемы эксперимента.

5. Опишите структуру лабораторного стенда, расположение и назначение органов управления, элементов индикации, разъемов стенда, правила установки микросхем в разъемы.

6. Опишите общий вид окна программы и назначение его элементов.

7. Опишите общий вид окна редактора принципиальной схемы и назначение его элементов.

8. Перечислите основные этапы ввода схемы соединений исследуемого узла.

9. Перечислите основные этапы исследования узла на базе микросхем и рекомендуемый порядок поиска неисправностей.

10. Приведите результаты проверки работы генераторов стенда и поля входов (констант).

11. Покажите преподавателю записанную вами схему и продемонстрируйте ее работу.

12. Покажите, какие сигналы дают отчет числа импульсов в прямом коде.

СИНТЕЗ КОМБИНАЦИОННОГО АВТОМАТА

ПО ЗАДАННОЙ ВРЕМЕННОЙ ДИАГРАММЕ

Лабораторная работа № 2

ЦЕЛЬ РАБОТЫ

1.1. Изучить алгоритм синтеза комбинационного цифрового автомата на основе временнóй диаграммы.

1.2. Отработать практические навыки сборки и наладки макетных образцов функциональных узлов вычислительной техники.

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

Рассмотрим комбинационный цифровой автомат, функционально представленный на рис. 2.1. Здесь Х1…Х3 – входы, на которые подаются комбинации сигналов, Y1…Y4 – выходы, на которых возникают логические уровни в соответствии с логикой работы данного автомата. Эту логику можно задать таблицей истинности, набором формул Yi = f (X1…X3), текстовым описанием («если…, то…») и другими способами.

Нередко от комбинационного автомата требуется формирование выходных сигналов в соответствии с известной временнóй диаграммой, например, такой, как на рис. 2.2. В этом случае алгоритм синтеза автомата сводится к последовательности действий:

Нередко от комбинационного автомата требуется формирование выходных сигналов в соответствии с известной временнóй диаграммой, например, такой, как на рис. 2.2. В этом случае алгоритм синтеза автомата сводится к последовательности действий:

ü составить таблицу истинности, рассмотрев значение каждой выходной переменной для всех сочетаний входных сигналов;

ü составить по таблице СДНФ или СКНФ для каждой выходной переменной;

ü выбрать элементную базу и в соответствии с нею преобразовать выражения для каждой функции;

ü изобразить принципиальную схему автомата;

ü проверить логику его работы на соответствие временной диаграмме;

ü собрать устройство из выбранных микросхем и проверить его функционирование.

Рис. 2.2

Рис. 2.2

В частности, функция Y4 для диаграммы, приведенной на рис. 2.2, представляется так:

| X1 | ||||||||

| X2 | ||||||||

| X3 | ||||||||

| … | ||||||||

| Y4 |

Отсюда  .

.

3. ПОРЯДОК ВЫПОЛНЕНИЯ

ЛАБОРАТОРНОЙ РАБОТЫ

3.1. Предварительное задание

3.1.1. По конспекту лекций и литературным источникам, например /4-6/, изучите материал о составлении СДНФ и СКНФ логической функции и ее преобразовании.

3.1.2. По материалам п. 2, конспекту лекций и литературным источникам изучите алгоритм синтеза комбинационного цифрового автомата на основе временной диаграммы.

3.1.3. По конспекту лекций, справочникам (например, /6-10/) и приложениям 1, 2 изучите функциональные возможности логических микросхем И, ИЛИ, НЕ. Распечатайте оба приложения для работы в лаборатории. В приложении 1 доработайте те выражения для столбца «Функция», которые заканчиваются на знак равенства, преобразуя их по де Моргану.

3.1.4. Подготовьте заготовку отчета, включив в нее название и цель работы, функциональное представление проектируемого автомата в сочетании с таким же представлением формирователя сигналов ФС (рис. 2.3). В качестве ФС будем использовать делитель частоты, соответствующий п. 12 предыдущей работы.

3.1.4. Подготовьте заготовку отчета, включив в нее название и цель работы, функциональное представление проектируемого автомата в сочетании с таким же представлением формирователя сигналов ФС (рис. 2.3). В качестве ФС будем использовать делитель частоты, соответствующий п. 12 предыдущей работы.

Включите в заготовку принципиальную схему этого делителя частоты (на одном корпусе ТМ2). Выбранные выходные сигналы переименуйте в Х1, Х2, Х3, начиная с G1.

3.2. Рабочее задание

3.2.1. Получите у преподавателя временную диаграмму, выполните действия, предусмотренные алгоритмом синтеза комбинационного цифрового автомата. Занесите в отчет вариант задания, соответствующую таблицу истинности для Y1…Y4, СДНФ или СКНФ этих функций.

3.2.2. Выполните такие преобразования СДНФ или СКНФ, чтобы реализовать каждую из функций с минимальным количеством и разнообразием микросхем (минимальный элементный базис). Например,  удобно реализовывать на одной микросхеме ЛА3, используя один элемент для инвертирования Х1, второй – для логического умножения с инвертированием, третий – для повторного инвертирования результата

удобно реализовывать на одной микросхеме ЛА3, используя один элемент для инвертирования Х1, второй – для логического умножения с инвертированием, третий – для повторного инвертирования результата  . Для выражений вида YK = MAVMBVMC, где MA, MB, MC – три минтерма (конъюнктивных выражения), удобно использовать преобразование (MAVMB)V(MAVMC), где в качестве MA следует выбрать тот из минтермов, который позволит оптимально упростить обе скобки (вынести общие множители). В скобках должны остаться функции неравнозначности, эквивалентности, импликации, которые затем следует выразить так, чтобы их можно было реализовать в минимальном элементном базисе.

. Для выражений вида YK = MAVMBVMC, где MA, MB, MC – три минтерма (конъюнктивных выражения), удобно использовать преобразование (MAVMB)V(MAVMC), где в качестве MA следует выбрать тот из минтермов, который позволит оптимально упростить обе скобки (вынести общие множители). В скобках должны остаться функции неравнозначности, эквивалентности, импликации, которые затем следует выразить так, чтобы их можно было реализовать в минимальном элементном базисе.

3.2.3. Составьте по результатам преобразования принципиальные схемыи приведитеихв отчете.При этом в качестве инверторов следует применять элементы «исключающее ИЛИ» и «И-НЕ», но так, чтобы в схеме было минимальное количество корпусов микросхем, а в каждой из них использовалось максимальное количество элементов (клапанов). При необходимости использовать константу лог.1 изображайте на входе логического элемента проводник с именем L1.

3.2.4. Запустите на ПК программу VirtualPCB, загрузите схему ЛР1_2, переименуйте выходные сигналы как в заготовке отчета, удалите индикацию ненужных сигналов, сохраните схему как ЛР2_1. Разметьте каждую из разработанных в п. 3.2.3 схем как описано в разделе «Подготовка к выполнению лабораторной работы» в соответствии с указаниями, приведенными далее. Для расположения микросхем используйте разъемы +2 и +3. Вызовите обозначения выбранных микросхем в окно редактора схем VirtualPCB, откройте для них окно УГО и нанесите распиновку на УГО в схеме, занесенной в ваш отчет, следуя правилам, приведенным в /1/.

3.2.5. Наберите в редакторе на основе ЛР2_1 разработанную вами схему для реализации той из функций Y, СДНФ которой включает 3 конъюнкции и которая указана на выданной диаграмме значком P. Сигнал L1 снимайте с одной из линий поля констант. Проверьте распиновку, вызывая УГО использованных микросхем. На индикацию под линиями Х1, Х2, Х3 выведите сигнал Y. Константы L1, R# и S# установите в лог.1.

3.2.6. Проверьте результат ввода, как указано выше, в частности проверьте отображение всех выходных сигналов в поле индикации, если какого-то имени нет, удалите связь и создайте ее снова. Сохраните схему под тем же именем ЛР2_1.

3.2.7. Установите нужные микросхемы в колодки согласно правилу, приведенному выше, включите питание стенда и щелкните «Соединиться с устройством». Генератор G1 переведите в режим «2Гц» и запустите. Наблюдайте значения в поле индикации и на диаграмме до ее заполнения.

Остановите генератор, сдвиньте диаграмму влево так, чтобы в ее начале значения сигналов Х1, Х2, Х3 были нулевыми, проверьте совпадение диаграммы Y с заданной.

Если что-то не так, то проверьте правильность соединений согласно рекомендациям по поиску неисправностей или же правильность преобразований в ходе синтеза автомата. Сохраните исправленную схему.

КОНТРОЛЬНЫЕ ВОПРОСЫ

1. Как построить таблицу истинности цифрового автомата по временной диаграмме его функционирования?

2. Что отражает формула логической функции?

3. Дайте описание процедуры составления СДНФ и СКНФ логической функции и их минимизации.

4. По каким принципам выбирают элементную базу для реализации логической функции?

5. Изложите последовательность действий при синтезе цифрового автомата по заданной временной диаграмме.

6. Какие ошибки возможны при синтезе цифрового автомата по заданной временной диаграмме?

7. Как построить временную диаграмму по таблице истинности цифрового автомата?

ИССЛЕДОВАНИЕ ШИФРАТОРОВ

НА ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ

И СПЕЦИАЛЬНОЙ МИКРОСХЕМЕ

Лабораторная работа № 3

ЦЕЛЬ РАБОТЫ

1.1. Изучить принципы построения схем шифраторов.

1.2. На примере схемы трехразрядного шифратора получить практические навыки сборки и наладки макетных образцов функциональных узлов вычислительной техники.

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

Определение шифраторов

Шифраторами или кодерами называют разновидность преобразователей кодов, которые преобразуют комбинации (слова) унитарного кода в соответствующие слова какого-либо позиционного кода. Двоичные шифраторы – это комбинационные схемы, которые при подаче активного уровня на один из nинформационных входов выдают на выходе слово позиционного двоичного кода, значение которого соответствует номеру активного входа. При этом разрядность выходного слова a составляет

a = int (log2n) разрядов, (3.1)

где int означает округление в бóльшую сторону до целого числа.

Шифратор с n входами иногда называют шифратором n х a (например, 10х4). Графическое обозначение такого шифратора имеет вид, приведенный на рис. 3.1.

Шифратор с n входами иногда называют шифратором n х a (например, 10х4). Графическое обозначение такого шифратора имеет вид, приведенный на рис. 3.1.

Для удобства сопряжения с переключателями и т.п. периферийными устройствами схему шифраторов обычно организуют так, чтобы активным уровнем служил лог.0.

Как и другие преобразователи кодов, шифраторы могут быть аппаратно реализованы на логических элементах, на программируемой логике и на совокупности специальных микросхем.

2.2. Синтез двоичного шифратора на логических элементах

2.2. Синтез двоичного шифратора на логических элементах

Простота алгоритма преобразования делает шифратор удобным объектом для выработки навыков синтеза комбинационных схем. Построим шифратор с 7 входами и нулевым состоянием, управляемый низкими входными уровнями. Пример источника инверсного унитарного кода приведен на рис. 3.2. Здесь переключатель SA1 имеет заземленный обегающий контакт, а сигнальные линии  подтянуты к лог.1 с помощью набора резисторов *R.

подтянуты к лог.1 с помощью набора резисторов *R.

Выходной код этого шифратора согласно соотношению (3.1) будет состоять из int (log27) = 3 разрядов. По словесному описанию составим таблицу функционирования:

__ __ __ __ __ __ __

X1 X2 X3 X4 X5 X6 X7 А2 А1 А0 |=А10

1 1 1 1 1 1 1 0 0 0 | 0

0 1 1 1 1 1 1 0 0 1 | 1

1 0 1 1 1 1 1 0 1 0 | 2

1 1 0 1 1 1 1 0 1 1 | 3

1 1 1 0 1 1 1 1 0 0 | 4

1 1 1 1 0 1 1 1 0 1 | 5

1 1 1 1 1 0 1 1 1 0 | 6

1 1 1 1 1 1 0 1 1 1 | 7

В принципе существует несколько способов синтеза логических функций Аi (i = 0…2), соответствующих этой таблице.

А. В простейшем случае (факультативная шифрация) логические формулы функций могут иметь вид:

А0= X1vX3vX5vX7 =

А0= X1vX3vX5vX7 =

А1= X2vX3vX6vX7 =  (3.2)

(3.2)

А2= X4vX5vX6vX7 =

Такое решение дает минимальный объем аппаратных средств (по 0,5 корпуса микросхемы ЛА1 на каждый выход). Однако функции Аi определены в таблице истинности не на полном множестве комбинаций входных сигналов, т.е. факультативно. Проанализируем их значения при неунитарном наборе на входах (сигналы от произвольного набора источников). Полное возможное количество входных комбинаций составляет 27=128, то есть существует 120 комбинаций с неопределенностью. Рассмотрим, например, какой код будет на выходе, согласно (3.2), при X2&X4=1, или X3&X5=1, X1&X4 =1 и так далее. Полученные коды не соответствуют ни одному из номеров входов – устройство оказалось незащищенным от неправильного использования. Его следует применять только для шифрации положения переключателей с обегающим контактом и других подобных устройств, в которых одновременное появление активных уровней на нескольких входах кодера невозможно в принципе.

Б. Повторим исходную таблицу истинности в положительной логике:

X1 X2 X3 X4 X5 X6 X7 А2 А1 А0

0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 1

0 1 0 0 0 0 0 0 1 0

0 0 1 0 0 0 0 0 1 1

0 0 0 1 0 0 0 1 0 0

0 0 0 0 1 0 0 1 0 1

0 0 0 0 0 1 0 1 1 0

0 0 0 0 0 0 1 1 1 1

Исключить ложные коды можно, записав логические функции в классической СДНФ:

, (3.3)

, (3.3)

где  – логические произведения инверсий всех аргументов, кроме указанного в индексе (например,

– логические произведения инверсий всех аргументов, кроме указанного в индексе (например,

). А1 и А2 определяются аналогично. Оценка затрат аппаратных средств – 12,5 корпуса. Можно было бы записать Аi и в виде СКНФ: А0=(X1v(v

). А1 и А2 определяются аналогично. Оценка затрат аппаратных средств – 12,5 корпуса. Можно было бы записать Аi и в виде СКНФ: А0=(X1v(v  ))&(.......) и так далее, но не выпускается шестивходовых микросхем ИЛИ, поэтому аппаратная реализация будет еще более громоздкой. Результат такого пути синтеза формально точен – ложные коды при Xj&

))&(.......) и так далее, но не выпускается шестивходовых микросхем ИЛИ, поэтому аппаратная реализация будет еще более громоздкой. Результат такого пути синтеза формально точен – ложные коды при Xj&  = 1 отсутствуют, но с инженерной точки зрения потеря входных сигналов при их взаимном наложении зачастую недопустима.

= 1 отсутствуют, но с инженерной точки зрения потеря входных сигналов при их взаимном наложении зачастую недопустима.

В. На практике выбран третий путь синтеза – по приоритетной таблице функционирования. При этом чисто договорно задают, какой вход имеет приоритет над остальными (обычно вход с большим номером – над всеми входами с меньшими номерами). Тогда таблица функционирования будет иметь вид:

__ __ __ __ __ __ __

X1 X2 X3 X4 X5 X6 X7 А2 А1 А0

1 1 1 1 1 1 1 0 0 0

0 1 1 1 1 1 1 0 0 1

Ф 0 1 1 1 1 1 0 1 0

Ф Ф 0 1 1 1 1 0 1 1

Ф Ф Ф 0 1 1 1 1 0 0

Ф Ф Ф Ф 0 1 1 1 0 1

Ф Ф Ф Ф Ф 0 1 1 1 0

Ф Ф Ф Ф Ф Ф 0 1 1 1

Здесь знак Ф означает произвольное, несущественное для функционирования устройства значение аргумента. Видно, что в этом варианте нужно создавать вдвое меньше логических произведений (по 6-5-4..1-0 штук) и для А0, например, логическое уравнение будет иметь вид:

(3.4)

(3.4)

Соответствующие уравнения для А1 и А2 студентам следует составить самим. С точки зрения затрат это означает, что нужно 6 схем приоритета: одна с шестью входами, одна с пятью и т.д., т.е. схема остается громоздкой. Первый путь ее упрощения – использовать одни и те же конъюнкции многократно, т.е. построить схему последовательного логического умножения  с промежуточными отводами (нарисуйте такую схему шифратора). Затраты аппаратных средств составят 8 корпусов с резервом. Недостаток этого решения – разное время прохождения сигнала от Xi до Аj, т.е. наличие критических состязаний второго вида (ложные коды в момент установления нового значения). Второй путь – выявить в формулах Аj лишние вхождения аргументов: ведь если одновременно X1=1 и X5=1, то проход X1 на А0 блокировать уже не нужно и так далее. База такой минимизации – теорема разложения в инверсном виде (по /6/, формула 1.27):

с промежуточными отводами (нарисуйте такую схему шифратора). Затраты аппаратных средств составят 8 корпусов с резервом. Недостаток этого решения – разное время прохождения сигнала от Xi до Аj, т.е. наличие критических состязаний второго вида (ложные коды в момент установления нового значения). Второй путь – выявить в формулах Аj лишние вхождения аргументов: ведь если одновременно X1=1 и X5=1, то проход X1 на А0 блокировать уже не нужно и так далее. База такой минимизации – теорема разложения в инверсном виде (по /6/, формула 1.27):

Xpv f (Xn,...,  ,...,X1)=Xpv f (Xn,...,1,...,X1). (3.5)

,...,X1)=Xpv f (Xn,...,1,...,X1). (3.5)

В нашем случае  и так далее. Отсюда, последовательно применяя (3.5) к X7, X6, X5, получим

и так далее. Отсюда, последовательно применяя (3.5) к X7, X6, X5, получим

|

Соответствующая принципиальная схема приведена на рис. 3.3 (условный расход комплектующих составляет 5,25 корпуса).

Рис. 3.3

Схема выполняет заданную функцию и соответствует таблице функционирования, однако, во-первых, четырехвходовые микросхемы ИЛИ не выпускаются промышленностью, во-вторых, разное количество логических элементов между входом и выходом для разных аргументов ведет к критическим состязаниям второго вида (ложные коды низкоприоритетных входов в момент установления новой пары значений). Для получения работоспособной схемы студентам следует самостоятельно переработать схему, приведенную на рис. 3.3. Следует заменить схемы 4ИЛИ на 4НЕ-ИЛИ, ввести инверторы на выходы схем И, а также изменить длину путей от входов до выходов с помощью дополнительных инверторов так, чтобы инверсии высокоприоритетных сигналов приходили на выходную логику раньше, чем низкоприоритетные сигналы. Переработанную схему следует привести в отчете.

КОНТРОЛЬНЫЕ ВОПРОСЫ

1. Дайте описание процедуры составления СДНФ и СКНФ логической функции и их минимизации.

2. Приведите определение шифратора и двоичного шифратора.

3. Подсчитайте, сколько выходов будут иметь шифраторы с 10, 20, 30 входами.

4. Опишите различия в функционировании шифраторов, синтезированных способами А, Б и В, назовите причину этих различий, перечислите преимущества и недостатки каждого варианта.

5. Запишите СДНФ функций A1, A2 классической реализации рассмотренного шифратора.

6. Запишите выражения для функций A1, A2 приоритетной реализации рассмотренного шифратора.

7. Объясните принцип построения и функционирования переработанной вами схемы трехразрядного приоритетного шифратора, пользуясь получен