Создание и трансляция текстового файла.

Созданный проект дешифратора можно проверить с привлечением платы лабораторного стенда. На этой плате (см. описание стенда) имеется 8-разрядный переключатель, который мож-но использовать для задания входных сигналов, и 3-хразрядный 7-сегментный индикатор, один из разрядов которого может быть использован для отображения результатов. Эти устройства на плате подключены к определенным выводам ПЛИС EPF8282ALC84-4, поэтому в проекте необ-ходимо указать тип ПЛИС и соответствие номеров ее выводов входным и выходным линиям дешифратора.

Описать такой дешифратор на языке AHDL можно в виде таблицы истинности следую-щим образом:

TITLE "7-Digit Indicator Decoder";

SUBDESIGN decode7

(

di[3..0] : INPUT;

a, b, c, d, e, f, g : OUTPUT;

)

BEGIN

TABLE

!di[] => (a, b, c, d, e, f, g);

H"0" => B"1111110";

H"1" => B"0110000";

H"2" => B"1101101";

H"3" => B"1111001";

H"4" => B"0110011";

H"5" => B"1011011";

H"6" => B"1011111";

H"7" => B"1110000";

H"8" => B"1111111";

H"9" => B"1111011";

H"A" => B"1110111";

H"B" => B"0011111";

H"C" => B"1001110";

H"D" => B"0111101";

H"E" => B"1001111";

H"F" => B"1000111";

END TABLE;

END;

Справа в таблице указаны шестнадцатиричные значения кода на входных линиях, а слева - двоичные значения выходного кода на линиях, соответствующих определенному сегменту ин-дикатора. Инверсия входных сигналов в таблице обусловлена тем, что в положении переключа-теля«ON» (замкнутом) на соответствующий вход ПЛИС поступает сигнал логического «0» (см. описание стенда).

Для стенда с динамическим 3-хразрядным 7-сегментным индикатором управление инди-катором осуществляется через специальный модуль d_ind7.

Отладка с привлечением платы лабораторного стенда.

Для проверки функционирования разработанного дешифратора необходимо выполнить следующие действия (пункты 1-5 выполняются под наблюдением преподавателя).

1. Подключить к разъему платы кабель устройства ByteBtaster, который в свою очередь должен быть подключен к разъему LPT компьютера.

2. Подключить к разъему платы кабель блока питания +12В.

3. Включить источник питания - на плате должен загореться индикатор питания.

4. Выбрать в системе MAX+plusIIкоманду меню Assign | GlobalProjectDeviceOptionsи в открывшемся диалоговом окне в строке ConfigurationSchemeуказать PassiveSerial(выбрать из меню в соответствии с Рис. 4), после чего установить опции Reserveи Tri-Stateдля вывода Data0, и удалить эти опции для всех остальных выводов.

5. Вызвать приложение Programmer, при активном окне приложения щелкнуть по меню Options | HardwareSetupи установить для Hardware_Typeзначение ByteBlaster, ввести ОК. Инициировать процесс загрузки ПЛИС, щелкнув по кнопке Configureприложения Programmer.

5. Переключая тумблеры 1-4 8-разрядного переключателя, наблюдать отображаемые на левом 7-сегментном индикаторе шестнадцатиричные цифры. Проверить правильность работы дешифратора.

Анализ размещения схемы устройства на кристалле с использованием редактора конфигурации БИС.

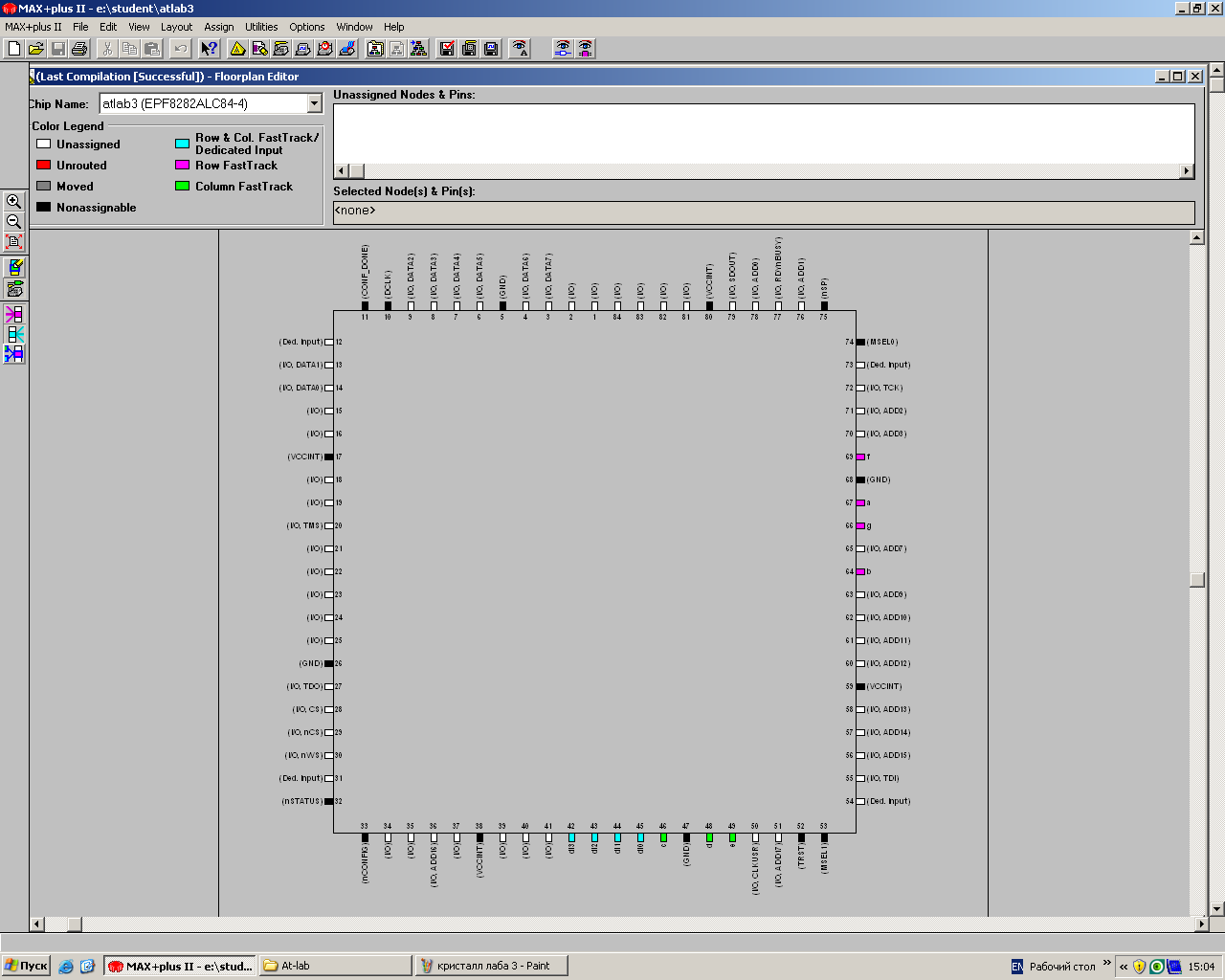

Вызвать редактор конфигурации можно командой меню Max+plusII | FloorplanEditorили щелчком по кнопке в панели инструментов. Откроется одно из двух вариантов изображения конфигурации ПЛИС (в данном случае типа EPF8282ALC84-4). Пусть это изображение типа DeviceView, приведенное на Рис. 5. На нем видно расположение всех выводов ПЛИС и назна-ченные им имена входных и выходных линий проекта. Переключить тип изображения конфигу-рации можно командой меню Layout| LabViewили Layout| DeviceView, или двойным щелчком мыши по изображению ПЛИС.

Рис. 1 Изображение конфигурации ПЛИС типа DeviceView

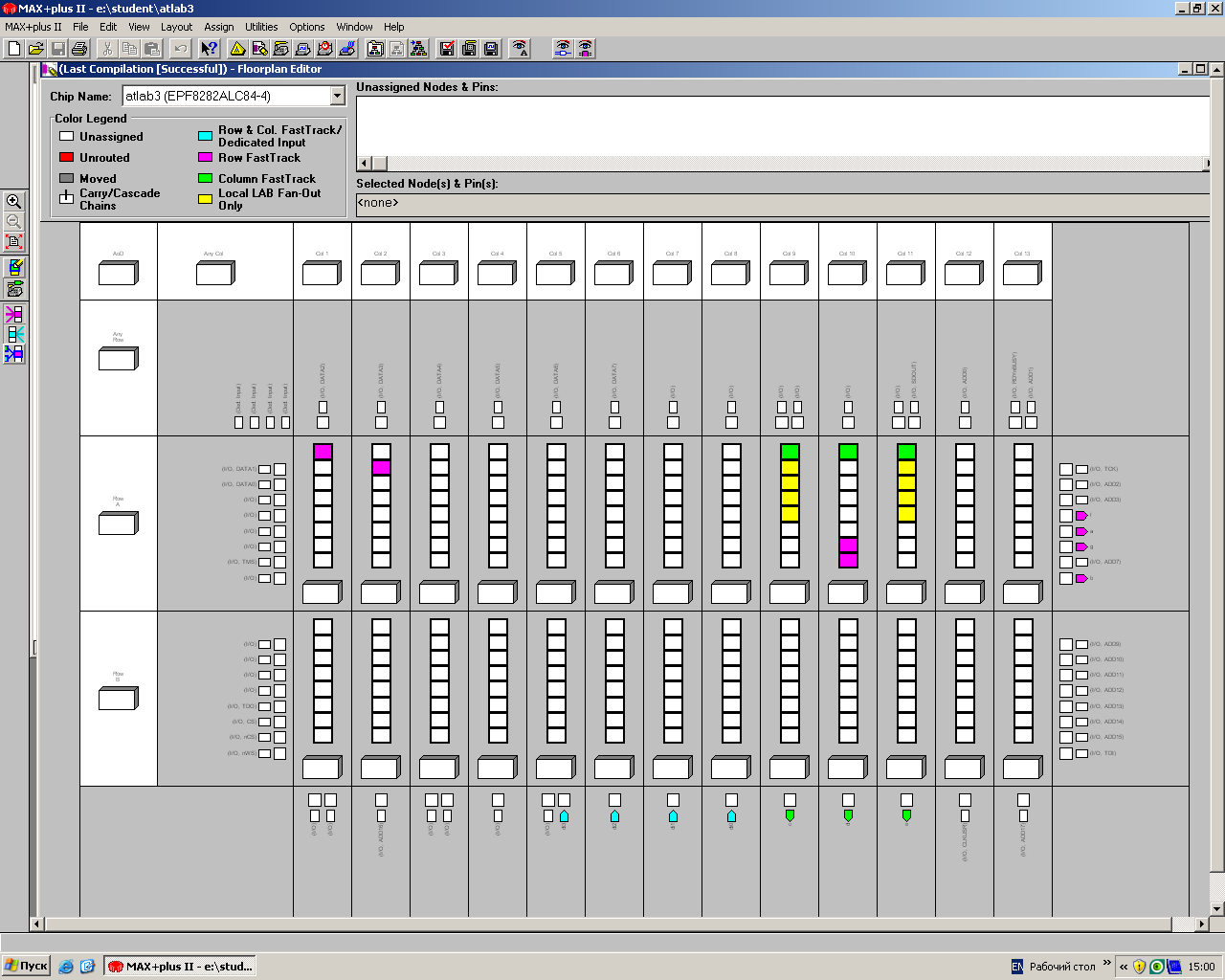

Изображение типа LAB View, приведено на Рис. 2.

Из рисунка видно, что при наведении указателя на вывод, рядом с указателем в рамке отображается имя линии проекта и номер вывода микросхемы. Редактор конфигурации позво-ляет получить информацию о связях отмеченных логических ячеек и выводов. Это делается следующим образом:

1. Выберем опцию ShowNodeFan-In("входные цепи") и/или опцию ShowNodeFan-Out("выходные цепи") в меню Option.

2. Установим режим LAB Viewи отметим одну или более логических ячеек или выво-дов.

Редактор отобразит входные и выходные цепи отмеченных элементов. На Рис. 6 отобра-жены связи третьей логической ячейки ряда А, столбца 2. Редактор конфигурации позволяет просматривать и изменять текущие назначения, которые хранятся в файле project'sAssigment&ConfigurationFile(.acf). После трансляции проекта можно вручную редактировать назначения, сделанные компилятором и хранящиеся в файле project'sFitFile(.fit). Для этого существует опция Back-AnnotateProjectв меню Assign, которая осуществляет копирование назначений из файла .fitв файл .acf.

Рис 2. Изображение конфигурации ПЛИС типа LAB View

Процесс корректировки назначений проекта с использованием редактора конфигурации следующий:

1. ВыберемкомандуменюAssign | Back-Annotate Project.

2. В открывшемся диалоговом окне включим опцию Chips, Logic Cells, Pins&DevicesразделаBack-Annotate to ACF. После ввода OK будет проведено копирование назначений из файла .fitв файл .acf.

3. ВведемкомандуменюLayout | Current Assignments Floorplan. Редактор конфигурации отобразит текущие назначения проекта.

4. Выберем опцию ShowNodeFan-In("входные цепи") и/или опцию Show Node Fan-Out ("выходныецепи") менюOption.

5. Введем команду поиска, выбрав пункт меню Utilities | FindText, в диалоговом окне выключим опцию Аllи включим опцию Pin&NodeNames. Укажем слово для поиска di0 и за-вершим ОК. В окне редактора конфигурации будет отмечен назначенный этому имени вывод и указаны его связи.

6. Введем команду меню Option | ShowMovedNodesinGray, которая отмечает серым цветом новые назначения.

7. Переведем редактор в режим просмотра текущих назначений, для чего нужно нажать на кнопку в левой вертикальной панели инструментов.

8. Наведем указатель мыши на отмеченный вывод линии di0 и при нажатой левой кнопке мыши «перетащим» назначение с вывода 45 на вывод 37. Аналогично переназначим линию di1 с вывода 44 на вывод 39, линию di2 с вывода 43 на вывод 40, линию di3 с вывода 42 на вывод 41. Новые назначения будут отмечены серым цветом.

9. Запустим перекомпиляцию проекта (Max+plusII | Compiler), убедившись, что отклю-чена опция Processing | Functional SNF Extractor, и включена опция Processing | Timing SNF Extractor.

10. После успешной перекомпиляции вернемся в окно редактора конфигурации и, вклю-чив опцию Layout | LastCompilationFloorplan, убедимся, что новые назначения выполнены. Эти назначения определяют в качестве формирователей входных векторов на плате тумблеры 5-8 (SW5-SW8) 8-разрядного переключателя, причем младший разряд (di0) задается переключателем 8, т.е. целью переназначения было установить общепринятый порядок, когда младший знача-щийбит находится справа.

11. ВведемкомандуменюAssign | Back-Annotate Project.

12. Загрузим файл проекта в ПЛИС на плате, вызвав окно программатора командой меню Max+plusII | Programmerи, переключая тумблеры 5-8 8-разрядного переключателя, проверим правильность работы дешифратора, наблюдая отображаемые на левом 7-сегментном индикаторе шестнадцатиричные цифры.