Реализация базовых логических операций.

Помимо рассмотренных основных арифметических действий ОПУ в любой ВМ реализуются операции логические («И», «ИЛИ», «НЕ», «исключающее ИЛИ») и сдвига. Чаще всего, эти операции реализуются дополнительными схемами, входящими в состав целочисленных ОПУ.

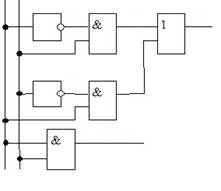

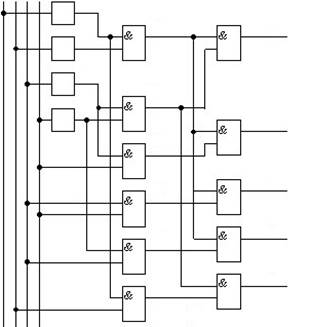

На практике логические операции в ОПУ выполняются сразу над совокупностью логических переменных, объединенных в один байт или слово. Причем над всеми битами выполняется одна логическая операция. Возможная структура подобного ОПБ представлена на Рисунок 3. Выбор нужной операции (одной из четырех) осуществляется бинарным управляющим кодом на входах дешифратора.

Рисунок 3 - Структура ОПБ для выполнения логических операций.

Практическая часть

Для построения схемы АЛУ потребуется знание стандарта ГОСТ 2.743-91 «ОБОЗНАЧЕНИЯ УСЛОВНЫЕ ГРАФИЧЕСКИЕ В СХЕМАХ. ЭЛЕМЕНТЫ ЦИФРОВОЙ ТЕХНИКИ», введенного 01.01.93.

Настоящий стандарт устанавливает общие правила построения условных графических обозначений (УГО) элементов цифровой техники в схемах, выполняемых вручную или с помощью печатающих и графических устройств вывода ЭВМ во всех отраслях промышленности. Ниже приведены основные положения и примеры УГО элементов, которые потребуются для построения АЛУ.

Возможные варианты элементов для реализации АЛУ

Использование вышеупомянутого ГОСТ и следующего описания элементов поможет реализовать схему АЛУ.

Регистр хранения информации

Рисунок 4-Функциональная схема регистра хранения информации

В качестве регистра хранения информации можно использовать восьмиразрядный регистр 74HC373.

Таблица состояний микросхемы 74HC373

| Входы | Выходы | ||

| OE | LE | Dn | On |

| X | X | Z | |

| X | Oo |

· 0 - низкий уровень

· 1 - высокий уровень

· Z - высокоимпедансное состояние

· X - любое состояние

· Oo - предыдущее состояние выхода

Рисунок 5 – Условное графическое обозначение регистра 74HC373

Сумматор

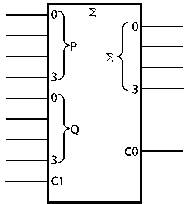

Рисунок 6 – Функциональная схема микросхемы 74HC283

В качестве сумматора можно использовать микросхему 74HC283, который представляет собой четырехзначный двоичный сумматор с ускоренным переносом.

Таблица состояний микросхемы 74HC283

| Входы | Выходы | |||

| Ai | Bi | C0 | C1 | Si |

Рисунок 7 – Условное графическое обозначение микросхемы 74HC283

Компаратор

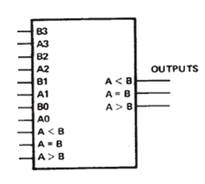

Рисунок 8- Функциональная схема регистра 7485

Для сравнения чисел в качестве компаратора можно использовать микросхему 7485 (4-хразрядный компаратор).

Таблица состояний регистра 7485

| Входы | Выходы | |||

| x | y | FA=B | FA>B | FA<B |

Рисунок 9 – Условное графическое обозначение микросхемы 7485

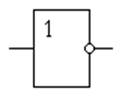

Инвертор

Рисунок 10- УГО инвертора.

В качестве инвертора можно использовать микросхему 74ALS которая осуществляет преобразование логической единицы в логический ноль и наоборот.

Таблица состояний логического элемента 74ALS

| Вход | Выход |

| x | y |

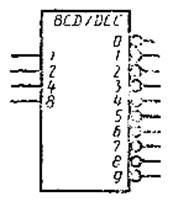

Дешифратор

Рисунок 11 – Функциональная схема микросхемы 74HC138

В качестве дешифратора в управленческой части можно использовать дешифратор 74HC138.

Таблица состояний микросхемы 74HC138

| №входного набора | Входы | Выходы | |||||||||

| X3 | X2 | X1 | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | |

Рисунок 12 – Условное графическое обозначение микросхемы 74HC138

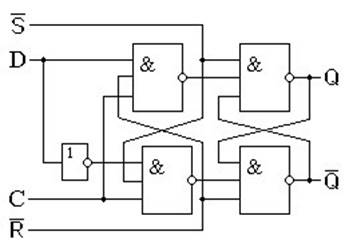

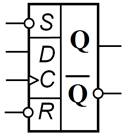

Триггер

Рисунок 13 – Функциональная схема микросхемы CD4013B

В качестве триггера можно использовать микросхему CD4013B, которая является двухступенчатым D – триггером flip-flop.

Таблица состояний D– триггера

| Режим работы | Входы | Выходы | ||||

| Асинхронный | Синхронный | |||||

| S | R | C | D | Q | Q | |

| Асинхронная установка 1 | x | x | ||||

| Асинхронная установка 0 | x | x | ||||

| Запрещенное состояние | x | x | ||||

| Установка 1 | ↑ | |||||

| Установка 0 | ↑ |

Рисунок 14 – Условное графическое обозначение микросхемы CD4013B

Логический элемент И

Рисунок 15 – Условное графического обозначение логического элемента И

В качестве этого элемента можно использовать микросхему 74HC08. При подаче напряжения низкого уровня на один или оба входа каждого элемента на выходе микросхемы 74HC08 устанавливается напряжение низкого уровня. Если на оба входа подается напряжение высокого уровня, то на выходе формируется напряжение высокого уровня.

Таблица истинности микросхемы 74HC08

| Входы | Выходы | |

| A | B | Y |